Abstract

A new kind of metamutator, namely “Current Inverting Metamutator”, its realizations using different types of active blocks and some of its applications like voltage-mode universal biquadratic filter with three input and one output terminals are presented. The proposed circuits can realize all standard filters, namely, low-pass, band-pass, high-pass, notch and all-pass without passive component matching conditions. The proposed circuit offers the features of using grounded capacitors and orthogonal controllability of angular frequency and quality factor. Then a novel realization of metamutator with one active device, additive and differential IC (AD-IC) is proposed and implemented with twelve transistors only. The metamutator with AD-IC has the advantages: (1) of creating new realizations of memristors, capacitance multipliers, inductor simulators, frequency dependent negative resistors which can be used to make IC active filters, (2) less is the number (only one) of active devices, less is the amount of disparity, (3) no need to match passive component values.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In 1971 memristor and a 2-port mutator, with a very complex circuit structure, for transforming nonlinear circuit elements to memristor was introduced in [1]. Recently different circuit structures for 2-port mutators have been introduced for obtaining Memstors (a generic name covering memristors, meminductors, memcapacitors) from nonlinear resistors or, converting one type of memstor to another [1,2,3,4,5,6,7].

The idea of a new class of multifunctional 4-ports was first introduced in [8] and then named metamutator, because of its ability of transforming many kinds of circuit elements to each other among other applications. These 4-port metamutators can be used for realizing mutators, quadrature oscillators, inverters, trans-admittance, trans-impedance amplifiers and gyrators by properly terminating some of its ports. Different kinds of circuit structures for metamutators have been introduced in [8,9,10,11,12]. Because of the port description matrix (1) and the negative sign in the voltage relation of two of its ports, it was named as Voltage Inverting Metamutator (VIM).

Recently, different kinds of filters and multifunctional filters with diverse realizations have been introduced by several researchers and manufacturers [13,14,15,16]. Universal filters are able to realize different types of filters low-pass (LP), high-pass (HP), band-pass (BP), band-stop (BS) and all-pass (AP) simultaneously. They are widely used in electronic measurements, communications and neural networks. The voltage-mode active filters with high input impedance are useful because by cascading several filters of this type, higher order filters can be realized [24, 25].

According to the number of input and output ports, filters can be classified into three categories: (1) single-input, multiple-output (SIMO) [26, 27], (2) multiple-input, single-output (MISO) [28] and (3) multiple-input, multiple-output (MIMO) type [29]. Similarly different realizations of a variety of impedance simulators, gyrators, frequency dependent negative resistors (FDNR) simulators are being considered by several companies and authors [17,18,19,20,21]. In [19] a FDNR simulator with two DO-CCIIs, three resistors and one capacitor, in [20, 23] a FDNR using two current backward transconductance amplifiers (CBTAs) and several passive components is presented. A FDNR simulator with two voltage differencing current conveyors (VDCCs), a single grounded resistor and two grounded capacitors is proposed in [22]. With two or more active devices in their structure, most of these circuits necessitate component matching. Also, because of many active devices present, existing parasitic elements and non-ideal gain effects create severe problems; less number of active devices causes less amount of disparity.

With the first part of the paper the newly introduced metamutator, named as current inverting metamutator (CIM) due to its port description matrix (2) and the negative sign in the current relation of two of its ports, is being presented in Sect. 2. Three CIM circuit realizations will be offered in Sect. 3. Application of CIM as universal filter is proposed in Sect. 4 with its simulation results in Sect. 5.

In the second part of the paper a new metamutator circuit with only one new active device, additive and differential-integrated circuit (AD-IC) realized only with twelve transistors, will be proposed; its port description matrix and circuit structure with twelve transistors using TSMC 0.25 µm CMOS process parameters will be given in Sect. 6. Theoretical analysis of the inductor simulator, capacitance multiplier, and FDNR will be presented in Sect. 7. The layout, the post-layout simulation results obtained using TSMC 0.25 µm process parameters with ± 1.25 V supplies confirming the claimed applications, including memristor’s signature, will be exhibited in Sect. 8. In the circuits introduced here, as only one active device and few passive components are being used, there is no need of matching components and functionality. Finally, Sect. 9 will conclude the paper.

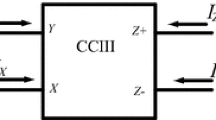

2 VIM and CIM

The 4-port block diagrams of VIM and CIM are shown in Figs. 1 and 2 and their port descriptions are defined via the equalities (1) and (2) respectively. Although identity matrix shows in both expressions in VIM a port voltage is being inverted whereas, in CIM a port current is inverted. As care must be exercised in the implementation phase as to which variable follows the other in (1) and (2), variables have been indexed with letters k, l, m, n taking different values from the set {1, 2, 3, 4} as required by the application.

3 Proposed realizations of CIM

3.1 Realization with one CFOA and one CCII+

In this section, three new CIM structures using two off the shelf active devices are being proposed. The circuit structure of the first one for l = 1, n = 2, k = 3, m = 4 is shown in Fig. 3, using one current feedback operational amplifier (CFOA) and one second-generation plus type current conveyor (CCII+) are being employed, which are defined respectively by (3) and (4).

After some algebraic manipulations using KCL and KVL the port relation matrix describing the circuit in Fig. 3 becomes as given with expression (2).

3.2 Realization with two DOCCIIs

As shown in Fig. 4, the second CIM is designed by using two dual output second generation current conveyors (DOCCII) with port definition matrix shown in (5). The structure of this metamutator is extracted from [4].

After some algebraic manipulations the port relation matrix between currents and voltages of the circuit in Fig. 4 becomes as given with expression (2) thus identifying a CIM.

3.3 Realization with two CFOAs

The third CIM is designed using two CFOA defined by (3), as shown in Fig. 5. It can easily be verified that the 4-port satisfies the CIM port description as given by (2).

4 Application of CIM as universal filter

In [30,31,32,33,34,35,36,37,38] several multi input VM universal biquadratic filters were introduced and different kinds of filters can be realized by properly selections of input voltage terminals in these circuits. However, these circuits suffer from one or more of the following problems:

-

1.

In [33, 34, 36,37,38] the necessity of passive component matching conditions,

-

2.

In [30,31,32, 35] lack of orthogonal controllability of the resonance angular frequency (ω0) and quality factor (Q),

- 3.

Application of CIM as a voltage mode (VM) universal filter is presented in this section. As an example, the CIM circuit with one CFOA and one CCII+ is selected. Using Table 1 to connect properly elements to ports of CIM in Fig. 3, different realizations of a multifunctional filter will be obtained. For example, applying realization #1 the circuit will become as shown in Fig. 6.

From (2) v2 = v3 and selecting the output as \(v_{3} = v_{\text{out}}\), KCL at port 2 of the circuit in Fig. 6 gives:

Using i1 = i2, v4 = v1 from (2), \(i_{1} = - \,\frac{{v_{1} }}{{R_{3} }}\), and \(V_{4} = - \,\frac{1}{{sC_{2} }}I_{4}\) in (6), gives:

then using i3 = − i4 and \(I_{3} = \left( {V_{S3} - V_{\text{out}} } \right)/R_{2}\) in (7) gives

Solving for \(V_{\text{out}}\) in terms of VS1, VS2 and VS3 from (8) the output of the multifunctional filter is found as shown by (9), with the selection of different voltage sources resulting in different filter functions as shown in Table 2:

So, the proposed CIM circuit can realize all filter functions with no requirements for matching conditions. The angular resonance frequency (ω0) and the quality factor (Q) of all filter responses, given in Table 2, are:

As shown by (10) and (11), the angular frequency can be controlled by R2 and/or R3 and the quality factor can be independently controlled by R1. So the angular frequency and quality factor are orthogonally controllable. In the case of C1 = C2 = C and R1 = R2 = R3 = R the angular frequency becomes \(\omega_{0} = \frac{1}{RC}\) and the quality factor is Q = 1. All of the filters have non-inverting unity gain and these results are also valid for other CIM circuits introduced in Sect. 3.

Taking into consideration of CIM non-idealities the port description matrix of CIM becomes,

where αj and βj are current and voltage frequency dependent non-ideal gains respectively and are equal to unity ideally. Furthermore,

in which ɛij and ɛvj are current and voltage tracking error coefficients with values close to zero. The non-ideal angular frequency ω0, quality factor Q and bandwidth for all types of filters are obtained as,

Sensitivities of this filter, derived from (13) to (15), are:

The absolute values of all passive and active element sensitivities are low and not larger than unity.

5 Simulation results of the universal filter

The simulation results of different types of filters shown in Fig. 6 are shown in Figs. 9 and 10. An AC voltage source with amplitude of 1 V is chosen for all of the voltage sources. For the characteristic frequency \(f_{0} = \omega_{0} /2\pi \cong 6.36\;{\text{MHz}}\) and the quality factor of filters Q = 1, the passive component values have been chosen as \(C_{1} = C_{2} = 25\;{\text{pF}},R_{1} = R_{2} = R_{3} = 1\;{\text{k}}\Omega\). For CFOA and CCII, 0.13 µm CMOS technology parameters have been used. The transistor level circuits are shown in Figs. 7 and 8, parameters being given in Tables 3 and 4 respectively; supply voltages are selected as ± 0.75 V, VB = 0.24 V.

Transistor level circuit of CFOA [22]

Transistor level circuit of CCII [22]

The transfer functions and simulation results of different types of filters are collected in Table 5 and Fig. 9, those of all-pass being in Fig. 10.

Simulation results for high-pass, low-pass, band-pass and band-stop filters in Fig. 6

Phase and gain of all-pass filter in Fig. 6

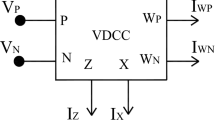

6 Metamutator with single active device AD-IC

The first metamutator was built using two separate adder and subtractor ICs in [8]. In this section a single 4-port IC named additive and differential IC (AD-IC) built only with twelve transistors will be proposed. The block diagram and port description matrix of AD-IC are shown in Figs. 11 and 19 respectively.

The 4-port metamutator can be constructed by properly interconnecting terminals of AD-IC as shown in Fig. 12. The port description matrix of this metamutator is the same as in (1) making it a VIM type metamutator, and the Table 4 in [8] illustrating several applications stands also true for this configuration.

In the realization of AD-IC, TSMC 0.25 µm CMOS process parameters were used, with transistor dimensions as shown in Table 6 and its circuit in Fig. 13. The developed CMOS layout of AD-IC is given in Fig. 16.

7 Applications of metamutator with AD-IC

Many applications of metamutator were given in [8,9,10,11,12]. In this section three new applications: inductor simulator, capacitance multiplier and FDNR Simulator are being proposed using the metamutator built with AD-IC. The general structure of the configuration using the AD-IC metamutator with port impedances is shown in Fig. 14.

By connecting impedances to three of the ports, the impedance seen from the remaining 4th port is depicted in Table 7. When reading column i of Table 7 it should be understood that no element is connected to port i whereas impedances Zj are connected to port j for j ≠ i and i = 1, 2, 3, 4.

Figure 14 illustrates the case i = 1. An interesting conclusion that can be deduced from Table 7 is that the metamutator allows the realization of grounded elements as well as floating ones. The simulation results of all applications will be given in the next section.

7.1 Application as inductor simulator

As coil realization of inductors on an integrated chip is highly undesirable many inductor simulator circuits have been proposed in the literature [39, 40]. In this section an application of metamutator as inductance simulator with minimum number of elements, AD-IC with 12 transistors, two resistors and single capacitor, is presented. According to Table 7 by connecting one capacitor and two resistors to three of the ports properly, an inductor will be achieved at the fourth port and the value of the inductance is equal to the product of the values of capacitor and resistors. The different realizations are shown in Table 8.

7.2 Application as capacitance multiplier

According to Table 7 by replacing one capacitor and two resistors (or three capacitors) in three of the ports, a capacitor will be achieved at the fourth port for which the value of the so obtained capacitance is the value of the capacitor multiplied by the ratio of resistance (capacitance) values. Possible realizations are shown in Table 9.

7.3 Application as FDNR simulator

Low-pass filters have wide usage in radio frequency (RF) transceivers; in this process the much-used low-pass filter is called an anti-aliasing filter. By reducing the size and refining the performance of these filters, new improvements in communication are achieved. Figure 15 shows the position of the anti-aliasing filter in fully digital receivers.

Schematic of fully digital receiver [24]

As in general anti-aliasing filters (AAF) are third or higher order passive LC ladder filters using an inductor in these circuits requires a lot of space and reduces the performance. In order to reduce the size and improve the performance one can use the complex impedance scaling technique for designing a prototype of the LC ladder circuits. This technique, treated extensively by Bruton [41], is based on the fact that the filter transfer function will remain unchanged if the impedance of each element is divided by s. So the Inductor will be transformed into a resistor, the resistor will be transformed into a capacitor and the capacitor will be transformed into a FDNR.

By connecting two capacitors and one resistor to three of the ports, as detailed in Table 7, a grounded or floating FDNR will be achieved at the fourth port. The value of the FDNR and different realizations are shown in Table 10. It should be observed again that only twelve transistors and three passive elements are being used with no component matching requirements.

8 Simulation results

The layout of the AD-IC circuit is shown in Fig. 16. The area of the AD-IC is approximately 60 × 22 µm2. Post-layout simulations are performed using the netlist extracted from the layout with TSMC 0.25 µm process parameters. The supply voltage is taken as ± 1.25 V and VB as 0.8 V. For increasing the dynamic range of the AD-IC circuits all NMOS transistors’ substrates are connected to VSS terminal. The dimensions of the transistors used for the circuit are given in Table 6. The equivalent parasitic capacitances CL at the output ports are approximately 73 fF. For the purpose of providing a smaller output resistance the W/L ratios of the output node transistors M3, M4, M11 and M12 in Table 6 are chosen much bigger than the ratio of other transistors.

8.1 Memristor realization

The port description matrix of metamutator with single active device AD-IC is the same as the port description matrix of metamutators with two active devices. In this case all applications obtained so far, can also be achieved by the AD-IC metamutator, as all the results are based on the port relationship given either by the expressions (1) or (2). For example, in case of terminating the ports 1, 2 and 3 by a capacitor, a nonlinear resistor and an inductor respectively, a grounded memristor will be achieved at the 4th port [8].

By applying a sinusoidal voltage source with amplitude of 2.5 V and frequency of 22 Hz at port 4 of the metamutator in Fig. 17, the current versus voltage and voltage versus current characteristics are obtained as shown in Fig. 18. For the nonlinear resistor the model introduced in [10] is being used. The supply voltages are chosen as ± 1.25 V and \(V_{\text{B}}\) as 0.5 V. The capacitor and inductor values were selected as 1 nF and 1 mH, respectively. The Lissajous curves show the signature of memristor at port 4.

8.2 Capacitance multiplier realization

According to Table 9 and applying realization #3 to the metamutator with AD-IC and connecting \(C_{3}\), R1 and R4 to three of the ports of the metamutator, a capacitor with the value of KC3 will be obtained at the second port with K = R4/R1. Moreover, the functionality and frequency response plots of the multiplied capacitor and that of an ideal capacitor are given in Fig. 19 for case #3 with R1 = 1 kΩ, R4 = 20 kΩ and C4 = 5 pF, which yields the multiplied capacitance value of 100 pF.

In this case the metamutator was simulated using an AC voltage source with amplitude 0.3 V; for AD-IC, TSMC, 0.25 µm CMOS process parameters were used with transistor dimensions as shown in Table 6 and the circuit in Fig. 13. The supply voltages were chosen as ± 1.25 V and \(V_{\text{B}}\) as 0.8 V.

8.3 Inductor simulator realization

According to Table 8 and applying realization #2 to the metamutator with AD-IC and replacing C4, R1 and R3 in three of the ports of the metamutator, an inductor will be obtained in the second port; Furthermore, the performance of the proposed inductance, the frequency response plots of the newly designed and ideal inductor are both given in Fig. 20 for R1 = R3 = 1 kΩ and C4 = 25 pF, which corresponds to an inductance of 25 µH.

In this case the metamutator was simulated using an AC current source with amplitude of 1 mA. For AD-IC TSMC, 0.25 µm CMOS process parameters were used with transistor dimensions as shown in Table 6 and its circuit in Fig. 13. Supply voltages are chosen as ± 1.25 V, \(V_{\text{B}}\) = 0.8 V.

8.4 FDNR simulator realization

Applying realization #4 to the metamutator with AD-IC as given in Table 10 and connecting C1, R2 and C3 to ports 1, 2 and 3 of the metamutator respectively, a FDNR will be observed from port 4. The simulation results are demonstrated in Fig. 21.

The metamutator with AD-IC was simulated using an AC voltage source with amplitude of 1 V. For AD-IC, TSMC 0.25 µm CMOS process parameters were used, with transistor dimensions as shown in Table 10 and its circuit in Fig. 13. The supply voltages are chosen as ± 1.25 V, \(V_{\text{B}}\) as 0.8 V. The values of C1, C3 and R2 were selected as 0.1 nF, 0.2 nF and 100 kΩ, respectively.

9 Conclusion

It has been shown that metamutators, recently introduced 4-ports in [8, 12], can be classified into two categories as: voltage inverting VIM and current inverting CIM (presented in this paper). CIM is also capable to implement a variety of elements/systems like VIM and it has been given three IC realizations using two different IC devices. One of these new realizations has been applied to the simulation of a memristor by properly terminating three of the ports and verifying the memristor’s signature.

Several new configurations, with properly terminated CIM ports, have been shown to be able to generate Universal Filters, a new application among many others presented in [8, 12]. All five filter types, band-, low-, high-, all-pass and band notch have been simulated with TSMC 0.13 µm parameters for one configuration and they have exhibited excellent frequency response.

Using AD-IC, introduced in this paper, as the only single active device and no passive elements, the metamutator has been given a new realization which was applied to capacitance scaling, memristor/inductor simulations and FDNR realization. Depending on the choice of the input port, these realizations can be made grounded or floating. All four applications have been simulated with TSMC 0.25 µm CMOS process parameters and shown to be in very good agreement with theoretical results.

Future work will concentrate on the comparison of VIM versus CIM, novel types of metamutators, their different realizations, tuning external elements to improve the behavior of these applications and further applications like linear oscillators, operational amplifiers etc. Filter building with FDNRs realized here and comparing the effect of using different kind of metamutators in the design of these filters will deserve special consideration. In another direction use of metamutators in nonlinear applications such as rectifiers, modulators will be looked upon.

Change history

03 September 2019

Voltage Inverting Metamutator (VIM) and Current.

03 September 2019

Voltage Inverting Metamutator (VIM) and Current.

References

Chua, L. O. (1971). Memristor—The missing circuit element. IEEE Transaction on Circuit Theory, 18, 507–519.

Sah, M Pd, Budhathoki, R. K., Yang, C., & Kim, H. (2014). Mutator-based meminductor emulator for circuit applications. Circuits, Systems and Signal Processing, 33, 2363–2383.

Sheng, Y. D., Yan, L., Lu, H. H. C., & Hua, H. Y. (2014). Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chinese Physics B, 23, 070702.

Pershin, Y. V., & Di Ventra, M. (2011). Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47(4), 243–244.

Biolek, D., Biolková, V., & Kolka, Z. (2010). Mutators simulating memcapacitors and meminductors. In Proceedings of the Asia Pacific conference on circuits and systems (pp. 800–803), Malaysia.

Biolek, D., & Biolkova, V. (2010). Mutator for transforming memristor into memcapacitor. Electronics Letters, 46, 1428–1429.

Yu, D., Liang, Y., Lu, H. H. C., & Chua, L. O. (2014). A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Transaction on Circuits and Systems II, 61, 758–762.

Minaei, S., Göknar, I. C., Yıldız, M., & Yuce, E. (2014). Memstor, memstance simulations via a versatile 4-port built with new adder and subtractor circuits. International Journal of Electronics, 102, 911–931.

Minayi, E. (2014). Applications of 4-port generalized mutators to memstor simulations. M. Sc: Thesis, Dogus University.

Göknar, I. C., & Minayi, E. (2014). Realizations of mutative 4-ports and their applications to memstor simulations. Analog Integrated Circuits and Signal Processing, 81, 29–42.

Göknar, I. C., Yıldız, M., & Minaei, S. (2016). Metamutator applications: a quadrature MOS only oscillator and transconductance, transimpedance amplifiers. Analog Integrated Circuits and Signal Processing, 89, 801–808.

Minayi, E., Göknar, I. C. (2017). CIM a current inverting metamutator and its application to universal filters among others. In Proceedings of the 40th international conference on telecommunications and signal processing, July 5–7, 2017, Barcelona, Spain.

Pini, A. Use monolithic universal active filter ICs to speed IoT analog front-end design. Digi-Key Electronics, Article Library, Nov. 15, 2017. Retrieved June 1, 2018 from https://www.digikey.sg/en/articles/techzone/2017/nov/use-monolithic-universal-active-filter-ics-to-speed-iotanalog-front-end-design.

Jin, J., & Wang, C. H. (2014). Current-mode universal filter and quadrature oscillator using CDTAs. Turkish Journal of Electrical Engineering & Computer Sciences, 22, 276–286.

Kaçar, F., & Yeşil, A. (2010). Voltage mode universal filters employing single FDCCII. Analog Integrated Circuits and Signal Processing, 63, 137–142.

Liu, S.-I., & Lee, J.-L. (1997). Voltage-mode universal filters using two current conveyors. International Journal of Electronics, 82, 145–150.

Yüce, E., Minaei, S., & Cicekoglu, O. (2006). Novel floating inductance and FDNR simulators employing CCII+s. Journal of Circuits, Systems and Computers, 15, 75–81.

Kacar, F., & Kuntman, H. (2009). Novel electronically tunable FDNR simulator employing single FDCCII. In European conference on circuit theory and design, Antalya, Turkey (pp. 21–24).

Minaei, S., Yuce, E., Cicekoglu, O., & Özcan, S. (2005). Inductance and FDNR simulator employing only two CCII+. In Applied electronics conference, Pilsen, Czech Republic (pp. 227–231).

Ayten, U. E., Sagbas, M., Herencsar, N., & Koton, J. (2011). Novel floating FDNR, inductor and capacitor simulator using CBTA. In 34th International conference on telecommunications and signal processing (TSP), Budapest, Hungary (pp. 312–316).

Prasad, D., & Srivastav, M. (2017). Novel Ms⁁2 type FDNR simulation configuration with electronic control and grounded capacitances. In IEEE International conference on electronics, circuits and systems, Batumi, Georgia (pp. 160–164).

Surakampontorn, W., Riewruja, V., Kumwachara, K., & Dejhan, K. (1991). Accurate CMOS based current conveyors. IEEE Transactions on Instrumentation and Measurement, 40, 699–702.

Minayi, E., & Göknar, I. C. (2017). Single active device metamutator; Its application to impedance simulation and in particular to FDNR. In International conference on electrical and electronics engineering, Bursa, Turkey (pp. 497–502).

Monsurrò, P., & Trifiletti, A. (2016). Synthesis of anti-aliasing filters for IF receivers. In International conference on mixed design of integrated circuits and systems, Lodz, Poland (pp. 239–242).

Fabre, A., Dayoub, F., Duruisseau, L., & Kamoun, M. (1994). High inputimpedance insensitive second-order filters implemented from currentconveyors. IEEE Transactions on Circuits and Systems I, 41, 918–921.

Horng, J.-W. (2002). Voltage-mode universal biquadratic filter with one input and five outputs using OTAs. International Journal of Electronics, 89, 729–737.

Minaei, S., Yuce, E., Herencsar, N., & Koton, J. (2012). SIFO voltage-mode universal filters employing TO-CCIIs. In International conference on telecommunications and signal processing, Prague, Czech Republic (pp. 359–362).

Horng, J.-W., Chan, T. H., & Li, T. Y. (2015). Tunable voltage-mode four inputs universal biquad using three DVCCs. In IEEE international conference on ASIC, Chengdu, China (pp. 1–4).

Paul, S. K., & Kushwaha, A. K. (2016). Biquadratic universal filter based on CCDDCCTA. In International conference on microelectronics, computing and communications, Durgapur, India (pp. 1–4).

Chen, H. P., & Yang, W. S. (2008). High-input and low-output impedance voltage-mode universal DDCC and FDCCII filter. IEICE Transactions on Electronics, 91(C), 666–669.

Horng, J. W. (2008). High input impedance voltage-mode universal biquadratic filter with three inputs using DDCCs. Circuits, Systems, and Signal Processing, 27, 553–562.

Chen, H. P. (2010). Versatile multifunction universal voltage-mode biquadratic filter. AEU International Journal of Electronics and Communications, 64, 983–987.

Minaei, S., & Yuce, E. (2010). All-grounded passive elements voltage-mode DVCC-based universal filters. Circuits, Systems, and Signal Processing, 29, 295–309.

Nikoloudis, S., & Psychalinos, C. (2010). Multiple input single output universal biquad filter with current feedback operational amplifiers. Circuits, Systems, and Signal Processing, 29, 1167–1180.

Lee, C. N. (2011). Fully cascadable mixed-mode universal filter biquad using DDCCs and grounded passive components. Journal of Circuits, Systems, and Computers, 20, 607–620.

Topaloglu, S., Sagbas, M., & Anday, F. (2012). Three-input single-output second-order filters using current-feedback amplifiers. AEU International Journal of Electronics and Communications, 66, 683–686.

Horng, J. W., Hsu, C. H., & Tseng, C. Y. (2012). High input impedance voltage-mode universal biquadratic filters with three inputs using three CCs and grounding capacitors. Radioengineering, 21, 290–296.

Horng, J. W., Chiu, T. Y., & Jhao, Z. Y. (2012). Tunable versatile high input impedance voltage-mode universal biquadratic filter based on DDCCs. Radioengineering, 21, 1260–1268.

Ibrahim, M. A., Minaei, S., Yuce, E., Herencsar, N., & Koton, J. (2012). Lossy/lossless floating/grounded inductance simulation using one DDCC. Radioengineering, 21, 3–10.

Kacar, F. (2010). New lossless inductance simulators realization using a minimum active and passive components. Microelectronics Journal, 41, 109–113.

Bruton, L. T. (1980). RC-active circuits: Theory and design. Englewood Cliffs, NJ: Prentice-Hall.

Acknowledgements

The authors sincerely thank all the reviewers and Prof. Shahram Minaei for their invaluable comments, their time and their efforts for improving the manuscript.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Minayi, E., Göknar, I.C. Current inverting metamutator, its implementation with a new single active device and applications. Analog Integr Circ Sig Process 97, 15–25 (2018). https://doi.org/10.1007/s10470-018-1239-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1239-9