Abstract

This paper intends to provide a three-level CUK converter-based on-board electrical vehicle battery charger with improved power quality features. The proposed configuration includes a diode bridge rectifier followed by a DC–DC converter suitable for the universal input voltage variations (85–265 V). It offers reduced voltage stress across the switches, reduced filter size, high efficiency, and improved dynamic response. A feed-forward control scheme is implemented for the proper functioning of the proposed converter under constant current (CC) and constant voltage (CV) modes of operation. In this paper, the mathematical modeling, operational details, and components design of the PFC converter are analyzed in continuous current mode. The simulation study on a 3.2 kW, 400 V proposed converter is carried out with MATLAB Simulink toolbox, and a real-time implementation of the same specifications of the proposed system is developed to verify the simulation study. The steady-state and dynamic behavior of the converter is investigated for power quality features like total harmonics distortion and input power factor with resistive and battery loads. The onboard charger exhibits satisfactory operation in CC and CV modes to a wide range of supply voltage variations.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Keeping in view of global warming and usages of fossil fuel, there is growing interest of car manufacturers, consumers, and researchers towards the electric vehicles (EVs)/plug-in electric vehicles (PHEVs) [1, 2]. According to battery charger location, type of usages, and power level, the battery chargers are classified as on-board chargers (level-1, level-2) and off-board chargers (level-3) [3, 4]. A single-phase 120 V/230 V ac supply is limited to about 1.92 kW used to charge level-1 battery charger and works as slow charging for overnight charging. The level-2 charging refers to an onboard/off-board charger suitable with single-phase, 230 V, 50 Hz/three-phase, 415 V, 50 Hz ac supply, operates up to 19.2 kW. To improve the fast-charging time, typically 10–30 min approximately can be achieved with the off-board (level-3) charger. The onboard charger is placed inside the vehicle that uses a suitable outlet ac supply. However, the off-board charger is located outside the vehicle at a fixed location and to direct charge the EV battery. Therefore, an off-board charger is less constrained by size and weight [5, 6].

The AC/DC power converter is a key component of the onboard battery charger which is located inside the EVs/PHEVs [7]. Most battery chargers consist of an AC–DC converter followed by a non-isolated/isolated DC–DC converter to improve the power quality. The active PFC techniques can be divided into two categories: the single-stage and the two-stage approach [7,8,9,10]. In a single-stage, a diode bridge rectifier is widely used to produce unregulated DC output. Due to the nonlinear property of the rectifier, it supplies a non-sinusoidal and high value of peak distorted current which has 70–80% low THD and low input power factor (PF) of the order 0.7–0.8 lagging. According to IEC 61000-3-2, it is necessary to maintain input PF above 0.9 and THD in source current below 5% [11, 12]. To satisfy the guidelines of the IEC Standard, there are several PFC converters have been proposed in the literature for power quality improvement [12]. Therefore, the single-stage approach is suitable for low-power applications. The two-stage approach is preferred where the power rating requirement is relatively high but suffers from poor efficiency.

Generally, the PFC converters are designed to operate in continuous conduction mode (CCM) or discontinuous conduction mode (DCM) [13]. In DCM mode, these converters are suffering from large voltage/current stress and high switching and conduction losses. Hence, DC–DC converters with DCM mode are advantageous for low-power applications. Based on the literature review, the boost and boost derived converters like flyback converter, etc., are found to be most appropriate for DCM PFC usage [14]. On the other hand, CCM associated with low switch stress is preferred for medium and high-power applications. Contrary, the PFC converters exhibit huge efficiency variations when fed from a wide range of input supply variations (85–265 V) [15]. At low input voltage, the boost converter suffers from poor efficiency as a consequence of high conduction losses in switch and reverse recovery losses in a diode. Thus, a large heat sink is required for losses dissipation, and security in the DC–DC converter leads to low power density [16,17,18].

These losses can be reduced by providing a high step-up gain and lower switch stress by employing DC–DC converters at low input voltage operation. There are several topologies which include transformer-based topologies, cascaded converters, quadratic converters, coupled inductor-based converters, and voltage multipliers. These converters include power factor correction to minimize harmonic currents drawn from the supply and provide regulated DC link voltage. Therefore, these topologies are widely used in battery charging applications [19]. Alike, a Cuk DC–DC converter which is derived from the buck and boost converters can generate the output voltage higher or lesser than supply voltage with reverse polarity. It consists of an intermediate capacitor that transfers energy from source to load. It has many advantages like a wide voltage conversion ratio, smooth source and load current, low conduction losses, and capacitor energy transfer [20, 21]. Despite aforesaid advantages, it suffers from high voltage stress and high filter size, and oversized components rating. To mitigate these disadvantages, three-level converters can be used which reduce filter size as well as voltage stress across the switch. The three-level converters are very much capable of smooth battery charging applications for electric vehicles [21]. Besides, a feed-forward control scheme is employed by eliminating distortion in source current, making input impedance resistive to ensure the proper functioning of the PFC converter [22,23,24].

The paper is structured in six sections. The technical issues and challenges related to PFC converters are discussed in Sect. 1. The schematic layout of system configuration and operation details of the three-level PFC CUK converter is demonstrated in Sect. 2. The design of circuit components and control algorithm of the proposed converter is presented in Sect. 3 and Sect. 4, respectively. Section 5 presents simulation and experimental results with resistive and battery loads. Power quality performances have also been discussed in Sect. 5. In the end, the conclusion is summarized in Sect. 6.

2 Operation analysis of PFC converter

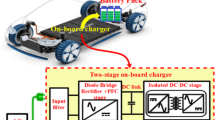

The general layout of a single-phase PFC power converter for a battery charging system mainly consists of a single-phase ac supply (vs), a diode bridge rectifier (DBR), a three-level Cuk DC–DC converter, and a battery pack of an electric vehicle as shown in Fig. 1.

2.1 Topology

A three-level Cuk converter-based power factor correction (PFC) circuit is proposed in Fig. 1a. It comprises a diode bridge rectifier (DBR) and a three-level CUK converter with different loads. The three-level Cuk converter consists of an input inductor (L1), energy transferring capacitors (C1, C2), output inductor (L2), output capacitor (Co), and power diodes (D1, D2). It is designed to operate in continuous conduction mode (CCM) during one switching period, i.e., for a particular switching cycle, input inductor current (iL1) never becomes zero.

Figure 1b illustrates the schematic diagram of the control scheme for the PFC converter which includes constant current (CC) and constant voltage (CV) modes of operation employed during battery charging application. The selection of charging modes either CC or CV depends on the value of state of charge (SOC) of the battery. The mode selector block inside the controller circuit changes the mode of operation from CC to CV. Initially, the battery is charged in CC mode in which the current controller maintains a constant current to charge the EV battery. As soon as the SOC of the battery reaches more than 85%, the operation of the converter is shifted to CV mode. During the CV mode of operation, the voltage controller maintains the constant output voltage of the converter to charge the battery.

2.2 Modes of operation

To carry out steady-state analysis of the proposed converter, the source voltage (vs) is assumed to be constant (Vs) over a particular sampling time (Ts). As supply voltage keeps on changing in each sampling time, the duty cycle (D) also keeps on varying in each sampling. For one switching period (Ts), each switch is turned on for DTs and turns off for (1 − D)Ts. The four operating modes are identified in each sampling period which repeats multiple times in one cycle of 50 Hz supply frequency as shown in Figs. 2 and 3. Depending upon the supply voltage (vs), the duty ratio D of a switch may be classified as D < 0.5 and D > 0.5.

-

A.

Case-1 when each switch is operated with D < 0.5

In this case, waveforms of current and voltage of circuit parameters for one switching period are shown in Fig. 2a.

Mode-1 (0 < t ≤ DTs): In this mode, switch SW1, diode D2 turns on and switch SW2, diode D1 turned off as shown in Fig. 3a. The input inductor L1 charges through path vs-L1-SW1-D2 and output inductor L2 charges with SW1-D2-CO-L2-C1 as well as intermediated capacitors C1, C2 discharges. Thus, inductor currents \(i_{{L_{1} }}\) and \(i_{{L_{2} }}\) are increased and achieved their respective final values at time DTs. The corresponding equations are following as:

Here, the average voltage across intermediate capacitor C1and C2 is shown in Eq. (1).

Mode-2 (DTs < t ≤ Ts/2): In this mode, switches SW1, SW2 kept off and diodes (D1, D2) conduct as illustrated in Fig. 3d. The input inductor L1 discharges through the path C1-D1-D2-C2-VS-L1 and L2 discharges through output capacitor Co. The current through both the inductors fall from their final values to initial values as shown in Fig. 2a. The corresponding equations are given as:

Mode-3(Ts/2 < t ≤ DTs + Ts/2): In this mode, diode D2 turned off, but D1 remains on with SW2 on and SW1 off as depicted in Fig. 3b. The currents through inductors raise from their initial values to final values same as mode-1. The corresponding equations are given as:

Mode-4 (DTs + Ts/2 < t ≤ Ts): The operation in mode-4 is the same as mode-2 switch SW1 turned off and switch SW2 kept off and diodes (D1, D2) both are conducting depicted in Fig. 3d.

-

B.

Case-2 when each switch is operated with D > 0.5

The voltage and current waveforms of various parameters over one switching cycle are depicted in Fig. 2b. Based on the state of switches, four modes of operations over one switching are identified. In the case of a duty ratio greater than 0.5, the output voltage should be greater than the input voltage.

Mode-1 (0< t ≤ (DTs−Ts/2)): Initially switches SW1, SW2 turned on and diode D1, D2 kept off as illustrated in Fig. 3c. Input inductor L1 is charging with input voltage vs and output inductor L2 is charging through C1-SW1-SW2-C2-CO-L2. Hence inductor currents iL1 and iL2 are increased and achieved their respective final values at time (DTs − Ts/2). The corresponding equations are given as:

Mode-2 ((DTs−Ts/2) < t ≤ Ts/2): In this mode, SW2 turned off, but SW1 remains on with D1 off and D2 on as depicted in Fig. 3a. The voltage across both the inductors becomes negative; hence, the currents through inductors fall from their final values to initial values because the voltage across inductors is negative. The corresponding equations are given as:

Mode-3 (Ts/2 < t ≤ (Ts − DTs)): The operation in mode-3 is same as mode-1. In case-2, for D < 0.5 because both switches SW1 and SW2 are conducting and diode are reversed bias depicted in Fig. 3c.

Mode-4 ((Ts − DTs) < t ≤ Ts): At the time instant t = DTs, SW2 remains on, SW1 turns off and D1 turns on and D2 turns off as illustrated in Fig. 3b. The current through both the inductors (iL1, iL2) again decrease from their final values and related equations are given below:

3 Design of passive components of PFC converter

Based on the power ratings of the three-level converter, proper selection of passive components like inductors (L1, L2) and capacitors (C1, C2, Co) is to be carried out for providing the well-maintained DC output with improved power quality features at the input side. A single-phase 240 V, 50 Hz is supplied to a DBR feeding the TL converter which is given by the equation vs(t) = VmSin(2πfL)t = 240√2Sin(314t); where Vm, fL is the peak voltage and line frequency of supply system, respectively. The output of DBR, which is connected as the input voltage to a three-level converter, is given in Eq. (8);

For the satisfactory operation of an inductor, the average voltage over one switching cycle should be zero. Thus, the average voltage across inductor L1 is given as:

After solving Eq. (9), the steady-state output voltage and the value of duty ratio D, in the terms of supply voltage and output DC voltage is given in Eq. (10):

Thus, the duty ratio D is measured as 0.65 for three-level Cuk converter PFC operation.

3.1 Design of inductors (L 1, L 2)

The value of inductors (L1, L2) can be selected by evaluating the average inductor current. With consideration of lossless converter and CCM mode of operation, the boundary values of the inductor current are identified by using Eqs. (4) and (10). After that designed equations for inductors for different range of duty ratio are given in Eq. (11):

where ripple in input inductor current ΔIL1 = 30% ripple of input current Is, ripple in output inductor current ΔIL2 = 30% ripple of input current Io.

As the PFC converter is operated in continuous current mode, IL1min should be positive. The minimum value of L1 can be determined by keeping the minimum inductor current to zero.

Here, L1crit is the minimum value of inductance, the value above which the PFC converter operated in CCM mode.

The voltage and current equations for the intermediate inductor (L2) are the same as the input inductor (L1) with the same boundary values. Hence design values of L2 will be the same as L1 in both Eqs. (11) and (12). The critical inductance (L1, L2) is calculated from Eq. (11) for D > 0.5 is 3 mH. And the selected values of L1, L2 in the CCM mode of operation are specified is given in “Appendix”.

3.2 Design of intermediate capacitors (C 1, C 2)

Figure 3a indicates that both intermediate capacitor currents (iC1, iC2) are the same as current flow in an intermediate inductor (iL2) for that mode hence values of C1 and C2 will be the same. The capacitor current iC1 can be represented during switching as shown in Fig. 2b. The value of capacitor C1 can be calculated by

where ΔVC1 = ripple voltage across C1, from Eqs. (1) and (13). Thus, the values of capacitors are given by Eq. (14);

For the duty ration, D > 0.5, the calculated intermediate capacitances (C1, C2) are 1.8 μF and the selected value for intermediate capacitors is specified in “Appendix”.

3.3 Design of output capacitor (C o)

The value of output capacitor depends upon ripple in output voltage (ΔVCo). For the low value of ripple content, the designed value of capacitor is higher. The output voltage ripple (ΔVCo) can be calculated by Eq. (16) and output current (iCo) is given in Eq. (15).

After solving Eq. (15), the value of output capacitor is given by:

The calculated and selected value for output capacitance (Co) is 1000 μF. The selected design components values are specified in “Appendix”.

4 Control algorithm

To achieve the desired objective of ripple-free output voltage/ current along with improved input power factor, the average current control technique is employed. It consists of two control loops namely inner input current control to maintain the unity power factor operation and outer control loop for maintaining the constant output voltage/current. The inner current control loop is faster and it tries to reduce error between average input current [23]. Besides, there is one feed-forward network that tries to reduce zero crossing error in supply current.

For outer control loop operation, initially, the battery will operate under CC mode and the mode selector block selects constant current (CC) mode of operation. In CC mode of operation, Battery will operate at 30% SOC and compare reference current I*DC(k) with output current IDC(k) which generate a current error Ie(k), where Ie(k) at any instant ‘k’ is given as

This current error is the input of the current PI controller, and it generates a controlling signal Ic(k), which is shown in Eq. (18) are:

where kpi, kii are the proportional and integral gain of the outer current PI controller.

In the case of an outer voltage control loop, when battery voltage reaches 85% of SOC value then mode selector block selects constant voltage (CV) mode of operation. In this control algorithm (Refer Fig. 4), the output voltage controller will be activated and compared a reference voltage V*DC(k) with the output DC voltage VDC(k). Then, it generates a voltage error Ve(k), where Ve(k) at any instant ‘k’ is given as

The voltage error Ve(k) is the input of a voltage PI controller and it generates a controlling voltage signal Vc(k), which is represented by

where kpv, kiv are the proportional and integral gain of the outer voltage PI controller. The current reference i*L1(k) is produced by multiplying Vc(k) with the unit template of supply voltage as follows:

The comparison is done between the current reference signal i*L1(k) and input inductor current iL1(k) which produces a current error ILe(k), where ILe(k) at any instant ‘k’ is given as

This ILe(k) is fed to another proportional-integral (PI) controller and output of PI is generated controlled output as ILc(k) which is given by Eq. (23);

where kp1, ki1 are proportional and integral gains of the inner current PI controller. The output of inner current PI controller ILc(k) is added up with the output of feed forward network and compares with a high-frequency ramp signal of switching frequency 10 kHz. The output of this comparator is used as switching pulses for switch SW1 and for generating the switching pulses for switch SW2, same high frequency ramp signal is delayed by 180° using a transport delay. This feed-forward network is nothing but a varying duty ratio of the proposed converter. Here, Gcv = gain of voltage controller; Gci = gain of current controller; Gff = gain of feed-forward network; Td = transport delay.

5 Results and discussions

A 3.2 kW, 400 V/8 A three-level CUK converter-based on-board charger is developed in MATLAB software for simulation study with “ode4” solver and same is done for real-time implementation with 20 µs sampling time. The developed charging system performances are shown as per converter design parameters shown in “Appendix”. The steady state and dynamic performance is investigated with respect to power quality features like supply current THD, supply voltage THD and input PF with resistive and battery loads. The charging performance of the battery is examined in constant current (CC) and constant voltage (CV) modes on the basis of state of charge (%SOC). The waveform results of source voltage (vs), source current (is), output voltage (VDC), output current (IDC), inductor currents (iL1, iL2), intermediate capacitor voltage (vC1), voltage across switch and diode (VSW1, VD2), switch current (ISW1), battery voltage (VB) and battery current (IB) are examined for resistive and battery loads shown in Fig. 5. Figure 6 shows simulation results of power quality indices like power factor and THD in supply current.

5.1 Simulation results

A developed Simulink model analysis of proposed PFC system is done for steady and dynamic state by feeding 400 V/8 A resistive load and battery load with nominal voltage of 345 V/40 AH at 230 V, 50 Hz supply voltage.

-

A.

Steady-state analysis feeding resistive load

Figure 5a shows steady-state analysis of the PFC converter for resistive load at supply voltage of 230 V, 50 Hz for time t = 0.9 to 1.2 s. It is observed that source current waveform is purely sinusoidal and also in phase with source voltage which indicates that proposed converter is operating at unity PF. The current through input and output inductor follows output current of DBR which is displayed in continuous conduction mode. Figure 5a shows intermediate capacitor voltages (vC1) is equal to summation of half of sinusoidal input voltage and constant output DC voltage. The min value of voltage of intermediate capacitor is 200 V and max value is 362 V at 230 V supply voltage. The shown output voltage and current maintained constant DC value 400 V and 8 A, respectively, in Fig. 5a. When switch and diode is in off state, thus appeared voltage across switch and diode is 362 V, i.e., equal to half of varying input voltage and constant DC output voltage is also presented by Fig. 5a. When switch is in on state, the appeared current across switch is sum of input and output current shown by simulation result of Fig. 5a.

-

B.

Dynamic analysis feeding resistive load

Figure 5b, c shows dynamic performance results at source voltage variation and load voltage variation, respectively, for time t = 0.9 to 1.6 s. The 20% step decrease in source voltage is done at t = 1 s then again set at t = 1.2 s with 230 V nominal supply voltage shown in Fig. 5b. The variation in source voltage from 230 to 184 V shows the variation in input current. However, the output voltage VDC is unaltered after 300 ms small period of disturbance at unity PF shown in Fig. 5b. Figure 5c shows performance of the TL converter with load variation. The load is increased from 8 to 16 A at t = 1 s and then it again settled to 8 A at t = 1.3 s at same input voltage. In results, output voltage is maintained at its desired value (400 V) at unity PF with small disturbance of 200 ms. Both source and load variations show constant output voltage VDC 400 V and maintained power factor unity which satisfied the PFC operation of proposed converter.

-

C.

Steady-state analysis feeding the battery load

A battery charging is done by proposed PFC converter either in constant voltage (CV) mode or in constant current (CC) mode. Figure 5d, e presents steady-state analysis of PFC converter with battery load in CC and CV mode, respectively, at input voltage of 230 V, 50 Hz. Depending upon the SOC of battery, the operation of converter is shifted from CC to CV mode. Initially, converter operates in CC mode to charge battery with SOC of 30%. In CC mode, therefore, the battery is charging with constant output current of 8 A. Figure 5d presents the max value of source current (is) is 19.8 A, output voltage (VDC) 388 V which is less than constant output voltage 400 V, and constant output current (IDC) 8 A which is equal to constant charging current 8 A. Figure 5d also shows the voltage across the battery is less, i.e., 365 V and battery current is equal to 8 A of constant current shows the CC mode of charging operation.

When SOC of battery reaches to 85%, converter operates in CV mode. Now, it shows the converter is charging with constant output voltage of 400 V. Figure 5e presents the max value of source current is 5.2 A, output voltage (VDC) 400 V which is equal to constant charging voltage 400 V, the output current of 2.2 A which is less than constant output current of 8 A. Therefore, the voltage and current across the battery are 395.4 V and 2.2 A. It is identified that in CV mode, battery is charged with constant voltage of 400 V and in CC mode, the battery is charged with constant current 8 A, and the converter is maintained input power factor (PF) unity in both the operating modes. Figure 6 depicts the converter harmonic spectrum and THD of the source current (is) of battery charging in CC and CV mode at 230 V supply voltage. The shown input current THDs are 3.78% and 4.2% in CC and CV mode, respectively.

5.2 Test results

The proposed charging system results are verified experimentally in real time using Spartan3 FPGA board (XC3S5000) with sampling time of 20 μs. The same design parameters shown in “Appendix” are also used for test results. A Fluke Power Analyser and a Digital oscilloscope (DSO) are used in recording of test results.

Figure 7 shows test performance of the proposed converter with resistive load, and battery load at supply voltage of 230 V in CC and CV mode, respectively. Figure 7a shows waveforms of input voltage and current are in same phase, and constant DC output voltage and current of 400 V and 8 A, respectively. Figure 7b displays results of input inductor current, intermediate capacitor voltage, switch voltage and current stress which is same as simulation results. It is observed that constant DC output current of 8 A is maintained during CC mode of battery charging depicts in Fig. 7c. Further, when SOC of battery reaches to 85%, the operation of converter is shifted to CV mode in which output voltage of 400 V is maintained constant as seen in Fig. 7d. Figure 7d, e shows unity power factor (PF) in both the charging operating modes.

To assess the dynamic performance of converter, the supply voltage variation from 230 to 184 V (20% variation) at 50 Hz is carried out with resistive load. It is observed in Fig. 7e that shows DC output voltage remained constant at 400 V after small disturbance of 300 ms with load current of 8 A. Figure 7f shows performance of converter under load variation from 8 to 16 A, at nominal supply voltage of 230 V, 50 Hz. The same constant DC voltage is maintained constant after 300 ms disturbance. In Fig. 7e, f, the dynamic state performance the charging system maintain both constant output voltage and power factor unity.

Figure 8 shows waveforms of THD of supply current, real power (Ps), reactive power (Qs), input PF and distortion factor in both CC and CV modes at supply voltage 230 V, 50 Hz. it is observed that THD in source current is of 3.6% and reactive power required is 0.40 KVAR in CC mode, and THD in source current is 3.1%, reactive power required 143 kVAR in CV mode. Table 1 depicts comparison of experimental and simulation results of converter related to power quality features at universal input voltages (85–265 V).

A comparison study of proposed TL CUK converter is executed with conventional CUK converter under wide voltage variations shown in Fig. 9. It is perceived that THD and Efficiency variation with output power at different load conditions shown in Fig. 9a, b. At 230 V of supply voltage, the system efficiency achieved in CC and CV mode is 97.1% and 94.5%, respectively, and input current THDs in both operating modes are less than 5%. Figure 9c–f shows proposed converter losses are reduced as compared to conventional converter under voltage variations. In spite of the additional losses being incurred in the proposed converter, the total loss is found to be less under different input voltage conditions. Table 2 shows the comparison of TL CUK and conventional CUK PFC converter parameters. As compared to conventional Cuk PFC converter, proposed converter shows the reduction in reduced voltage stress across switches and diodes, switching and conduction losses across switch, and switching and conduction losses across diode.

6 Conclusion

The PFC-based three-level (TL) CUK converter is proposed and examined for resistive load of 3.2 kW/400 V and onboard EV battery charging application in both CC and CV operating modes. The proposed converter offers PFC characteristics in CCM mode by using feed-forward control techniques. The feed-forward technique advantages are to provide zero crossing error in sine template and made the supply current in phase with supply voltage. The designed converter validates power factor unity, efficiency 97.1% and current THD less than 5% meets the required criteria as prescribed by IEEE Standard 519-1992 and IEC61000-3-2. The added benefits of the proposed TL CUK converter topology are reducing voltage stress to half, reduce filter size, lesser losses across switch and diode as compared to conventional CUK converter. Thus, it reduces the switch rating, improves the overall efficiency 2–3%, and also improves dynamic response. The simulation results of a proposed converter with wide supply voltage variations are also examined with resistive and battery load. The proposed charger has shown satisfactory characteristics during steady-state, under load, and supply voltage variations. These results are also validated experimentally in a real-time approach. Therefore, the PFC converter is well suited for high input/output voltage applications such as onboard charging for electric vehicles.

References

Liu R, Dow L, Liu E (2011) A survey of PEV impacts on electric utilities. In: Proceedings of IEEE power and energy society innovative smart grid technologies conference, Anaheim, CA, pp 1–8. https://doi.org/10.1109/ISGT.2011.5759171

Tar B, Fayed A (2016) An overview of the fundamentals of battery chargers. In: Proceedings of IEEE 59th international midwest symposium on circuits and systems (MWSCAS), Abu Dhabi, pp 1–4. https://doi.org/10.1109/MWSCAS.2016.7870048

Solero L (2001) Nonconventional on-board charger for electric vehicle propulsion batteries. IEEE Trans Veh Technol 50(1):144–149. https://doi.org/10.1109/25.917904

Yilmaz M, Krein PT (2013) Review of battery charger topologies, charging power levels, and infrastructure for plug-in electric and hybrid vehicles. IEEE Trans Power Electron 28(5):2151–2169. https://doi.org/10.1109/TPEL.2012.2212917

Shi Y, Tang AK (2017) A single-phase integrated onboard battery charger using propulsion system for plug-in electric vehicles. IEEE Trans Veh Technol 66(12):10899–10910. https://doi.org/10.1109/TVT.2017.2729345

Kim M, Kim BL (2017) An integrated battery charger with high power density and efficiency for electric vehicles. IEEE Trans Power Electron 32(6):4553–4565. https://doi.org/10.1109/TPEL.2016.2604404

Oruganti R, Srinivasan R (1997) Single phase power factor correction: a review. Recent Adv Power Electron Drives 22(6):753–780. https://doi.org/10.1007/BF02745844

Musavi F, Edington M, Eberle W, Dunford WG (2012) Evaluation and efficiency comparison of front end AC–DC plug-in hybrid charger topologies. IEEE Trans Smart Grid 3(1):413–421. https://doi.org/10.1109/ECCE.2011.6063780

Singh B, Singh BN, Chandra A, Al-Haddad K, Pandey A, Kothari DP (2003) A review of single-phase improved power quality AC-DC converters. IEEE Trans Ind Electron 50(5):962–981. https://doi.org/10.1109/TIE.2003.817609

Singh B, Singh S, Chandra A, Al-Haddad K (2011) Comprehensive study of single-phase ac-dc power factor corrected converters with high-frequency isolation. IEEE Trans Ind Inform 7(4):540–556. https://doi.org/10.1109/TII.2011.2166798

International Standard IEC 61000-3-2 (2000) Limits for harmonic current emissions (equipment input current ≤16 A per phase)

Erickson RW, Maksimovic D (2001) Fundamentals of power electronics, 2nd edn. Kluwer, New York

Jovanovic MM, Jang Y (2005) State-of-the-art, single-phase, active power-factor-correction techniques for high-power applications: an overview. IEEE Trans Ind Electron 52(3):701–708. https://doi.org/10.1109/TIE.2005.843964

Wang L, Wu QH, Tang WH, Yu ZY, Ma W (2017) CCM-DCM average current control for both continuous and discontinuous conduction modes boost PFC converters. In: Proceedings of IEEE electrical power and energy conference (EPEC), Saskatoon, SK, pp 1–6. https://doi.org/10.1109/EPEC.2017.8286149

Praneeth AVJS, Williamson SS (2018) A review of front end ac-dc topologies in universal battery charger for electric transportation. In: Proceedings of IEEE transportation electrification conference and expo (ITEC), Long Beach, CA, pp 293–298. https://doi.org/10.1109/ITEC.2018.8450186

Nussbaumer T, Raggl K, Kolar JW (2009) Design guidelines for interleaved single-phase boost PFC circuits. IEEE Trans Ind Electron 56(7):2559–2573. https://doi.org/10.1109/TIE.2009.2020073

Gautam D, Musavi F, Edington M, Eberle W, Dunford WG (2011) An automotive on-board 3.3 kW battery charger for PHEV application. In: Proceedings of IEEE vehicle power and propulsion conference, Chicago, IL, pp 1–6. https://doi.org/10.1109/VPPC.2011.6043192

Praneeth AVJS, Williamson SS (2019) A wide input and output voltage range battery charger using buck-boost power factor correction converter. In: Proceedings of IEEE applied power electronics conference and exposition (APEC), Anaheim, CA, USA, pp 2974–2979. https://doi.org/10.1109/APEC.2019.8721797

Ananthapadmanabha BR, Maurya R, Arya SR (2018) Improved power quality switched inductor Cuk converter for battery charging applications. IEEE Trans Power Electron 33(11):9412–9423. https://doi.org/10.1109/TPEL.2018.2797005

Ruan X, Li B, Chen Q (2002) Three-level converters-a new approach for high voltage and high power DC-to-DC conversion. In: Proceedings of IEEE 33rd annual IEEE power electronics specialists conference (Cat. No. 02CH37289), Cairns, Qld, Australia, pp 663–668. https://doi.org/10.1109/PSEC.2002.1022529

Ruan X, Li B, Chen Q, Tan S, Tse CK (2008) Fundamental considerations of three-level DC–DC converters: topologies, analyses, and control. IEEE Trans Circuits Syst I Regul Pap 55(11):3733–3743. https://doi.org/10.1109/TCSI.2008.927218

Jappe TK, Mussa SA (2009) Discrete-time current control techniques applied in PFC boost converter at instantaneous power interruption. In: Proceedings of Brazilian power electronics conference, pp 1118–1123. https://doi.org/10.1109/COBEP.2009.5347636

Van de Sype DM, De Gusseme K, Van den Bossche AP, Melkebeek JA (2005) Duty-ratio feedforward for digitally controlled boost PFC converters. IEEE Trans Ind Electron 52(1):108–115. https://doi.org/10.1109/TIE.2004.841127

Chen H, Li H, Yang R (2009) Phase feedforward control for single-phase boost-type SMR. IEEE Trans Power Electron 24(5):1428–1432. https://doi.org/10.1109/TPEL.2009.2013953

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

S. no. | Specific parameters | Values |

|---|---|---|

1 | Single-phase supply voltage | 230 V, 50 Hz |

2 | Input and output inductances (L1, L2) | 5 mH |

3 | Intermediate capacitors (C1, C2) | 10 μF |

4 | Output capacitor (C0) | 3000 μF |

5 | Switching frequency (fs) | 10 kHz |

6 | Load | 400 V/8 A |

7 | Battery nominal voltage | 345 V, 40 AH |

Control parameters: Gains of output PI voltage controller kpv = 0.00005, kiv = 20 for CV mode, gains of the output PI current controller kpi = 0.1, kii = 10 for CC mode and inner PI current controller kp1 = 0.3, ki1 = 7.8 same for both CV and CC mode operation; feed forward gain is kd = 1.8.

Rights and permissions

About this article

Cite this article

Maurya, R., Arya, S.R., Saini, R.K. et al. On-board power quality charger for electric vehicles with minimized switching stresses. Electr Eng 104, 1667–1680 (2022). https://doi.org/10.1007/s00202-021-01407-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-021-01407-1