Abstract

This article proposes the configuration of a multifunctional active filter using voltage differencing inverting buffered amplifier (VDIBA). The filter configuration is resistorless and uses two VDIBA blocks to implement low pass, high pass and band pass filter responses. The working of the presented VDIBA-based configuration is thoroughly examined through mathematical and simulation analyses. The VDIBA-based configuration is simulated using a 45-nm CMOS technology node using ADE of Cadence at ± 0.95 V supply voltage.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

The rapid improvements in VLSI designs have changed the dynamics of active elements. There is also a huge demand for active elements in applications such as oscillators and filters to consume as low power as possible. The operational amplifier has been the most prevalent and extensively used active block for a long time. New advances have also made it necessary for both analog and digital blocks to be implemented on the same IC.

Communication has witnessed a gradual evolution from analog-to-digital communication. However, practically signals are analog in nature. Speech signal, real time audio are all analog signals which should undergo digital communication. Analog signals are initially converted into digital signals using analog-to-digital (A/D) converters. The signals need to initially pass through an analog filter to achieve noise immunity. Analog filters, thus hold a high demand in the communication and signal processing domain.

Authors in [1] have presented the promising active elements and their future applications. In this paper, several active elements such as differential difference amplifier (DDA), four terminal floating nullor (FTFN), operational transconductance amplifier (OTA), voltage differencing inverting buffered amplifier (VDIBA), voltage differencing transconductance amplifier (VDTA), etc., were explained in brief. This paper proposes a new internal structure of the active element, VDIBA, along with its filter applications. Several operations of VDIBA, for-instance, inductor emulator [2], multifunctional filter [3], multiplier [4], oscillator [5], etc., are reported in literature. The intrinsic structure of VDIBA consists of a transconductance stage followed by an inverted buffered amplifier stage [6]. In this article, a VDIBA-based multifunctional filter configuration is proposed. The traditional transconductance phase present at the input of VDIBA is succeeded by an Arbel–Goldminz transconductance stage [7]. This Arbel–Goldminz transconductance stage eradicates the requirement for transistor matching and generates optimal outputs. Also, as in the Arbel–Goldminz transconductance stage, the transistors are placed symmetrically, this circuit is more immune to noise in contrast with earlier traditional transconductance stage. The output of the initial transconductance stage is supplied to an inverted buffer stage, which provides the necessary amplification to the circuit. A multifunctional filter can mimic the behavior of all different kind of filters. This article demonstrates the three filters namely high pass, low pass and band pass filter.

2 VDIBA Design

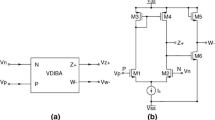

VDIBA is a four-port active element with block diagram depicted in Fig. 1. The functionality of VDIBA and its ports are mathematically represented by the subsequent matrix form [8]:

As shown in block diagram, there are four terminals, i.e., p, n, w and z. The voltages vp, vn represent the voltages at input terminals, ip, in represent the currents at input terminals. vz, iz and vw, iw represent the voltage and current at the intermediate terminal and the output terminal, respectively. The transconductance (gm) of the transconductance stage is given by

The internal representation of presented VDIBA configuration is shown in Fig. 2. In the representation, the first stage is realized with Arbel–Goldminz transconductance stage. This first stage contains two NMOS (M1 and M2) and PMOS (M3 and M4) transistor pairs. This stage achieves the same functionality which is achieved in a differential amplifier. The first stage is followed by an inverted voltage buffer (IVB) stage. In the second stage, a common source (CS) amplifier with a NMOS transistor load is realized. The overall configuration is provided with suitable bias current source (Ibias) pairs, supply voltages VDD and VSS to bias the transistors in saturation region.

The small-signal equivalent model of the presented VDIBA configuration is displayed in Fig. 3. Analysis of this equivalent model of the VDIBA configuration results in the subsequent expression of overall gain:

Here, gmk is the transconductance of kth NMOS/PMOS transistor. The transconductance depends on bias current Ibias, oxide capacitance Cox, mobility μk and aspect ratio (W/L). The tunability of the proposed VDIBA design is provided through changing the value of Ibias.

3 Multifunctional Active Filter Configuration

The proposed multifunctional active filter configuration is shown in Fig. 4. In this design, two VDIBA blocks are connected in cascade. The Arbel–Goldminz stage in each VDIBA is configured to act as a feedback amplifier.

The output port of the first VDIBA block is connected to the input port of the second VDIBA block. Two capacitors (C1 and C2) are connected at both the intermediate ports.

As shown in Fig. 4, the voltage mode multifunctional filter has multiple input voltages (V1, V2, V3) and single output (Vout). For the purpose of implementing a particular filter configuration, i.e., lowpass, highpass and bandpass, the voltages are arranged as per the following:

-

(1)

If voltage VLP is assigned to V3 and V1 = V2 = 0, the configuration implements second-order low pass (LP) filter. The voltage transfer function of the configuration is evaluated as

$$ \frac{{V_{{{\text{out}}}} }}{{V_{{{\text{LP}}}} }} = - \frac{{g_{{\text{m}}}^{2} }}{{s^{2} C_{1} C_{2} + sg_{{\text{m}}} \left( {C_{2} + C_{1} } \right) + g_{{\text{m}}}^{2} }} $$(5) -

(2)

If voltage VHP is assigned to V1 = V2 and V3 = 0, the configuration implements second-order high pass (HP) filter. The voltage transfer function of the configuration is evaluated as

$$ \frac{{V_{{{\text{out}}}} }}{{V_{{{\text{HP}}}} }} = \frac{{s^{2} C_{1} C_{2} }}{{s^{2} C_{1} C_{2} + sg_{{\text{m}}} \left( {C_{2} + C_{1} } \right) + g_{{\text{m}}}^{2} }} $$(6) -

(3)

If voltage VBP is assigned to V1 and V2 = V3 = 0, the configuration implements second-order band pass (BP) filter. The voltage transfer function of the configuration is evaluated as

$$ \frac{{V_{{{\text{out}}}} }}{{V_{{{\text{BP}}}} }} = - \frac{{sg_{{\text{m}}} C_{1} }}{{s^{2} C_{1} C_{2} + sg_{{\text{m}}} \left( {C_{2} + C_{1} } \right) + g_{{\text{m}}}^{2} }} $$(7)

The parameters of filter, namely cut-off frequency (ωc) and bandwidth (BW) for the multifunctional filter configuration can be expressed as:

From (8) and (9), it can be noticed that the cut-off frequency (ωc) and bandwidth (BW) for the multifunctional filter can be electronically controlled. Both the filter characteristics can be varied by changing the transconductance (gm) of the VDIBA. In addition, the proposed configuration is resistorless and employs only grounded capacitors, thereby validating its suitability for fully integrated circuit applications.

4 Simulation Results

Various analyses including AC, DC and transient were performed on the proposed design using Cadence. The performance is analyzed through simulations carried out at 45-nm CMOS. The bias supply current (Ibias) is fixed at 145 μA and the voltages, VDD and VSS, is fixed at + 950 mV and − 950 mV, respectively.

DC analysis of proposed VDIBA configuration is carried out and the result is depicted in Fig. 5. During DC analysis, the output currents, Iz and Iw, are plotted with respect to difference of two input voltages, i.e., (Vp − Vn). Further, the transient analysis of proposed VDIBA configuration is performed and the result is shown in Fig. 6. Figures 7, 8 and 9, respectively, represent the frequency response of band pass, high pass and low pass obtained during AC analysis. For AC analysis, a sinusoidal signal of 10 mV amplitude and 10 kHz frequency is applied. Figures 7, 8 and 9 show the phase magnitude and gain magnitude plots which validate the working of the proposed configuration. The power dissipation of the multifunctional filter design is measured as 2.3 mW.

5 Conclusion

This article proposes an active multifunctional filter configuration using an innovative and stable design of VDIBA. This circuit can be tuned with external current. The working of both VDIBA and the multifunctional filter are validated with the help of simulation results. The average power consumption of filter configuration is measured to be 2.3 mW with cut-off frequency around 10 MHz. This proposed configuration can be used in high performance signal processing applications which is required for analog and digital communications.

References

Biolek D, Senani R, Biolkova V, Kolka Z (2008) Active elements for analog signal processing: classification, review, and new proposals. Radioengineering 17(4):15–32

Tangsrirat W (2017) Synthetic grounded lossy inductance simulators using single VDIBA. IETE J Res 63(1):134–141

Kumari S, Gupta M (2018) Design and analysis of tunable voltage differencing inverting buffered amplifier (VDIBA) with enhanced performance and its application in filters. Wireless Pers Commun 100:877–894

Tangsrirat W (2017) Resistorless tunable capacitance multiplier using single voltage differencing inverting buffered amplifier. Rev Roum Sci Techn 62(1):72–75

Channumsin O, Tangsrirat W (2017) VDIBA-based sinusoidal quadrature oscillator. Prz Elektrotech 93(3):248–251

Kacar F, Yesil A, Noori A (2012) New CMOS realization of voltage differencing buffered amplifier and its biquad filter applications. Radioengineering 21(1):333–339

Arbel AF, Goldminz L (1992) Output stage for current-mode feedback amplifiers, theory and applications. Analog Integr Circ Sig Process 2(3):243–255

Sotner R, Jerabek J, Herencsar N (2013) Voltage differencing buffered/inverted amplifiers and their applications for signal generation. Radioengineering 22(2):490–504

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kumar, V., Kumar, A., Kumar, A., Singh, B.K. (2023). A Novel Multifunctional Active Filter Configuration. In: Szymanski, J.R., Chanda, C.K., Mondal, P.K., Khan, K.A. (eds) Energy Systems, Drives and Automations. ESDA 2021. Lecture Notes in Electrical Engineering, vol 1057. Springer, Singapore. https://doi.org/10.1007/978-981-99-3691-5_5

Download citation

DOI: https://doi.org/10.1007/978-981-99-3691-5_5

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-99-3690-8

Online ISBN: 978-981-99-3691-5

eBook Packages: EnergyEnergy (R0)