Abstract

With the drastic increase in power demand in the future, the dependability on renewable energy sources (RESs) is increasing leading to research on power electronic devices for high-efficiency operation. In this paper, the Zeta converter is interfaced with a high gain booster single-stage inverter. The RESs like solar photovoltaic array (PVA), wind generator, fuel cell, and battery generate a voltage at a very low amplitude which is boosted using this converter. The proposed single-stage boosting inverter (SSBI) has several advantages when compared to the conventional two-stage one in terms of the requirement of fewer components and simple topology. Single-cycle control with a non-linear controller is employed with the high gain SSBI to provide the controlled pulses to the switches to produce an ac output voltage. The Zeta converter is a typical DC-DC converter and generates boosted DC voltage with a normal gain value. The DC output of the Zeta converter is further fed to SSBI for high gain boost inverting operation. The modeling of the converter is carried out in MATLAB with all results represented with dynamic voltage changes.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

The micro-inverters that are designed for the solar photovoltaic (PV) are single-stage, two-stage, and multi-stage. The multi-stage small-scale inverters are typically including a step-up DC-DC converter with an optimal power point tracking (OPPT) control [1]. The two-stage smaller scale inverter can be outlined falling an OPPT-controlled stride with a network-tied high-frequency inverter and a DC-DC converter, while the single-stage needs to play out voltage step-up, OPPT, and DC-AC reversal works across the board stage. To change over and to connect the solar power to the utility grid, the low voltage of the solar PV board must be stepped up to coordinate the utility level. It represents a test to the architect of solar PV inverters as a customary lift converter cannot give the required pick up at high efficiency [2, 3]. The common problem of the single-stage DC-AC power framework is the AC-DC power decoupling issue [4].

Correct and suitable types of power converters are required for solar PV systems to meet various needs, and applications have a significant influence to obtain the optimum performance [5] as they act as an interface between the utility/main grids and/or residential loads and solar PV systems. Various modeling methods for grid-connected step-up PV systems intended to include different tools for the control design are presented in reference [6]. A detailed review of the various single-stage inverter (SSI) approaches in solar PV systems is presented in [7]. In reference [8], a Zeta converter with a coupled inductor is utilized for efficient recycling of leakage inductor energy. As the PV array (PVA) depicts as the floating source, there is an enhancement in the overall safety of the system. It also discusses operating principles, steady-state analysis, and stress on active components of the converter are also presented. The important characteristics of DC/DC converters as well as various MPPT approaches are analyzed and reviewed in [9].

Reference [10] describes the design and detailed operation of a Cuk-derived, common-ground PV micro-inverter. The present state-of-the-art approaches available for micro-inverters with a comprehensive overview of various technical characteristics such as grid compatibility abilities, control structures, power circuit configuration, energy harvesting capabilities, decoupling capacitor placement, and various mechanisms required for safety are presented in [11]. The classification of the PV system, various inverter types, the global status of the PV market, configurations of grid-connected PV inverters, and topologies are reviewed in [12].

The decoupling of AC–DC power is accomplished on a high-voltage dc link and hence it needs generally low capacitance esteem. The one-cycle control (OCC) has a quick reaction and low affectability to dc-transport voltage swell permitted applying yet littler decoupling capacitor esteem, what's more, has shown low THD output for various sorts of profoundly nonlinear burdens.

2 Proposed Modules and Functionalities

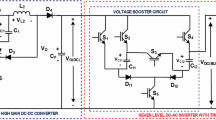

Several single-stage topologies which can understand voltage step-up and reversal in a single-stage are presented in the literature. In a double lift inverter load is associated with yields of two bidirectional lift converters. Figure 1 depicts the DC-AC boost converter. Subsequently, this topology takes a typical H-bridge with boosting inductors associated with the midpoints of legs [13, 14]. The negative marks of this topology are the constrained DC step-up increase, flowing currents, which disable the efficiency; and to some degree entangled control.

Figure 2 depicts another single-stage arrangement of the DC-AC converter. Contrasted with the topologies utilization of single lift inductor, no coursing currents and have a high voltage DC-link [15]. Likewise, customary control strategies can be connected. Also, the proposed topologies may give different decisions to single-stage arrangements.

In any case, the restricted dc step-up requires utilizing more costly high-voltage PV boards with 70–100 \(V_{{{\text{dc}}}}\) yield keeping in mind the end goal to get coveted DC-transport voltage good to network-associated inverters [16, 17]. On the other hand, utilizing the famous crystalline silicon modules with the 25–50 \(V_{{{\text{dc}}}}\) maximum power point (MPP) extend. In the field operating conditions, substantial electrolytic capacitors have a short life and impede the framework’s unwavering quality. Hence, the decoupling issue ends up one of the significant worries in the miniaturized scale inverter outline. An enhanced topology using the spillage vitality reusing showed 86% pinnacle efficiency [18, 19]. Some other fly back-based topology likewise makes utilization of an extra power decoupling circuit.

Another nonlinear control system, one-cycle control is presented for steady-state frequency operation. However, the SSBI can be able to control by any existing control techniques. Figure 3 depicts the high-gain SSBI. Contrasted with the topologies utilization of a single lift inductor, have a high voltage DC-link [20], no coursing currents, and a small decoupling capacitor. Likewise, customary control strategies can be connected. Also, the proposed topologies give different decisions in single-stage arrangements [21, 22]. The schematic view of the Zeta converter is depicted in Fig. 4.

To achieve a higher conversion ratio of voltage, with higher efficiency, higher gain enhancement techniques were implemented previously [23]. A boost converter is a power converter. Here in this converter, its DC voltage at the output is more prominent than its DC voltage at its input. The SSBI topology works in discontinuous conduction mode (DCM) all through the lattice cycle if it supports the operation of DCM through peak interim [24]. By applying the condition for the DCM or critical conduction mode (CCM) through peak interim yields the critical estimation of the adjustment file as beneath

where M is the modulation index, \(V_{{{\text{in}}}}\) is the input voltage, and \(V_{{\text{p}}}\) is the peak value of output voltage.

3 Implementation of High Gain SSBI for PV Array in Simulink

As mentioned earlier, the Zeta converter interfacing in an SSBI for PVA has been implemented in MATLAB Simulink software. MATLAB gives one of the successful modeling instruments and reenactment apparatus called Simulink. In engineering, it needs to represent the information graphically. MATLAB Simulink can be used for several applications such as image processing, signal processing, power electronics, basic electrical and electronics measurements, and instrumentation. Simulink is a piece graph condition for multi-space amusement and model-based outline. It underpins the recreation customized code age and steady tests and checks [25, 26]. Here viably gives a graphical depiction, can changes square libraries, and can agree to demonstrating and recreating dynamic structures. Along these lines, it is joined with MATLAB figuring into models and sends reenactment results to MATLAB for assist investigation.

This section presents the software design of the proposed models. Figure 5 depicts a simulation model of a high gain single-stage boosting inverter (implemented in Simulink model of MATLAB software) which is controlled by one cycle controller. It operates at an input voltage of 48 V, switching at 50 kHz frequency, and the output voltage at 436 V.

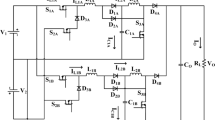

The PV array (PVA) comprises 8 PV cells, and all of them are associated in series to get a coveted voltage yield. Contingent upon required load control, the total number of parallel branches is expanded to at least 2. The impacts of solar irradiation and temperature levels are spoken to by two variables picked up. These are changed by dragging the slider pick-up modifications of these blocks named variable solar insolation and temperature. The design of the Zeta converter in the simulation approach and which is implemented in MATLAB is depicted in Fig. 6.

Figure 7 depicts the simulation model of the design and integration of Zeta converter in high gain SSBI. Here, the PVA, ZETA converter, and high gain SSBI are cascaded respectively. The output of the PVA is given as input to the Zeta converter and in the same way, the output of a Zeta converter is given as an input to the high gain SSBI, and the output is fed to the load. The Simulink model of PVA is connected to a Zeta converter. The Simulink model of PVA fed Zeta converter is integrated into high gain SSBI in the Simulink model. This Simulink model is a discrete-time system, and simulation is switched at a frequency of 50 kHz.

4 Results and Discussion

This section presents the output results of the proposed models. In this work, PSIM simulation is utilized to confirm the DCMvoltage conversion proportion. Simulation parameters are as per the following: input voltage (\(V_{\rm g}\)) = 48 V, \(L_{m}\) = 150μH, \({\text{T}}_{s}\) = 20 μs, boost duty cycle (Ðbst) = 0.64, n = 3, and \(R_{{{\text{eq}}}}\) = 4000 Ω. Connecting these variables leads to \(M_{{{\text{cal}}}}\) = 10.96, though mimicked result \(M_{{{\text{sim}}}}\) = 10.58 emphatically supporting the hypothetical desire. CCM–DCM boundary condition is checked by simulation utilizing the accompanying parameters: \(V_{\rm g}\) = 48 V, \(L_{m}\) = 150 μH, \(T_{s}\) = 20 μs, Ðbst = 0.64, and n is 3. The detonated perspective of input current \(I_{\rm g}\) shows that SSBI is in reality at CCM–DCM boundary. The reproduced power output obtained as \(P_{{{\text{ob}}}}\) = 68 W and coordinated the hypothetically expected estimation of \(P_{{{\text{ob}}}}\) = 68.36 W. Figure 8 presents the output waveforms of the input current (\(i_{\rm g} )\) and inductor current (\(i_{{{\text{LO}}}}\)) of SSBI. The decoupling capacitance \(\left( {C_{{{\text{dc}}}} } \right)\) of DC-link capacitor between the inputs and output has been depicted in Fig. 9.

The value of \(C_{{{\text{dc}}}}\) depends on \(P_{{{\text{dc}}}}\) and f at line conditions, \(V_{{{\text{dc}}}}\) and allowed peak-to-peak swell \(\left( {\Delta V} \right)\). The \(C_{{{\text{dc}}}}\) value can be calculated by

Figure 10 depicts the waveforms of the diode current (\({\varvec{I}}_{{\mathbf{D}}}\)), input current (\({\varvec{i}}_{{\varvec{g}}} )\), , inductor peak current (\({\varvec{I}}_{{{\mathbf{pk}}}}\)), and input voltage \(\left( {{\varvec{V}}_{{\varvec{g}}} } \right)\). Figure 11 presents the current waveforms through each switch in SSBI.

The output current \(\left( {{ }I_{{\text{o}}} } \right)\) and output voltage \(\left( { V_{{\text{o}}} } \right)\) waveforms define the differences between input and output waveforms, and they are depicted in Fig. 12. Figure 13 depicts the output power of high gain SSBI.

The waveforms in Fig. 12 represent the nature of output voltage below and above the \(P_{{{\text{omin}}}}\) In Fig. 13, \({\text{P}}_{o}\) is simply above \(P_{{{\text{omin}}}}\) and it does not cause any distortion in the waveform. In Fig. 13, Po is just underneath the beginning of peak-shaving distortion. Parameters utilized as a part of the simulation are \(V_{\rm g}\) = 48 V, \(V_{{{\text{dc}}}}\) = 380 V, and Output current Io = 0.8981A. Figure 14 depicts the operation of Zeta converter when it is integrated with a high gain SSBI.

The variable voltage from the PV array is given to a high-gain SSBI. Then SSBI produces the variable output voltage for each particular level of input voltage from the PV array as the output of the PV array is variable from time to time so to stabilize the output of SSBI, and the Zeta converter is integrated with between PV array and single-stage boosting inverter. When the \(V_{{{\text{pv}}}}\) 38 V of PV array is applied to the Zeta converter then it produces 48 V DC voltage and is applied to the high-gain SSBI as \(V_{\rm g}\) then output voltage \(V_{{\text{o}}}\) is 435 V. In another case, \(V_{{{\text{pv}}}}\) 58 V of PV array is applied to the Zeta converter then it produces 48 V DC voltage and is applied to the high-gain SSBI as \(V_{\rm g}\) then output voltage \(V_{{\text{o}}}\) is 435 V. The output of the Zeta converter is always constant even if the input is above or below the level of output voltage. By this, the variable renewable source output is maintained stable and the converter achieves the high voltage conversion.

5 Conclusions

The integration of Zeta converter in high-gain SSBI for elective vitality age applications has been described in this paper. Here high gain SSBI utilizes a TI to accomplish a high-input voltage step-up and, therefore, permits operation from the low dc input voltage. This paper determines the standards of operation, hypothetical investigation of nonstop, and irregular modes of operation by considering the increase in voltage and current stresses. Here, two remaining solitary models with 48 and 35 V inputs are studied and simulated. Hypothetical discoveries remain in great assertion with simulation and trial comes about. Satisfactory efficiency was accomplished with a low dc input voltage source. The Zeta converter provides positive output power from variable solar irradiance to the SSBI topology. The high gain SSBI provides the upside of high voltage step-up, and it can be additionally expanded by modifying the TI turns proportion.

References

Mthew D, Naidu RC (2020) Investigation of single-stage transformerless buck-boost microinverters. IET Power Electron 13(8):1487–1499

Mumtaz F, Yahaya NZ, Meraj ST, Singh B, Kannan R, Ibrahim O (2021) Review on non-isolated DC-DC converters and their control techniques for renewable energy applications. Ain Shams Eng J

Raj TAB, Ramesh R, Maglin JR, Vaigundamoorthi M, Christopher IW, Gopinath C, Yaashuwanth C (2014) Grid connected solar PV system with SEPIC converter compared with parallel boost converter based MPPT. Int J Photoenergy 2014:1–12

Mohammad N, Quamruzzaman M, Hossain MRT, Alam MR (2013) Parasitic effects on the performance of DC-DC SEPIC in photovoltaic maximum power point tracking applications. Smart Grid Renewable Energy 4(1)

Dogga R, Pathak MK (2019) Recent trends in solar PV inverter topologies. Sol Energy 183:57–73

Trejos A, Gonzalez D, Paja CAR (2012) Modeling of step-up grid-connected photovoltaic systems for control purposes. Energies 5(6):1900–1926

Ankita, Sahooa SK, Sukchaib S, Yaninec FF (2018) Review and comparative study of single-stage inverters for a PV system. Renew Sustainable Energy Rev 91:962–986

Dheesha J, Murthy B (2014) Simulation of micro inverter with high efficiency high step up Dc-Dc converter. Int J Innovat Res Electr Electron Inst Contr Eng 2(2):974–984

Raghavendra KVG, Zeb K, Muthusamy A, Krishna TNV, Kumar SVSVP, Kim DH, Kim MS, Cho HG, Kim HJ (2020) A comprehensive review of DC–DC converter topologies and modulation strategies with recent advances in solar photovoltaic systems. Electronics 9(1)

Ajith A, Thiyagarajan R, Nagalingam A, Ilango R, Purushothaman G (2018) A novel topology using cuk converter in PV microconverter with transformerless injection. Int J Eng Res Technol (IJERT) 6(7):1–7

Çelik Ö, Tan ATA (2018) Overview of micro-inverters as a challenging technology in photovoltaic applications. Renew Sustain Energy Rev 82(3):3191–3206

Zeb K, Uddin W, Khan MA, Ali Z, Ali MU, Christofides N, Kim HJ (2018) A comprehensive review on inverter topologies and control strategies for grid connected photovoltaic system. Renew Sustain Energy Rev 94:1120–1141

Dileep G, Singh SN (2017) Selection of non-isolated DC-DC converters for solar photovoltaic system. Renew Sustain Energy Rev 76:1230–1247

Jana J, Saha H, Bhattacharya KD (2017) A review of inverter topologies for single-phase grid-connected photovoltaic systems. Renew Sustain Energy Rev 72:1256–1270

Abramovitz A, Zhao B, Smedley K (2016) High-gain single-stage boosting inverter for photovoltaic applications. IEEE Trans Power Electron 31(5):3550–3558

Hu H, Harb S, Kutkut NH, Shen ZJ, Batarseh I (2013) A single-stage microinverter without using electrolytic capacitors. IEEE Trans Power Electron 28(6):2677–2687

Narasimha S, Salkuti SR (2018) Design and implementation of smart uninterruptable power supply using battery storage and photovoltaic arrays. Int J Eng Technol 7(3):960–965

Narasimha S, Salkuti SR (2018) Dynamic and hybrid phase shift controller for dual active bridge converter. Int J Eng Technol 7(4):4795–4800

Hu H, Harb S, Fang X, Zhang D, Zhang Q, Shen ZJ, Batarseh I (2012) A three-port flyback for PV microinverter applications with power pulsation decoupling capability. IEEE Trans Power Electron 27(9):3953–3964

Narasimha S, Salkuti SR (2020) An improved closed loop hybrid phase shift controller for dual active bridge converter. Int J Electr Comput Eng 10(2):1169–1178

Chien-Ming W (2004) A novel single-stage full-bridge buck-boost inverter. IEEE Trans Power Electron 19(1):150–159

Abramovitz A, Zhao B, Heydari M, Smedley K (2014) Isolated flyback half-bridge OCC micro-inverter. Proc IEEE energy convers. Congr Expo 2967–2971

Narasimha S, Salkuti SR (2020) Design and operation of closed-loop triple-deck buck-boost converter with high gain soft switching. Int J Power Electron Drive Syst 11(1):523–529

Hu H, Kutkut N, Batarseh I, Harb S, Shen ZJ (2013) A review of power decoupling techniques for microinverters with three different decoupling capacitor locations in PV systems. IEEE Trans Power Electron 28(6):2711–2726

Kim SC, Narasimha S, Salkuti SR (2020) A new multilevel inverter with reduced switch count for renewable power applications. Int J Power Electron Drive Syst 11(4):2145–2153

Zhao B, Abramovitz A, Smedley K (2014) High gain single-stage boosting inverter. IEEE Energy Convers Congress Expos (ECCE) 4257–4261

Acknowledgements

This research work was funded by “Woosong University’s Academic Research Funding—2021”.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Narasimha, S., Salkuti, S.R. (2023). Zeta Converter Interfacing in a Single-Stage Boosting Inverter for Solar Photovoltaic Array. In: Namrata, K., Priyadarshi, N., Bansal, R.C., Kumar, J. (eds) Smart Energy and Advancement in Power Technologies. Lecture Notes in Electrical Engineering, vol 927. Springer, Singapore. https://doi.org/10.1007/978-981-19-4975-3_42

Download citation

DOI: https://doi.org/10.1007/978-981-19-4975-3_42

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-4974-6

Online ISBN: 978-981-19-4975-3

eBook Packages: EnergyEnergy (R0)