Abstract

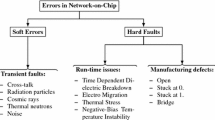

Reliability issue such as soft error due to scaling IC technology, low voltage supply and heavy thermal effects, has caused fault tolerant design be a challenge for NoC(Network-on-Chip). The router is a core element of the NoC, and the virtual channel based on flip-flop which occupies most of the area is the most sensitive element to soft error of the router. Focus on this problem, a dynamic reliable virtual channel architecture is proposed in this paper. It can detect the utilization of the virtual channel to adjust physical configuration to support for no-protection, dual redundancy and TMR (triple modular redundancy) requirements in flexibility. Compared with typical TMR virtual channel design, the synthesis results show that our method can achieve several fault tolerant structures switch with near 3 times resource utilization in ideal case and only 13.8% extra area cost.

Access provided by Autonomous University of Puebla. Download to read the full chapter text

Chapter PDF

Similar content being viewed by others

References

Kim, J., Park, D., et al.: Design and analysis of an NoC architecture from performance, reliability and energy perspective. In: Proceedings of the 2005 ACM Symposium on Architecture for Networking and Communications Systems, pp. 173–182 (2005)

Owens, J.D., et al.: Research challenges for on-chip interconnection networks. IEEE Micro 27(5), 96–108 (2007)

Gratz, P., et al.: Implementation and evaluation of on-chip network architectures. In: Computer Design, ICCD 2006, pp. 477–484 (2006)

Murali, S., et al.: Analysis of error recovery schemes for network on chips. Design & Test of Computers 22(5), 434–442 (2005)

Chang, Y.-C., et al.: On the design and analysis of fault tolerant NoC architecture using spare routers. In: Asia and South Pacific Design Automation Conference, pp. 431–436 (2011)

Hu, J., Marculescu, R.: Dyad: Smart routing for network-on-chip. In: Proceedings of Design Automation Conference (DAC), pp. 260–263 (2004)

Pirretti, M., et al.: Fault tolerant algorithms for network-on-chip interconnect. In: Proc. Int. Symposium Very Large Scale Integrate (ISVLSI), pp. 46–51 (2004)

SHHSU: Design and Implementation of a router for network-on-chip. Department of Electrical Engineering National Cheng Kung University Thesis for Master of Science (2005)

Neishaburi, M.H., et al.: ERAVC: Enhanced reliability aware NoC router. In: Quality Electronic Design (ISQED), pp. 1–6 (2011)

Nirgam: http://nirgam.ecs.soton.ac.uk/

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Wu, P., Fu, Y., Jiang, J. (2013). Design and Implementation of Dynamic Reliable Virtual Channel for Network-on-Chip. In: Xu, W., Xiao, L., Lu, P., Li, J., Zhang, C. (eds) Computer Engineering and Technology. NCCET 2012. Communications in Computer and Information Science, vol 337. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-35898-2_17

Download citation

DOI: https://doi.org/10.1007/978-3-642-35898-2_17

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-35897-5

Online ISBN: 978-3-642-35898-2

eBook Packages: Computer ScienceComputer Science (R0)