Abstract

A novel single-phase nine-level switched-capacitor inverter (9LSCI) with quadruple-boost ability and reducing the component counts is proposed. Only one DC source, nine switches, two diodes and two switched capacitors (SCs) are employed in the basic unit of the proposed topology to realize nine-level output. Due to the passive voltage balancing of each capacitor maintains a constant voltage without additional control. A simple logic-gate-based pulse width-modulation scheme is developed for gating switches of the proposed topology. The working principle of the basic unit topology, the voltage/current stress on the switch, the determination of the capacitance and the simulation and the experiment at 400 W output power are introduced in this paper. In addition, an extended form of the basic unit is provided. A detailed analysis of the proposed topology has been carried out to show the superiority of the proposed converter with respect to the other existing MLI topologies. Various simulations are carried out in Matlab/Simulink R2021b and the feasibility is verified in experiments.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the depletion of fossil energy and the aggravation of environmental pollution, fossil fuel power generation is gradually replaced by renewable energy, such as photovoltaic and wind energy. In renewable energy systems, power electronic circuits play an important role to supply power stably and efficiently.

Multilevel inverter (MLI) has attracted much attention due to its low total harmonic distortion (THD), low switching voltage stress, low switching loss and small output filter. The classical MLI topology includes cascaded H-bridge (CHB) multilevel inverter, neutral point clamped (NPC) multilevel inverter and flying capacitor (FC) multilevel inverter. However, when the number of operation voltage levels exceeds three, some problems such as voltage imbalance and using many components will be caused. Therefore, MLI with fewer components is studied. However, the applicability of such circuits is highly constrained because most of them are buck type. In general, the renewable sources (such as PV) are available in the form of low-voltage supplies, which needs to be boosted to supply power to the load. First scheme is to connect several PV modules in series to form a high voltage input, which has encountered many mismatch problems. Another traditional solution is to add a DC-DC boost converter to the front stage of the traditional MLI. But the complexity is increased, and efficiency is reduced.

The integrated boost technology based on switching capacitor has been widely studied as a new method to solve the above problems [1]. In [2,3,4,5,6,7], voltage balance of capacitor can be achieved without auxiliary method by using SC. But boost capacities of them are poor. Recently, this problem has been solved in [8,9,10,11,12], which provide four times the output voltage gain. In [8, 9], 12 power switches are required, which increases the volume of the inverter and reduces the efficiency. The topology in [10, 11] can achieve the nine-level output by 8 power switches. However, more capacitors and diodes are needed in [10, 11] and the inverter topology in [10] has no scalability.

The scalability is an important performance of MLI. Especially in high-power applications, the switching frequency of inverter is limited due to the limitation of material and technology level of power electronic devices, which leads to the decline of output power quality. There are two solutions in MLI.

The first solution is to increase the switching frequency by reducing the maximum voltage stress on both ends of each switching device in MLI, to achieve high power quality output. However, this method has a high requirement for MLI topology, which requires that the maximum voltage stress at both ends of all high frequency switching devices should not exceed the rated value of safe operation. Moreover, this scheme increases the switching frequency, which increases the switching loss.

Another effective solution is to increase the number of output levels. This scheme has been applied in [13]. Through the nearest level control methods, the output bus voltage presents a step wave, and the number of step waves is determined by the number of levels. The THD of output voltage can be calculated according to the equation provided in [14].

where h is the count of non-negative level and M is the modulation index. It can be concluded from Eq. (1) that when the number of step waves of the output bus voltage is enough, the THD of the output voltage can be reduced to the required value. The outstanding feature of this method is that it does not need to switch the two levels at high frequency due to the output step wave, and the switching frequency is only a few hundred hertz.

Some limitations also exist in the second solution. The increase of output level will inevitably increase the number of components, which will increase the volume of inverter and reduce the efficiency. In [15,16,17,18], the number of output bus voltage levels is increased, and the number of components required is reduced by adding DC sources. However, their applications are limited due to the increasing number of DC power supplies. In [19,20,21], the number of output bus level is increased by using SC in single DC power supply. Unfortunately, a lot of switches, SC and other components are required.

The aim of this article is to cover this specific research gap by introducing a novel 9LSCI inverter and its extended topology suitable for PV power generation that requires boost capability, etc. applications. The base unit inverter that makes up the proposed topology uses fewer components, and it can provide quadruple the output voltage boost function. In addition, the basic cell topology has good scalability, the higher number of output levels can be expanded by adding only a small number of components. The rest of this article is organized as follows. In the second part, the extended topology of 9LSCI basic cell topology, working principle, PD modulation strategy based on logic and the calculation of two switched capacitor parameters are discussed. In the third part, the loss is analyzed. The fourth part gives the comparison between the proposed topology and other topology. The results and analysis are given in the fifth part. Experiments are carried out on the experimental platform based on STM32H750VBT6 to verify its performance. Finally, the conclusion is given in the sixth part.

2 Proposed Circuit

2.1 Circuit Description

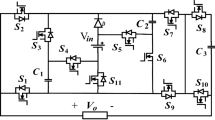

The Basic unit of the proposed topology is demonstrated in Fig. 1. In ideal circumstance, the proposed inverter has nine output voltage levels: ± 4Vin, ± 3Vin, ± 2Vin, ± Vin and 0, and to achieve this goal, only one dc voltage source, two capacitors, two diodes, and nine power switches are needed. To realize nine-level output and four times boost of basic cell topology, the capacitor C1 and C2 are expected to be charged on Vin, 3Vin and 2Vin, respectively. Among the nine switches in the basic unit topology, the switch Si has complementary operation with \({\overline{\text{S}}}_{i} (i = 1,2,3,4)\), which simplifies the switch control. Switch S1 and \({\overline{\text{S}}}_{{1}}\) work in low frequency mode, which further reduces the switching loss.

Further, the number of voltage levels can be increased by cascading multiple such units. The expansion circuit of the basic unit is shown in Fig. 2. The expressions of the number of switches (Nsw), capacitors (NC), diodes (Nd) and level (N) are given.

The relationship between the number of switches, capacitors, diodes and the number of levels in the extended circuit can be obtained from Eq. (2). According to their relationship, the number of output voltage (vbus) levels increases by 4 with the addition of two switches, a capacitor and a power diode. Its expanded performance is excellent.

The switching states of the proposed topology and the corresponding current paths for each of the output voltage levels are shown in Table 1 and Fig. 3, respectively. The entry “1 =” indicates that a particular switch is ON and “0” indicates the OFF condition.

2.2 Description of Each Voltage Level

For the proposed nine-level inverter, switching patterns are listed in Table 1, including the states of the capacitors, and to have a quick and better understanding, current paths in the positive half cycle are demonstrated in Fig. 3a–e for each case, respectively. Assumptions have been given: all the power devices are ideal, the on-state resistances and forward voltage drops of power devices are considered as zero, the capacitance of the two capacitors is large enough, and the proposed inverter has already entered steady states. To make the concept more accessible, the capacitor voltages are assumed to be constant at VC1 = Vin and VC2 = 2Vin.

State A: it can be seen from Table 1 and Fig. 3a that in state A, capacitors C1 and C2 discharge in series with power supply Vin, and they share the same discharge current. At this point, the bus voltage (vbus) is

State B: in state B shown in Fig. 3b, capacitor C1 is charged in parallel with power supply Vin, so capacitor C1 is equal to power supply Vin. Capacitor C2 is discharged in series with power supply Vin. At this point, the bus voltage vbus is

State C: in State C shown in Fig. 3c, capacitor C1 is connected in series with power supply Vin to supply power to load and capacitor C2. At this point, the bus voltage vbus is

State D: in state D shown in Fig. 3d, capacitor C1 is charged in parallel with power supply Vin, which satisfies formula (5). Capacitor C2 does not participate in the charging and discharging process, and it maintains the voltage state at the previous moment. At this point, the bus voltage vbus is

State E: in state E shown in Fig. 3e, capacitor C2 is charged by capacitor C1 and power supply Vin, which satisfies formula (7). At this point, the bus voltage vbus is

Actually, the capacitor C1 is directly charged in parallel by the input DC source Vin, and the capacitor C2 is charged in parallel by the capacitor C1 inputting the DC source Vin in series and then in parallel. The charging or discharging states of capacitors C1 and C2 in each level state are shown in Table 1. After each capacitor is charged, it is equivalent to an independent DC source, and the voltage drop across the capacitor due to discharge is a slow process with small voltage fluctuations. Therefore, it is assumed that VC1 = Vin and VC2 = 2Vin are constant.

Overall, the proposed nine-level inverter is equipped with the self-voltage balancing ability, thus simplifying the driving circuits and modulation algorithms. When the load is inductive, the current will flow in the opposite direction, and Fig. 3a–e show the reverse current paths for each voltage level in the positive half cycle. It can be found that the output voltage levels remain the same regardless of the directions of the load current. Since the proposed inverter has a symmetric operation, it can be considered for the other four states in negative half cycle as well.

2.3 Control Strategy

Multi-Carrier PWM has many modulation methods, such as level-shift pulse width modulation (LS-PWM) [22, 23] and phase-shift pulse width modulation (PS-PWM) [24]. However, for MLI with N levels, both LS-PWM and PS-PWM need (N − 1) carriers, and more complex logic control strategies are required.

An optimized multicarrier phase disposition (PD) pulse width modulation (PWM) method is proposed in [25] to simplify the modulation strategy, and it is adopted for the proposed topology. As shown in Fig. 4a, the carrier voltage levels of e1, e2, e3 and e4 have the same phase and amplitude, but the horizontal displacement difference between adjacent levels is AC. Sinusoidal modulated signal waveforms es = Arefsin2πfreft share the same time axis with these carriers. Aref is the amplitude of the sine wave |Aref|< 4Ac, fref is the frequency of the sine wave.

The amplitude of the output voltage waveform Vo is determined by the ratio of the amplitude of the reference sinusoidal signal waveform es to the amplitude of the carrier. Therefore, the modulation index m is defined as:

According to Table 1, the simple logic circuits or a lookup table method of the controller can be used for the PWM signals of the switches.

As shown in Fig. 4b, according to the relationship between es and ek (k = 1,2,3,4), four positive level states and one fundamental level can be obtained, and then each switch can be controlled by simple logic control.

2.4 Determination of Capacitances

The peak charging and discharging currents of SC are depended on the voltage ripple at both ends of the capacitor. The high voltage ripple of SC will lead to the decrease of power conversion efficiency. Therefore, through the proper design of the capacitor, the voltage ripple of the floating capacitor can be kept low, and the two peak currents can be reduced to an acceptable value, the efficiency can also be improved. According [26], each capacitance is calculated from their voltage ripple.

For capacitor C1, voltage ripple can be maintained at a small value by a small capacitance. Because capacitor C1 does not discharge in two continuous states, energy can be supplemented in each switching cycle.

It is known from [9] that when the capacitor voltage VC2 is less than Vin + VC1, the voltage ripple of capacitor C1 occurs, and the inverter is in the state of Fig. 3c. Capacitor C1 discharges and capacitor C2 is charged. In this state, the current flowing through capacitor C1 is equal to the output current plus the current of capacitor C2 charging circuit, which is expressed as

iC2c is the charging current of capacitor C2, which can be expressed as

where rC1 and rC2 are the equivalent series resistance (ESR) of the capacitors C1 and C2. rDS is ON resistance of the switch. rDD is ON resistance of the diode. io(t) is the output current, which can be expressed as

Among them, Ibus represents the peak value of the output sinusoidal current; φ represents the phase difference between the output voltage and the output current. When the capacitor C1 is in the period from t2m − 1 to t2m as shown in Fig. 5, the discharge current flowing through the capacitor C1 is shown in Eq. (11), and the discharge amount of the capacitor C1 at this time is expressed as

Therefore, the total discharge of capacitor C1 during the period t1 to t2m is expressed as

When capacitor C1 is directly connected in parallel with the power supply, the inverter is in the state of Fig. 3b or Fig. 3d. In the state, the current flowing through capacitor C1 is

According to Eq. (16), in the time period of t2m − 1 and t2m − 2, C1 is charged, which is expressed as

The total charging amount Q1c is given as

Therefore, through Eqs. (15) and (18), the difference between the discharge amount and the charge amount of capacitor C1 from t1 to t2m is

Finally, taking the allowable voltage ripple ΔVC1 into consideration, the minimum capacitance should meet the following formula

The same does not apply to C2, which continuously discharges to the output over the time span (ta – tb), as shown in Fig. 4a. In this state, the current flowing through the capacitor C2 is consistent with the output current. Therefore, the discharge amount of capacitor C2 in this period is

Considering the voltage ripple ΔVC2 of capacitor C2, the minimum value of capacitor C2 should be

2.5 Voltage/Current Stresses on Switches

From the five states in Fig. 3, voltage stresses (Vsi, i = 1–5) of the nine switches are found as

It should be noted that the voltage stresses of Si and \({\overline{\text{S}}}_{i} \left( {i = {1},{2},{3,4}} \right)\) are the same, but the current stresses flowing through them are different.

It can be seen from Fig. 3 that the maximum current stress of switches S1, S2 and \({\overline{\text{S}}}_{i} \left( {i = {1},{2},{3}} \right)\) is the output current Ibus. The maximum current flowing through the switch S3 occurs in the State C shown in Fig. 3, which is consistent with the discharge current flowing through the capacitor C1 as ic1d(t). In state A and State C, the current flowing through switch S4 is io(t) and ic1d(t), respectively. Therefore, the maximum current stress of switch S4 is Ibus or iC1d,max. Where iC1d,max is the maximum discharge current of capacitor C1 in state C. The difference is that the switch \({\overline{\text{S}}}_{4}\) is only turned on when the capacitor C1 is charged, and it is directly connected in series with C1.

Therefore, the current stress is iC1c(t) according to Eq. (16). Similarly, the switch S5 is only turned on when the capacitor C2 is charged, and it is directly connected in series with C2. The current stress iC2c(t) is obtained from Eq. (12).

3 Loss Analysis

Three types of losses are considered for the switched capacitors converters, which include capacitors conduction losses (PC), switching losses (PS), and capacitors charging losses (PRip).

3.1 Calculation of Conduction Losses

Conduction losses for the power switch and power diode is obtained from the following equations [27]:

where PC,sw(t) and PC,D(t) indicates the conduction loss of the switch tube and diode respectively. Von and ron is the voltage drop and the on resistance of the device in the on state. iavg and irms represents the RSM current and average current flowing through the switch tube and diode respectively.

Each level state shown in Fig. 3 corresponds to a discharge path, so there is a corresponding conduction loss on the on path. By calculating the conduction loss of the level in each state, the total conduction loss can be obtained in a whole period. The conduction loss can be obtained by the following formula:

In the state E shown in Fig. 3, the currents of load circuit switch and charging circuit of capacitor C2 are small, so the conduction loss in this state is ignored. It is worth noting that the conduction loss in the four states of negative half period is symmetrical with that of positive half period, so the total conduction loss can be calculated as:

3.2 Calculation of Switching Losses

One of the most important sources of the power loss is switching losses (PS) which are generated due to switching delays that are intrinsic to the semiconductor devices. Because of the different delay time of switching on and off, the loss of each switch can be divided into on loss (Psw,i(on)) and off loss (Psw,i(off)) in one basic frequency period. The losses of the active switches during the turning ON and OFF are obtained as following equations [3]:

where, Nsw,i(on) and Nsw,i(off) are the number of times that the switch i is turned on and off in the fundamental frequency period. ton and toff are the delay time for the switch to turn on and turn off completely. VS,i and IS,i can be approximately considered as the voltage stress and current stress before the switch is turned on and off respectively. The on loss (\(\overline{P}_{sw,i(on)}\)) of switch \({\overline{\text{S}}}_{i} (i = 1,2,3,4)\) and off loss (\(\overline{P}_{sw,i(off)}\)) is similar to the above formula.

Further, Nsw,i(on) and Nsw,i(off) are equal in one fundamental frequency period and expressed as Nsw,i. Since the operation of switch Si and switch \({\overline{\text{S}}}_{i} (i = 1,2,3,4)\) are complementary, the number of times they on and off is considered equal. The switching losses of S1 and \({\overline{\text{S}}}_{1}\) operating at fundamental frequency are neglected. \(N_{sw,i(on)}\) and \(N_{sw,i(off)}\) for switches of each module is calculated as following equations:

Therefore, the total switching loss is

3.3 Calculation of Ripple Losses of Capacitors

The ripple losses are caused by the parallel connection of capacitors with input DC sources for charging the capacitors. The voltage ripple of capacitor is calculated by (20) and (22). Therefore, capacitors ripple losses are obtained from the following equation [28]:

where Ck and ΔVCk represent the capacity and voltage ripple of capacitor k(k = 1,2) respectively.

Then, using (30), (34), and (35), the total losses of proposed topology (Ptot) will be

Finally, the efficiency can be achieved as

4 Comparative Study

In order to evaluate the advantages and disadvantages, the comparisons between the proposed topology and other nine-level inverters reported recently are given. Table 2 shows the comparison of the key characteristics between the nine-level inverter introduced in this paper and the nine-level inverter recently reported. According to the number of power switches (NSW), the number of input DC sources (NDC), the number of independent diodes (Nd), the number of capacitors (Ncap), the output voltage gain and the scalability of the topology are compared.

The three traditional types of nine-level inverters have good scalability, and with the increase of the number of levels, the output power quality also increases. Unfortunately, a large number of components are required and they do not have boost capability.

Compared with the nine-level topology reported in [2,3,4,5,6,7,8,9], the basic unit of the proposed topology has more advantages in the number of components or output performance. For example, the basic unit of the proposed topology in this paper has the same number of components as the topology reported in [5, 6]. However, the proposed topology has more advantages in terms of output voltage gain and scalability.

The nine-level topologies reported in [10, 11] have good output voltage gain, and the number of switches is less than the proposed topology. However, the proposed topology has obvious advantages in terms of the number of independent diodes and capacitors. Compared with the nine-level topology reported in [12], the proposed topology has one more diode, but the topology reported in [12] has no scalability.

The single source extension of the proposed topology has been compared with several single source extension circuits introduced in other literatures. As shown in Fig. 6, the curves of the number of switches, driving circuits and capacitors with the increase of the level are shown respectively. Figure 6a shows the curve of the number of switches varies with the number of levels. When the number of levels exceeds five, the proposed topology needs fewer switches and has obvious advantages. Figure 6b shows the relationship between the required gate drive and the number of levels. It is worth noting that, except for the inconsistency of the number of driving circuits and switches in the topology introduced in [4], the number of driving circuits in other expansion circuits compared is consistent with their respective number of switches. Figure 6c shows the curve of the number of capacitors varies with the number of levels. The proposed topology also has advantages.

5 Results and Analysis

5.1 Simulation Results

Simulink simulations are carried out to verify the performance of the proposed nine-level inverter. The simulation model is shown in Fig. 7, and the simulation parameters are shown in Table 3. DC input is 50 V, which leads to 50 V and 100 V at C1 and C2 of SC capacitor. The peak value of nine-level output voltage is 200 V. According to the data sheet of IXFH80N65X2, the conduction resistance and drain-source capacitance of MOSFET are determined. According to the data sheet of DSEI60, the conduction resistance rD1-rD2 and the forward conduction voltage drop of independent diodes D1 − D2 are determined.

Figure 8a and b show the simulation waveforms of bus voltage, output voltage and output current under pure resistive load Z1 and inductive load Z2 respectively. The DC voltages at both ends of switching capacitor voltage C1 and C2 under inductive load Z2 are shown in Fig. 8c. The simulation waveform is consistent with the analysis. The FFT analysis of bus voltage vbus under load Z2 is shown in Fig. 8d. Compared with the fundamental frequency component, the odd order harmonics are greatly attenuated, and the frequency of the fundamental frequency component is the same as the output voltage. That is to say, the low THD is achieved by the proposed nine-level inverter with fewer components. On the other hand, the THD of bus voltage vbus shown in Fig. 8d is 16.89%, which satisfies another THD calculation expression described in [11].

When the modulation index M is 0.9, the voltage THD is estimated to be 16.03%, which is in good agreement with the simulation results. In fact, formula (1) and formula (38) are not contradictory, because they serve different objects. Equation (1) is for the case that the output of bus voltage vbus is a step wave, while Eq. (38) is for the case that bus voltage vbus switches quickly under two levels.

The dynamic waveform of modulation index M of the proposed basic cell topology under inductive load Z2 is given in Fig. 9a. 0.2, 0.4, 0.6–1, the corresponding THD of the output voltage is 5.29%, 2.76%, 1.68%, and 1.24%, respectively, and the power quality of output voltage and current waveform will be improved. Moreover, when the modulation index M changes dynamically, its dynamic performance does not decrease.

The key waveforms of the proposed basic cell topology when load is suddenly added are shown in Fig. 9b. Figure 9b is the waveform of bus voltage vbus, output voltage vout and output current iout from no-load sudden change to inductive load Z2. The output voltage is stable, and the output current can be smoothly transited under sudden load addition.

The curve of output efficiency changing with power is shown in Fig. 10 when the output load is reduced from 320 to 40 Ω. When the output power Po = 115 W, the maximum power conversion efficiency is 97.2%.

5.2 Experiment Analysis

In order to further verify the feasibility of the proposed basic unit nine-level SC inverter, the experimental prototype shown in Fig. 11 is realized. The experimental circuit parameters and equipment specifications are shown in Table 4. The system is controlled by STM32H750VBt6 single chip microcomputer. The DC voltage of the system is 50 V and the modulation index is 0.9. The load is 45 Ω. The filter inductor is self-winding, the inductance is 1.1mH, and the filter capacitor is 8 μF. The switching frequency is 10 kHz and the frequency of output fundamental is 50 Hz.

The experimental results of the proposed basic cell nine-level SC topology are shown in Fig. 2. Under pure resistive load, the phase of output voltage and current are the same, as shown in Fig. 12a. Figure 12b shows the DC voltage waveforms at both end of two SC in the main circuit. The experimental results are consistent with the simulation, and the fluctuation of voltage is small.

The experimental results when the modulation index changes dynamically are shown in Fig. 13. In Fig. 13a, when the modulation index increases from 0.2 to 0.6, the output bus voltage is transited from 3-level output to 7-level output, and the dynamic performance of the transition is good. Figure 13b shows the dynamic change of modulation index from 0.9 to 0.4. At this time, the corresponding level of output bus voltage is transited from 9-level output to 5-level output. When the output level is decreased, the output waveform is still stable. Figure 14 shows the experimental results of the proposed basic cell nine-level SC inverter under sudden load change. When the load is suddenly added, the experimental waveform is consistent with the simulation. It should be pointed out that the parameters of the simulation model are assumed to be known. For the black-box inverter system in practical applications, that is, when the parameters of the components in the inverter are unknown, these unknown parameters are expected to be estimated and determined by some identification algorithms [29,30,31,32,33,34] to make them to be white-box, such as the least squares algorithm [35,36,37,38,39,40] and the gradient algorithm [41,42,43,44,45,46,47,48], etc. The combination of recognition algorithm and power electronics has broad application prospects.

6 Conclusions

In this paper, a novel switched capacitor nine-level inverter with four times boost capability is proposed. The proposed topology is highly scalable, which can increase the output voltage by four levels and four times the output voltage gain when every two switches and a small number of auxiliary passive components are added to the base unit of the proposed topology. However, an H-bridge is required in the proposed topology, which increases the output voltage stress. The high scalability of the proposed topology can reduce the influence of this disadvantage. When the number of the output level of the expansion circuit is enough, the switching frequency can be effectively reduced by using the output step wave. This paper presents extended form of the basic unit, and introduces the working principle, modulation method, switched capacitor parameter calculation, loss analysis, comparison, simulation and experimental results of the basic unit as a conventional nine level inverter. The capacitor in the proposed topology has the capacity of capacitor voltage self-balancing, and the PD modulation algorithm based on logic is used to simplify the complexity of the modulation circuit. Compared with the existing topology, the superiority of the proposed inverter is proved. All the advantages and feasibility of the proposed topology are evaluated through the simulation model. An experimental prototype with rated power of 400 W is built, and the experimental dynamic waveforms under different conditions are described. The results show that the proposed inverter has good dynamic performance as a switching power supply. It is worth noting that the topology proposed in this paper still needs to be improved. For example, the mathematical model study of the proposed topology has not been given. Some advanced modeling methods for linear [49,50,51,52,53,54,55] and nonlinear [56,57,58,59,60] systems are helpful for the establishment of a more accurate mathematical model of the proposed structure, which in turn can be applied to other fields.

References

He L, Cheng C (2016) A flying-capacitor-clamped five-level inverter based on bridge modular switched-capacitor topology. IEEE Trans Industr Electron 63(12):7814–7822

Taghvaie A, Adabi J, Rezanejad M (2018) A self-balanced step-up multilevel inverter based on switched-capacitor structure. IEEE Trans Power Electron 33(1):199–209

Liu J, Cheng KWE, Ye Y (2014) A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system. IEEE Trans Power Electron 29(8):4219–4230

Ali JSM, Kumar V (2018) Compact switched capacitor multilevel inverter (CSCMLI) with self-voltage balancing and boosting ability. IEEE Trans Power Electron 34(5):4009–4013

Liu J, Wu J, Zeng J, Guo H (2017) A novel nine-level inverter employing one voltage source and reduced components as high-frequency ac power source. IEEE Trans Power Electron 32(4):2939–2947

Barzegarkhoo R et al (2022) Nine-level nine-switch common-ground switched-capacitor inverter suitable for high-frequency AC-microgrid applications. IEEE Trans Power Electron 37(5):6132–6143

Naik BS et al (2020) A hybrid nine-level inverter topology with boosting capability and reduced component count. IEEE Trans Circuits Syst II Express Briefs 68(1):316–320

Sandeep N, Ali JSM, Yaragatti UR, Vijayakumar K (2019) Switched-capacitor-based quadruple boost nine-level inverter. IEEE Trans Power Electron 34(8):7147–7150

Nakagawa Y, Koizumi H (2019) A boost-type nine-level switched capacitor inverter. IEEE Trans Power Electron 34(7):6522–6532

Lin JAW, Wu J, Zeng J (2019) A novel nine-level quadruple boost inverter with inductive-load ability. IEEE Trans Power Electron 34(54):4014–4018

Saeedian M, Adabi Firouzjaee ME, Hosseini SM, Adabi J, Pouresmaeil E (2019) A novel step-up single source multilevel inverter: topology, operating principle and modulation. IEEE Trans Power Electron. https://doi.org/10.1109/TPEL.2018.2848359

Bana PR et al (2020) A novel nine-level boost type multilevel inverter with inductive ability for photovoltaic system. In: 2020 IEEE industry applications society annual meeting, pp 1–6. https://doi.org/10.1109/IAS44978.2020.9334916

Memon MA, Mekhilef S, Mubin M (2018) Selective harmonic elimination in multilevel inverter using hybrid APSO algorithm. IET Power Electron 11(10):1673–1680

Ruderman A (2015) About voltage total harmonic distortion for single- and three-phase multilevel inverters. IEEE Trans Ind Electron 62(3):1548–1551

Chen Q et al (2020) New type single-supply four-switch five-level inverter with frequency multiplication capability. IEEE Access 8:203347–203357

Siddique MD, Mekhilef S, Shah NM, Memon MA (2019) Optimal design of a new cascaded multilevel inverter topology with reduced switch count. IEEE Access 7:24498–24510

Samadaei E, Sheikholeslami A, Gholamian SA, Adabi J (2018) A square T-type (ST-Type) module for asymmetrical multilevel inverters. IEEE Trans Power Electron 33(2):987–996

Zeeshan Sarwer MD, Siddique Atif Iqbal, Sarwar Adil, Mekhilef S (2020) An improved asymmetrical multilevel inverter topology with reduced semiconductor. Int Trans Electr Energy Syst. https://doi.org/10.1002/2050-7038.12587

Siddique MD, Mekhilef S, Shah NM et al (2020) Switched-capacitor-based boost multilevel inverter topology with higher voltage gain. IET Power Electron. https://doi.org/10.1049/iet-pel.2020.0446

Siddique MD, Reddy BP, Iqbal A et al (2020) Reduced switch count-based N-level boost inverter topology for higher voltage gain. IET Power Electron. https://doi.org/10.1049/iet-pel.2020.0359

Sandeep N, Ali JSM, Yaragatti UR, Vijayakumar K (2019) A self-balancing five-level boosting inverter with reduced components. IEEE Trans Power Electron 34(7):6020–6024

McGrath BP, Holmes DG (2002) Multicarrier PWM strategies for multilevel inverters. IEEE Trans Ind Electron 49(4):858–867

Odeh CI, Lewicki A, Morawiec M (2021) A single-carrier-based pulse width modulation template for cascaded H-bridge multilevel inverters. IEEE Access 9:42182–42191

Franquelo LG, Rodriguez J, Leon J, Kouro S, Portillo R, Prats MAM (2008) The age of multilevel converters arrives. IEEE Ind Electron Mag 2(2):28–39

Hinago Y, Koizumi H (2012) A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans Ind Electron 59(2):878–887

Chen M, Yang Y, Blaabjerg F (2021) A six-switch seven-level triple-boost inverter. IEEE Trans Power Electron 36(2):1225–1230

Sadigh AK, Dargahi V, Corzine KA (2016) Analytical determination of conduction and switching power losses in flying-capacitor-based active neutral-point-clamped multilevel converter. IEEE Trans Power Electron 31(8):5473–5494

Babaei E, Gowgani SS (2014) Hybrid multilevel inverter using switched capacitor units. IEEE Trans Ind Electron 61(9):4614–4621

Ding F, Chen T (2014) Combined parameter and output estimation of dual-rate systems using an auxiliary model. Automatica 40(10):1739–1748

Ding F, Liu YJ, Bao B (2011) Gradient based and least squares based iterative estimation algorithms for multi-input multi-output systems. Proc Inst Mech Eng Part I J Syst Control Eng 226(1):43–55

Ding F (2013) Coupled-least-squares identification for multivariable systems. IET Control Theory Appl 7(1):68–79

Zhou YH (2020) Modeling nonlinear processes using the radial basis function-based state-dependent autoregressive models. IEEE Signal Process Lett 27:1600–1604

Zhou YH, Zhang X (2021) Partially-coupled nonlinear parameter optimization algorithm for a class of multivariate hybrid models. Appl Math Comput 414:126663

Zhou YH, Zhang X (2021) Hierarchical estimation approach for RBF-AR models with regression weights based on the increasing data length. IEEE Trans Circuits Syst II Express Briefs 68(12):3597–3601

Xu L (2021) Separable multi-innovation Newton iterative modeling algorithm for multi-frequency signals based on the sliding measurement window. Circuits Syst Signal Process 41(2):805–830

Ding F, Liu XG, Chu J (2013) Gradient-based and least-squares-based iterative algorithms for Hammerstein systems using the hierarchical identification principle. IET Control Theory Appl 7(2):176–184

Ding F (2014) Combined state and least squares parameter estimation algorithms for dynamic systems. Appl Math Modell 38(1):403–412

Ding J, Liu G (2014) Hierarchical least squares identification for linear SISO systems with dual-rate sampled-data. IEEE Trans Autom Control 56(11):2677–2683

Liu YJ, Shi Y (2014) An efficient hierarchical identification method for general dual-rate sampled-data systems. Automatica 50(3):962–970

Wang YJ (2016) Novel data filtering based parameter identification for multiple-input multiple-output systems using the auxiliary model. Automatica 71:308–313

Ding F, Chen T (2005) Parameter estimation of dual-rate stochastic systems by using an output error method. IEEE Trans Automat Control 50(9):1436–1441

Ding F, Liu G, Liu X (2010) Partially coupled stochastic gradient identification methods for non-uniformly sampled systems. IEEE Trans Autom Control 55(8):1976–1981

Ding F, Liu G, Liu X (2011) Parameter estimation with scarce measurements. Automatica 47(8):1646–1655

Zhang X (2022) Optimal adaptive filtering algorithm by using the fractional-order derivative. IEEE Signal Process Lett 29:399–403

Xu L (2022) Separable Newton recursive estimation method through system responses based on dynamically discrete measurements with increasing data length. Int J Control Autom Syst 20(2):432–443

Xu L, Yang E (2020) Auxiliary model multiinnovation stochastic gradient parameter estimation methods for nonlinear sandwich systems. Int J Robust Nonlinear Control 31(1):148–165

Xu L, Zhu Q (2022) Separable synchronous multi-innovation gradient-based iterative signal modeling from on-line measurements. IEEE Trans Instrum Meas 71:6501313

Xu L, Chen FY, Hayat T (2021) Hierarchical recursive signal modeling for multi-frequency signals based on discrete measured data. Int J Adapt Control Signal Process 35(5):676–693

Xu L, Zhu Q (2021) Decomposition strategy-based hierarchical least mean square algorithm for control systems from the impulse responses. Int J Syst Sci 52(9):1806–1821

Zhang X (2021) Hierarchical parameter and state estimation for bilinear systems. Int J Syst Sci 51(2):275–290

Zhang X, Yang E (2019) State estimation for bilinear systems through minimizing the covariance matrix of the state estimation errors. Int J Adapt Control Signal Process 33(7):1157–1173

Zhang X (2020) Adaptive parameter estimation for a general dynamical system with unknown states. Int J Robust Nonlinear Control 30(4):1351–1372

Zhang X, Xu L (2020) Recursive parameter estimation methods and convergence analysis for a special class of nonlinear systems. Int J Robust Nonlinear Control 30(4):1373–1393

Zhang X, Liu Q, Hayat T (2020) Recursive identification of bilinear time-delay systems through the redundant rule. J Frankl Inst 357(1):726–747

Zhang X, Yang E (2019) Highly computationally efficient state filter based on the delta operator. Int J Adapt Control Signal Process 33(6):875–889

Zhang X, Hayat T (2018) Combined state and parameter estimation for a bilinear state space system with moving average noise. J Frankl Inst 355(6):3079–3103

Zhang X, Hayat T (2017) Recursive parameter identification of the dynamical models for bilinear state space systems. Nonlinear Dyn 89(4):2415–2429

Wang H, Fan H (2021) Complex dynamics of a four-dimensional circuit system. Int J Bifurc Chaos 31(14):2150208

Wang H, Ke G, Fan H (2022) Multitudinous potential hidden Lorenz-like attractors coined. Eur Phys J Spec Top. https://doi.org/10.1140/epjs/s11734-021-00423-3

Xu CJ, Xu HC, Su HS (2022) Adaptive bipartite consensus of competitive linear multi-agent systems with asynchronous intermittent communication. Int J Robust Nonlinear Control. https://doi.org/10.1002/rnc.6086

Acknowledgements

This work was supported by the Key Laboratory Open Foundation of Hubei Province for Solar Power Generation and Energy Storage Control (No. HBSEES201902) and National Natural Science Foundation of China (No. 61571182).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Pan, J., Chen, Q., Xiong, J. et al. A Novel Quadruple-Boost Nine-Level Switched-Capacitor Inverter. J. Electr. Eng. Technol. 18, 467–480 (2023). https://doi.org/10.1007/s42835-022-01130-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-022-01130-2