Abstract

In this paper, a novel low power and high write margin Darlington based NCNTFET Darlington 8T SRAM cell is proposed. The power consumption of the proposed Darlington SRAM cell is compared with that of conventional 6T CNTFET and conventional 8T CNTFET SRAM cells. The power consumption of the proposed Darlington SRAM cells is very less as compared to that of conventional 6T and 8T CNTFET SRAM cells for all write, hold, and read operations. The write static noise margin (WSNM) of the proposed NCNTFET Darlington 8T cell is found to increase by 70.83% than that of both conventional 6T and 8T CNTFET SRAM cell. Effect of CNTFET parameters such as chiral vectors (m,n), gate oxide thickness (Hox), dielectric constant of gate oxide material (Kox), temperature, pitch value, number of carbon nano tubes (CNTs) and supply voltage (VDD), on the power performance, drain current (ID) and drain to source voltage (VDS) of the novel proposed Darlington SRAM cell are investigated. The write, hold, and read power consumption of proposed NCNTFET Darlington 8T SRAM cell is compared with that of some of the existing SRAM cells. The simulation is carried out using Stanford University 32 nm CNTFET model.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

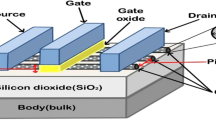

Moore’s law states that in every eighteen months, the number of transistors in an integrated circuit is getting doubled. The International Technology Roadmap for Semiconductors (ITRS) has predicted that the silicon (Si) has reached its scaling limits [1]. The minimization of the size of metal oxide semiconductor field-effect transistor (MOSFET) below 10 nm has several demerits such as high leakage power, quantum effects, PVT variation, etc. Hence, electronics engineers are in need to search for the best alternative device instead of MOS transistors [2]. Carbon Nano Tube Field Effect Transistor (CNTFET) is one of the promising semiconductor devices to overcome all the limitations of Si technology at nanoscale regime. CNTFET has many favourable electrical characteristics like high ON to OFF current ratio, ballistic transport, good transconductance, low power consumption, and least PVT variation [3].

1.1 Carbon Nano Tube Field Effect Transistor

CNTFET is obtained by replacing the conducting channel of MOSFET by a carbon nano tube (CNT) (Fig. 1). CNT is a graphene sheet rolled up in cylindrical form [4]. CNTFETs are classified into two categories based on number of layers of graphene. One is single walled CNT (SWCNT) and another one is multi-walled CNTs (MWCNTs) [5]. The structure of SWCNTs and MWCNTs is shown in Fig. 2. The electrical characteristics of CNT are determined by chiral vector or chirality of the CNT. Figure 3 shows the honeycomb structure of graphene sheet and various types of CNTs. The width of CNTFET (WCNT) is determined by [1]

Here, \(N\) is the number of CNTs used, \(S\) is the distance between parallel CNTs also called pitch value of CNTFET, \({D}_{CNT}\) -diameter of CNTs.

The chiral vectors (m, n), the threshold voltage of CNTFET (Vth), and the diameter of the CNT (DCNT) are related by the following expression [1].

Here a—carbon atomic distance, \(V_{\pi }\)—carbon bond energy (\(V_{\pi }\) = 3.033 eV) and e-charge of electron [1].

Leakage power and the power delay product of CNTFET based circuits are seventy-five and hundred times lower than that of MOSFET based circuits respectively. The effect of variation of process, voltage, and temperature on CNTFET is much lower as compared with that of MOSFET device [6, 7]. The chiral vectors are directly related to DCNT and inversely proportional to the Vth. Hence, increase in m and n values increases the diameter of CNT, which in turn increases the amount of current flow in the CNTFET. Therefore, the power consumption is also increased. Increasing chiral vectors, decreases the threshold voltage of the CNTFET. At high values of chiral vectors, a minimum gate voltage is sufficient to switch ON the CNTFET [7].

Quantum capacitance determines the delay in a MOSFET and is found to increase with gate voltage but in the case of CNTFET, the quantum capacitance decreases with increasing gate voltage above 0.5 V. The threshold voltage of CNTFET is inversely proportional to the temperature. Increase of temperature from 27 °C to 227 °C decreases the threshold voltage of the CNTFET by a margin of 4.6% only [8, 9]. Variations in gate oxide thickness affects drain current capability of CNTFET. The decrease in gate insulator thickness, decreases the threshold voltage of CNTFET and increases the gate leakage current. This, in-turn increases the power consumption of the circuit [5]. Dielectric constant is directly proportional to gate capacitance, thus increase in the value of dielectric constant decreases the threshold voltage of CNTFET [10]. Hence, the power consumption of CNTFET is increased with increasing of dielectric constant value [11]. The dielectric constant (Kox) of silicon dioxide (SiO2), hafnium oxide (HfO2), and titanium oxide (TiO2) are 3.9, 16, and 55 respectively.

Drain current (ID) as a function of drain to source voltage (VDS) is calculated for various oxide thickness, dielectric constant, chiral vectors, temperature, number of CNTs, and pitch value. Figures 4, 5, 6, 7, 8 and 9 are showing the variation drain current (ID) and drain to source voltage (VDS) of CNTFET.

1.2 Static Random-Access Memory

SRAM is one of the essential building blocks of digital very large scale integrated (VLSI) circuits and it occupies 90% of total chip area. SRAMs are the most important source of static power consumption. Hence, design of SRAM cell has to be done in consideration with low power consumption, high speed, and smaller chip area. SRAM cells designed with CNTFET are being proposed for achieving low power and high speed operations [12]. The read noise margin of conventional 6T (Fig. 10) SRAM cell is reduced by using same path for both read and write operations [13]. In conventional 8T SRAM cell (Fig. 11), a separate read path is used, which increases read stability of the memory cell as compared with that of the conventional 6T SRAM cell. The conventional 8T SRAM cell consumes more power during the read operation. This is due to current leakage in the Read Bit Line (RBL) [14]. In conventional 10T SRAM cell, stacked access transistors are used to reduce the sub-threshold leakage in bit lines. The differential read method improves the Read static Noise Margin (RSNM) and decreases the radiation effect on the storage nodes [15]. Fine grained bit line stacking technique based 8T SRAM cell reduces read port leakage current of 8T bit-cell. The read and write power consumption of fine-grained bit line stacking technique based 8T SRAM cell has significantly minimized by adopting the Bank-level Word Line (WL) driver power-gating method. The leakage power of an SRAM cell is reduced by using the floating write drive technique. Hence, Fine grained bit line stacking technique based 8T SRAM cell achieves 75% leakage power reduction as compared to that of conventional 8T SRAM cell [16]. The 8T SRAM cell proposed in [17] has virtual ground. This virtual ground weakens the positive feedback of the circuit which in turn increases the WSNM of the SRAM cell. This proposed cell does not require any precharging circuit for the read operation. In the proposed cell, the storage node is separated from the read path. Hence, RSNM of the circuit is also improved. The write, hold and read currents of the proposed SRAM cell are reduced and speed is increased as compared with that of conventional 6T SRAM cell[17]. The 8T SRAM cell with vertical read word line (RWL) and selective dual split power line offers better power performance than the conventional 6T SRAM cell. The dynamic power consumption of the proposed cell is drastically reduced due to vertical read word line. The vertical read word line selects only particular read bit lines during the read operation. This, in turn controls the charging and discharging of selected bit lines. Hence, the dynamic power consumption of the proposed cell is reduced during the read operation. The proposed memory cell noise margin is also improved by the dual split power line technique [18]. The 6T and transmission gate based 8T SRAM cells are constructed using Hetero-junction Tunnel Field Effect Transistor (HETT) which dissipates less power compared to that of MOS transistors. HETT based SRAM cells also offer high speed operations [19]. The Schmitt trigger based 8T SRAM proposed is a modified version of conventional 6T SRAM cell. A high threshold voltage (Vth) NMOS transistor is added in the pull-down network of the conventional 6T SRAM cell which gives the structure of the Schmitt trigger based 8T SRAM cell [18]. The presence of high Vth NMOS transistor reduces the leakage power consumption of the proposed SRAM cell [18]. A single ended TG based 8-transistor (8T) SRAM cell has feedback cutting facilities, which reduces the disturbances during the reading condition. Hence the SNM of the circuit is increased. The power and delay performances of the circuit are very good as compared with that of conventional SRAM cells [20]. The 2-read/write 8T dual-port SRAM cell consumes less dynamic power. It has an additional circuit named as world line pulse adjusting circuit which adjusts the pulse width of the word line for both read and writes operations. The bit line discharging power is reduced by shortening the width of the word line during different row access. The 2-read/write 8T dual-port SRAM cell reduces the read power by 7% and write power by 18% [21].

6T CNTFET SRAM Cell [3]

Conventional 8T CNTFET SRAM cell [13]

2 Structure and Operation of Proposed NCNTFET Darlington 8T SRAM Cell

The circuit diagram of the proposed NCNTFET Darlington 8T SRAM cell is shown in Fig. 12. It is a modified structure of the conventional 6T CNTFET SRAM cell. Two NCNTFETs (N5 and N6) are connected in Darlington fashion in the pull-down network of the conventional 6T CNTFET SRAM cell gives the structure of the proposed NCNTFET Darlington 8T SRAM cell. The CNTFETs N1, N2, P1, P2, N5, and N6 form the storage cell of the proposed structure. The CNTFETs N3 and N4 act as access transistors. These access transistors are controlled by the word line. It has storage nodes Q and QB. The bit lines BL and BLB are used as a path for write and read operations. The presence of Darlington NCNTFETs in the pull-down network of the conventional 6T CNTFET SRAM cell improves the power performance of the memory cell during the write, hold, and read conditions. The power consumption of the proposed NCNTFET Darlington 8T SRAM cell is very less as compared with that of conventional 6T and 8T CNTFET SRAM cells.

2.1 Write Operation

For write a bit in the storage cell, the corresponding bit and its complement values are placed on BL and BLB respectively. WL is raised high; the access transistors are enabled. Hence BL value is stored in Q and BLB value stored in QB. Figure 13 illustrates the write operation of ‘1′ in the proposed cell. The conditions for write are BL = 1, BLB = 0, and WL = 1. The WL is raised; this in turn enables the access transistors. Hence the BL and BLB values are transferred to Q and QB respectively. The storage node Q is raised high. Hence N2 is enabled and P2 is disabled. Due to that QB gets discharged to ground potential. Hence P1 is enabled and N1 is disabled. The ‘ON’ condition of P1 connects the storage node Q with supply voltage (VDD). This shows the bit ‘1’ store in Q and bit ‘0’ in QB.

2.2 Read Operation

The structure of the proposed NCNTFET Darlington 8T SRAM cell for the read operation is shown in Fig. 14. Before read operation, the WL has to be kept low for some time, simultaneously the bit lines are pre-charged up to VDD. After pre-charging, the WL is raised high. Hence, the access transistors N3 and N4 are turned ‘ON’. As shown in Fig. 12, during the conditions Q = 1 and QB = 0, N1 is ‘OFF’ and N2, N4, N5 and N6 are in ‘ON’ condition. Hence, the BLB gets a discharging path through all these ‘ON’ transistors. Meanwhile, the BL maintains its potential as that of VDD. The potential difference between the BL and BLB is sensed by the sense amplifier and the resultant stored value is produced at the output of the sense amplifier.

2.3 Hold Operation

The hold mode of the SRAM cell is also called standby mode. During hold operation WL = 0. Hence the access transistors N3 and N4 are switched off. Therefore, neither writing nor reading is possible. The storage nodes hold the bit values stored in the previous clock cycle. In Fig. 15, the hold operation is shown.

3 Results and Power Analysis

A Darlington pair of NCNTFETs are connected in the pull-down network of the conventional 6T SRAM cell gives the structure of proposed NCNTFET Darlington 8T SRAM cell. The Darlington pair is offering high input impedance. The presence of high impedance Darlington pair in series with the pull-down network reduces the leakage current flow through it. Hence the power performance of the proposed NCNTFET Darlington 8T SRAM Cell is improved as compared to that of conventional 6T and 8T SRAM cells. The power comparison of SRAM cells is summarised in Table 2. The hold condition power consumption of conventional 6T and 8T CNTFET SRAM cells are 1.7469 × 10–5 W but it is found to be 2.1366 × 10–10 W for the proposed NCNTFET Darlington 8T SRAM Cell. The hold condition power performance of the proposed NCNTFET Darlington 8T SRAM Cell is nearly 100% improved as Compared to that of Conventional 6T and 8T CNTFET SRAM cells. During the read operation, the power consumption of conventional 6T CNTFET SRAM and 8T CNTFET SRAM cells is 1.7985 × 10–05 W and 1.8279 × 10–5 W respectively. The read power performance of the proposed NCNTFET Darlington 8T SRAM Cell is improved by 87.18% and 88.57% than conventional 6T CNTFET SRAM and 8T CNTFET SRAM cells respectively. Figure 16 shows the power comparison of conventional 6T, 8T, and proposed SRAM cell. The device parameters for nominal values and process assumptions for simulations are listed in Table 1

The nominal values of chiral vectors are m = 19 and n = 0. Rather than choosing the same chiral values for all the CNTFETs, the dual chiral value concept is applied. Dual chiral values can be applied in two ways. Case 1: NCNTFET with m = 19, n = 0 and PCNTFET with m = 16, n = 0 and Case 2: PCNTFET with m = 19, n = 0 and NCNTFET with m = 16, n = 0. The simulation result shows that the power consumption of all the memory cells during dual chiral values is lesser as compared with that of nominal value power consumption [2]. The Table 3 gives the complete power report for single and multiple chiral vectors.

The gate oxide thickness (Hox) of CNTFET is varied by ± 20% from the nominal value (4 nm). The power performance of the SRAM cells is investigated for the variation of gate oxide thickness during the write, hold, and read conditions. It is noted that the power consumption of the memory cell is inversely proportional to gate oxide thickness. Increasing gate oxide thickness increases the threshold voltage of the CNTFET and reduces the charge leakage from the channel to the gate. Hence, the power consumption of conventional 6T, 8T, and proposed Darlington SRAM cell are decreased while increasing the gate oxide thickness. The Power comparisons of various SRAMs under oxide thickness variation are provided in Table 4.

Gate oxide dielectric constant of CNTFET is varied from 3.9 to 55 and the power performances of the SRAM cells are observed. The dielectric constant of SiO2 is 3.9, HfO2 is 16, and TiO2 is 55. The write, hold, and read power consumption of conventional 6T, 8T, and proposed Darlington SRAM cells are calculated for these materials. The gate oxide dielectric constant of CNTFET is directly proportional to the channel current conduction of CNTFET. Hence, increasing dielectric constant increases the power consumption of the memory cell. The Power comparisons of various SRAMs under dielectric constant variation are summarised in Table 5.

Temperature of CNTFET is varied from room temperature (27 °C) to − 20 °C, − 10 °C, 100 °C, and 227 °C. The corresponding power consumption variation of conventional 6T, 8T, and proposed Darlington SRAM cell are noted. Increase in temperature of CNTFET generates thermal charges in the CNTFET channel. Hence, the increase in temperature increases the current conduction of CNTFET. This increases the power consumption of the SRAM cells. The power consumption of SRAM cells is positively proportional to the temperature. The Power comparisons of various SRAMs under temperature variation are tabulated in Table 6.

The power consumption of conventional 6T, 8T, and proposed Darlington SRAM cell are calculated for single and multiple (2, 3, 4, and 5) CNTs during the write, hold and read modes of operations. Increase in number of CNTs increases the amount of current flow in the CNTFET channel. This, in turn increases the power consumption of memory cell. Hence, the power consumption of conventional 6T, 8T, and proposed Darlington SRAM cell is directly proportional to the number of CNTs present in the CNTFET. The Power comparisons of various SRAMs during single and multiple nano tubes are provided in Table 7.

The axial distance between two adjacent CNTs is called the pitch value of CNTFET. The nominal pitch value is found to be 20 nm. Here, the power consumption of CNTFET is calculated for pitch values such as 10 nm, 50 nm, and 90 nm. The power consumption of conventional 6T, 8T, and proposed Darlington SRAM cell are calculated for those corresponding pitch values. Increasing pitch value increases the power consumption of the SRAM cells. The Power comparisons of various SRAMs under pitch value variation are tabulated in Table 8.

The nominal supply voltage for 32 nm technology is 0.9 V. The proposed Darlington SRAM cells have not achieved the required functionality when the supply voltage is less than 0.6 V. Hence the supply voltage is varied from 0.9 to 0.6 V. The power consumption of conventional 6T, 8T, and proposed Darlington SRAM cell are noted for write, hold, and read conditions. From the simulation results, it can be seen that the power consumption of the SRAM cell is directly proportional to the supply voltage. Thus, decreasing the supply voltage decreases the power consumption of SRAM cells. The Power consumption comparisons of various SRAMs under supply voltage variation are provided in Table 9. Figures 17, 18, 19, 20, 21, 22 show the power comparison of 6T, 8T and proposed SRAM cells for the varation of CNTFET parameters

4 Static Noise Margin Analysis

The static noise margin (SNM) is one of the important performance metrics of a memory cell. The stability of a memory cell is measured based on SNM of the cell. Maximum tolerance of SRAM cells against DC noise voltage is defined as the static noise margin of the SRAM cell. For evaluating SNM, the voltage transfer characteristics (VTCs) of memory cell storage nodes Q and QB are noted. A butterfly diagram is drawn from VTCs. SNM of a memory cell is equal to the largest diameter of the square that can be fixed in the butterfly diagram [7]. The proposed NCNTFET Darlington 8T SRAM cell is offering high write SNM than the conventional 6T and 8T CNTFET SRAM cells. The WSNM of conventional 6T and 8T CNTFET SRAM cells is 240 mV. The proposed NCNTFET Darlington 8T SRAM offers 410 mV WSNM. Hence the WSNM of proposed NCNTFET Darlington 8T cell is increased by 70.83% than both conventional 6T and 8T CNTFET SRAM cells. Due to the presence of Darlington pair CNTFETs the hold and read modes noise margins of the proposed cell reduced lesser than conventional 6T and 8T cells. Figure 23 shows the SNM comparison of conventional 6T, 8T, and proposed SRAM cell.

5 Comparison of Various CNTFET SRAM Cells

The simulation results shows that the hold power consumption of proposed 8T cell is 99.99% lower when compared with that of conventional 6T [3], 8T [13], 10T [22] and 10T [23] cells. The read power consumption of proposed 8T cell is 88.38%, 88.57%, 91.96% and 93.29% lower when compared with that of conventional 6T [3], 8T [13], 10T [22] and 10T [23] cells, respectively. The proposed 8T cell also achieves write SNM of 1.7, 1.7, 1.7, and 1.32 times higher compared to 6T [3], 8T [13], 10T [22] and 10T [23] cells, respectively. Figures 24 and 25 shows the power and SNM comparison of various CNTFET SRAM cells, respectively.

6 Conclusion

The effect of CNTFET parameters on drain current and drain to source voltage is observed. The simulation results show that the CNTFET drain current and power consumption are directly proportional to dielectric constant, chiral vectors, temperature, number of CNTs in the CNTFET channel, pitch value, and supply voltage. The CNTFET drain current and power consumption are inversely proportional to gate oxide thickness. The hold condition power performance of the proposed NCNTFET Darlington 8T SRAM Cell is nearly 100% improved as Compared to Conventional 6T and 8T CNTFET SRAM cells. The read power performance of the proposed NCNTFET Darlington 8T SRAM Cell is improved by 87.18% and 88.57% than conventional 6T CNTFET SRAM and 8T CNTFET SRAM cells respectively. The WSNM proposed NCNTFET Darlington 8T cell are increased by 70.83% than both conventional 6T and 8T CNTFET SRAM cells.

References

I.A. Khan, N. Alam, CNTFET based circuit design for improved performance, in Proc.-2019 Int. Conf. Electr. Electron. Comput. Eng. UPCON 2019 (2019), pp. 1–5. https://doi.org/10.1109/UPCON47278.2019.8980053.

S. Lin, Y. Bin Kim, F. Lombardi, Design of a CNTFET-based SRAM cell by dual-chirality selection. IEEE Trans. Nanotechnol. 9(1), 30–37 (2010). https://doi.org/10.1109/TNANO.2009.2025128

M. Elangovan, K. Gunavathi, Stability analysis of 6T CNTFET SRAM cell for single and multiple CNTs (2019). https://doi.org/10.1109/ICDCSyst.2018.8605154.

A. Karimi, A. Rezai, Improved device performance in CNTFET using genetic algorithm. ECS J. Solid State Sci. Technol. 6(1), M9–M12 (2017). https://doi.org/10.1149/2.0101701jss

K.R. Agrawal, R. Sonkusare, PVT variations of a behaviorally modeled single walled carbon nanotube field-effect transistor (SW-CNTFET), in 2015 Int. Conf. Nascent Technol. Eng. Field, ICNTE 2015—Proc., (2015), https://doi.org/10.1109/ICNTE.2015.7029940.

G. Cho, Y. Bin Kim, F. Lombardi, Assessment of CNTFET Based circuit performance and robustness to PVT variations, in Midwest Symp. Circuits Syst. (2009), pp. 1106–1109. https://doi.org/10.1109/MWSCAS.2009.5235961.

M. Nizamuddin, H. Shakir, P. Gupta, Design of ambipolar CNTFET based universal logic gates, in 2019 Int. Conf. Power Electron. Control Autom. ICPECA 2019—Proc., vol. 2019-November (2019), p. 7–11. https://doi.org/10.1109/ICPECA47973.2019.8975388.

S.K. Sinha, S. Chaudhury, Impact of temperature variation on CNTFET device characteristics, in CARE 2013—2013 IEEE Int. Conf. Control. Autom. Robot. Embed. Syst. Proc. (2013).https://doi.org/10.1109/CARE.2013.6733774

C. Venkataiah, Investigating the effect of chirality, oxide thickness, temperature and channel length variation on a threshold voltage of MOSFET, GNRFET, and CNTFET. J. Mech. Contin. Math. Sci. 1(3), 232–244 (2019). https://doi.org/10.26782/jmcms.spl.3/2019.09.00018

M. Elangovan, K. Gunavathi, High stable and low power 10T CNTFET SRAM cell. J. Circuits Syst. Comput. (2019). https://doi.org/10.1142/S0218126620501583

M.S. Benbouza, D. Hocine, Y. Zid, A. Benbouza, New nanotechnology structures CNTFET GaAs, in 8th Int. Conf. Renew. Energy Res. Appl. ICRERA 2019 (2019), pp. 799–803. https://doi.org/10.1109/ICRERA47325.2019.8997103

E. Abiri, A. Darabi, Design of low power and high read stability 8T-SRAM memory based on the modified Gate Diffusion Input (m-GDI) in 32 nm CNTFET technology. Microelectron. J. 46(12), 1351–1363 (2015). https://doi.org/10.1016/j.mejo.2015.09.016

M. Elangovan, K. Gunavathi, High stable and low power 8T CNTFET SRAM cell. J. Circuits Syst. Comput. (2020). https://doi.org/10.1142/S0218126620500802

M. Bansal, A. Kumar, P. Singh, and R.K. Nagaria, A novel 10T SRAM cell for low power applications, in 2018 5th IEEE Uttar Pradesh Sect. Int. Conf. Electr. Electron. Comput. Eng. UPCON 2018 (2018), pp. 1–4. https://doi.org/10.1109/UPCON.2018.8596829.

A. Feki et al., Sub-threshold 10T SRAM bit cell with read/write XY selection. Solid. State. Electron. 106, 1–11 (2015). https://doi.org/10.1016/j.sse.2014.11.018

F. Zhou, X. Hu, and G. Wang, A 32-Kb high-speed 8T SRAM with fine grained bitline stacking for leakage reduction in 7nm technology, in China Semicond. Technol. Int. Conf. 2019, CSTIC 2019 (2019), pp. 1–3. https://doi.org/10.1109/CSTIC.2019.8755790.

M. Uddin Mohammed, N.M. Hossain, and M.H. Chowdhury, A disturb free read port 8T SRAM bitcell circuit design with virtual ground scheme, in Midwest Symp. Circuits Syst., vol. 2018-August (2019), pp. 412–415. https://doi.org/10.1109/MWSCAS.2018.8624107.

L. Lu, T. Yoo, L. Van Loi, and T.T.H. Kim, An ultra-low power 8T SRAM with vertical read word line and data aware write assist, in 2018 IEEE Asian Solid-State Circuits Conf. A-SSCC 2018—Proc., vol. 6(8166) (2018), pp. 143–144. https://doi.org/10.1109/ASSCC.2018.8579292.

B.V.V. Satyanarayana, M. Durga Prakash, Design and performance analysis of transmission gate based 8T SRAM cell using heterojunction tunnel transistors (HETTs), in 2018 Int. Conf. Recent Innov. Electr. Electron. Commun. Eng. ICRIEECE 2018 (2018), pp. 1372–1376. https://doi.org/10.1109/ICRIEECE44171.2018.9009117.

D. Tripathy, T. Manasneha, V. Das, A single ended TG based 8T SRAM cell with increased data stability and less delay, in RTEICT 2017—2nd IEEE Int. Conf. Recent Trends Electron. Inf. Commun. Technol. Proc., vol. 2018-January (2017), pp. 1282–1285. https://doi.org/10.1109/RTEICT.2017.8256805.

R. Rnr et al., $’\QDPLF 3RZHU 5HGXFWLRQ LQ 6 \ QFKURQRXV 5 : 7LPLQJ ZLWK 6DPH ’ LIIHUHQW 5RZ $ FFHVV 0RGH 4(2045), 13–16 (2017)

S. Gupta et al., Low-power near-threshold 10T SRAM bit cells with enhanced data-independent read port leakage for array augmentation in 32-nm CMOS. IEEE Trans Circuits Syst I Regular Papers 66(3), 978–988 (2019)

P. Sanvale, N. Gupta, V. Neema, A. Prasad, An improved read-assist energy efficient single ended P-P-N based 10T SRAM cell for wireless sensor network. Microelectron. J. 92, 104611 (2019). https://doi.org/10.1016/j.mejo.2019.104611

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Elangovan, M., Karthickeyan, D., Arul Kumar, M. et al. Darlington Based 8T CNTFET SRAM Cells with Low Power and Enhanced Write Stability. Trans. Electr. Electron. Mater. 23, 122–135 (2022). https://doi.org/10.1007/s42341-021-00329-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-021-00329-w