Abstract

We present new results on the development of larger arrays (presently 72 channels, goal of multiple units of 160 channels) of superconducting LC filters. The a-Si:H based resonators show a quality factor above 10.000. The latest design utilizes oppositely wound planar coil pairs which enable close packing with low magnetic cross talk. We present results on the obtained center frequency distribution within the range of 1 to 3 MHz.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

One of the options for multiplexed read out of arrays of superconducting Transition Edge Sensors (TES) is Frequency Division Multiplexing (FDM). An essential component of such a circuit is an array of narrow band superconducting resonators, each consisting of an inductor and two capacitors. SRON is developing FDM for the SAFARI instrument on board of the Japanese space mission SPICA [1]. SAFARI is an infra-red imaging Fourier Transform Spectrometer with very sensitive TES detector arrays. Multiplexed read-out is essential to cope with the limited available cooling power at the temperature stages near the detector operating temperature of 100 mK. The present baseline design of the SAFARI detector system is described in Ref. [2]. Initial experiments with 18-channel LC filters in an FDM configuration were presented last year [3], together with more details on specifications, design and fabrication of the LC filter arrays [4]. In these publications we showed the feasibility of using LC filters with Nb/a-Si:H/Nb based capacitors with quality factor Q>10.000 in an FDM system. In the present publication we focus more on the scalability of this process for larger detector arrays, addressing issues on fabrication yield, cross-talk and accuracy of center frequency of the filters. For this study we designed 72-channel filter chips (and 72 pixel detector chips and interconnecting structures to the SQUID amplifiers) as an intermediate step towards the SAFARI baseline design of multiple units with 160 frequency channels in the range 1–3 MHz.

2 Design and Fabrication

The fabrication process of the LC filter chips was essentially not changed since the previous publication, except for some minor improvements in deposition and etching procedures. The superconducting capacitor electrodes and all wiring layers still consist of sputter deposited Nb with Ta protection. The capacitor dielectric layer is made from PECVD amorphous silicon (a-Si:H), and insulating layers in the planar coils and low inductance strip line wiring are sputtered SiO2. Patterning is done with positive photoresist and reactive ion etching.

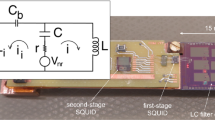

The main changes are visible in the design of the inductors on the chips. The inductors are still planar spiral structures, but instead of a single spiral, a coil now consists of a set of 2 spirals, wound in opposite direction. This design enables the coils to be placed much closer together with similar mutual induction. The first neighbor is really directly adjacent with essentially zero mutual inductance (except for very small asymmetry effects). The design is backed by inductance calculations using FastHenry[5] modeling software. For a 10−3 level of mutual inductance, the “gradiometric-like” sets of inductors (2 to 5 μH with 4 μm line pitch) can be placed at a pitch of about 2 mm. A picture of a finished unit cell of the array is presented in Fig. 1. A magnified view of the inductors is visible in Fig. 2.

(Color online) Unit cell of a set of 2 LC resonators with oppositely wound coil pairs. Large grey rectangles are capacitor surfaces (1 mm wide) Connection lines to the detector are on the left, wire bonding pads to the SQUID amplifier to the right. AC-bias coupling capacitors are placed next to pads labeled “M”

The complete assembly of a 72-channel FDM detector system is shown in Fig. 3. It consists of a 8×8 pixel bolometer array [6], the LC filter chip, an equalized-induction summing chip and a SQUID amplifier, all integrated in a light tight housing.

3 Results and Discussion

3.1 Fabrication Yield

The first step of characterization is measurement of the resistance at room temperature of each component and strip line connection segment. This provides a first estimate of the fabrication yield. With the first 4 wafers, each containing five different 72-ch chips, three 18-ch chips and one 8-ch test chip, there seems to be an issue with more spurious particles in the a-Si layer than normal, decreasing the yield of leak-free capacitors and occasionally damaging a coil or strip line. The total circuit yield per wafer varied between 80% and 85%. Since earlier wafers with an old design showed room temperature capacitor yield above 98%, we believe that following better machine operating procedures and optimization of a-Si deposition parameters, this yield will approach the 98%, which is the goal for the SAFARI project.

Other factors than described above affect the final yield. Especially the small AC-bias coupling capacitors are sensitive for ESD induced failure, occurring during wire bonding and connection of electronics. One failure affects a broad frequency range [7], whereas other failures mostly result in only one dead pixel. Shorts in coils are electrically and optically not easy to detect, but result in a shifted center frequency. This can lead to smaller available loop gain in the baseband feedback system, such that these channels must be excluded from the operation set (= dead pixel).

3.2 Quality Factor Q

The quality factor Q of a resonance circuit is defined as Q=f/Δf with f the resonance frequency and Δf the 3 dB bandwidth. Q is also related to the effective series resistance R esr in the circuit by Q=2πf⋅L/R esr. R esr in a superconducting circuit is dominated by loss in the capacitor dielectric. The specification for Q originates from demands on voltage biasing the detector, R esr should be smaller than about R TES/3 with R TES the setpoint resistance. Concluding, Q>6πf⋅L/R TES. L and R TES should be chosen to fulfil the electrothermal stability requirements of the detector [8]. A graph of measured quality factor in the series resonance setup (the regular FDM operation mode) at 58 mK is presented in Fig. 4. Several of the low-Q resonances are expected since these are connected to fixed resistors. The group with Q factors between 2000 and 8000 are probably due to TES detectors that did not reach the superconducting state completely (this bolometer array showed severely reduced T c by a novel design with extra Cu islands). The group with Q above 8000 shows the intrinsic quality factor of the LC resonators. The trend with higher Q factors at higher frequency can be explained by an un-intentional circuit independent series resistance of 2.5 mΩ, probably originating somewhere in the coils (contacts, step crossings, or quality of the Nb layer).

(Color online) Deviation from corrected design frequency value (red diamonds, left scale) and Q factor (blue squares, right scale) for the 54 detected resonances at 58 mK in the assembly of Fig. 3. Dashed line is SAFARI requirement for Q (R esr<5.3 mΩ, L=2 μH)

More chips were characterized by creating a set of parallel LC resonators, connected in series with each other (by Al wire bonding) and measuring directly the response with a network analyzer. Highest Q values measured at 4.2 K in this way are typically 4000, since normal conducting Al wire bonds limit R esr. The Q is however large enough to address frequency accuracy. At temperatures between 100 and 300 mK in a dilution fridge, we measure values consistent with the series resonance measurement of Fig. 4. Highest Q values observed in this way were around 20.000.

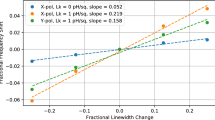

3.3 Center Frequency Accuracy

As baseline frequency spacing a value of 12.5 kHz has been chosen (160 channels between 1 and 3 MHz). For reasons of cross talk and the maximum usable loop gain in the baseband feedback system [7] the required accuracy of this spacing is about 10% of this value. In Fig. 4 the deviations from nominal frequency (corrected in first order for mean dielectric thickness deviation) have been plotted. The 1-σ deviation is about 8 kHz for this setup. The deviations are due to uncorrected variation in induction and capacitance. Sources of induction variations are wire bonds, detector pixel wiring geometry, effects of capacitor area on the self-inductions, and also defects in coils play a role. Some induction effects should later be reduced further by careful design. The long-range dielectric thickness variation on the chip has a significant effect on the spread. In Fig. 4 this effect looks like a spread in frequency deviations because the resonance frequencies are very irregularly distributed across the chip (to be re-considered). It should be possible to compensate in first order for this effect in future designs. What will remain are statistical capacity variations, mainly due to intermediate-range (μm to mm) variations in dielectric thickness and/or relative static permittivity. It will be very difficult to measure these small variations with techniques other than capacitor fabrication. On 14×20 mm2 test chips with parallel resonators without inductance variations we have measured a 1-σ frequency spread of 2 kHz (=0.1%). In order to reach the final specification we believe that we will have to use a method of capacitor trimming after characterization of the initial resonance positions.

References

B. Swinyard et al., The space infrared telescope for cosmology and astrophysics: SPICA; a joint mission between JAXA and ESA. Exp. Astron. 23, 193–219 (2009)

B.D. Jackson et al., The SPICA-SAFARI detector system: TES detector arrays with frequency division multiplexed SQUID readout, IEEE Trans. THz Sci. Technol. (2011). T-TST-SPI-10-2011-00003 (accepted)

R.H. den Hartog et al., IEEE Trans. Appl. Supercond. 21(3), 289–293 (2011)

M.P. Bruijn et al., IEEE Trans. Appl. Supercond. 21(3), 294–297 (2011)

FastHenry 3.0: www.fastfieldsolvers.com (2011)

P. Khosropanah et al., Low noise TES approaching SAFARI instrument requirements. J. Low Temp. Phys. (this volume)

R.H. den Hartog et al., Frequency division multiplexed readout of TES detectors with baseband feedback. J. Low Temp. Phys. (this volume)

K. Irwin, G. Hilton, Transition-edge sensors, in Cryogenic Particle Detection, ed. by C. Enss. Topics in Appl. Phys., vol. 99 (Springer, Berlin, 2005), pp. 63–149

Acknowledgements

The authors thank Dr. J.K. Rath (Nanophotonics Physics of Devices, Utrecht University) for deposition of a-Si:H layers, A.J. van der Linden for fabrication assistance, and M. Schoemans and M.A. Lindeman for measurement assistance. This work was financially supported by the Netherlands organization for Scientific Research (NWO).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bruijn, M.P., Gottardi, L., den Hartog, R.H. et al. High-Q LC Filters for FDM Read out of Cryogenic Sensor Arrays. J Low Temp Phys 167, 695–700 (2012). https://doi.org/10.1007/s10909-011-0422-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10909-011-0422-5