Abstract

Superconducting resonators are now found in a broad range of applications that require high-fidelity measurement of low-energy signals. A common feature across almost all of these applications is the need for an increased number of resonators to further improve sensitivity, combined with the desire to limit cryogenic readout channels and complexity. One of the major limitations of current resonator arrays is the observed scatter in the resonator frequencies when compared to the initial design. Here we present recent progress toward identifying one of the dominant underlying causes of resonator scatter - inductor line width fluctuation. We designed and fabricated an array of lumped-element resonators in which the inductor line width changes from 1.8 \(\upmu {\hbox {m}}\) to \(2.2 \,\upmu {\hbox {m}}\) in steps of 0.1 \(\upmu {\hbox {m}}\). The inductor is defined using electron-beam lithography to probe and quantify the systematic variation of resonance frequencies. Paired with two different capacitor geometries the resonators showed a linear frequency spacing of \(\approx {20}\, \hbox {MHz}\) and 30 MHz, respectively, or \({1.48}\, {\%}\) and \({1.96}\,\%\) in fractional frequency shift (\(\varDelta f/f_{o}\)). This linear relationship matches our theoretical prediction. Our result demonstrates significant improvement in resonator array frequency scatter is readily achievable if inductor line width variation is sufficiently controlled.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Superconducting microwave resonators have been widely used for high sensitivity detection of excitations such as charge [1,2,3] and photons [4, 5] due to their simple fabrication process and frequency domain multiplexing capability. Among the various types of superconducting resonator-based detectors, Microwave Kinetic Inductance Detectors (MKIDs) [6, 7] have found broad application [8,9,10,11,12,13]. Over the past decade, arrays of MKIDs have evolved to thousands [14, 15] of detectors per wafer with improved noise equivalent power (NEP). However, scatter in resonator frequency placement, where the fabricated resonance frequencies are shifted from their designed values, has become a limiting issue for large array performance. Various parameters could contribute to this fluctuation such as nonuniformity in the critical temperature (\(T_c\)) and film thickness, nonuniformity in lithographic processing, and nonuniform etch profiles across the wafer.

One solution for mitigating frequency fluctuations is capacitor trimming [16], a method that improves the MKID frequency distribution at the cost of introducing additional fabrication steps. Another approach is to improve MKID materials and fabrication processes to improve resonator frequency placement, though this approach requires detailed studies to understand the fundamental parameters that result in scatter of the resonator frequency. This paper is an initial investigation along this direction, and studies how variations in resonator geometry arising from fabrication processes contribute to frequency scatter. Our work is motivated in part by results from previously fabricated MKIDs where we observed significant line width variation - up to 2 \(\upmu {\hbox {m}}\) for a 4 \(\upmu {\hbox {m}}\) wide feature - across a 6 inch wafer. Bearing in mind that the inductance of a microstrip inductor strongly depends on its line width, this variation will significantly change the inductance of our lumped element inductor and may well explain the resonant frequency shift of the resonators. To investigate the impact of the line width variation on resonator frequency placement we carried out a study using electron beam (e-beam) lithography to fabricate resonators with line widths varying in steps of 100 nm, and evaluated their resonance frequency placement as a function of their line widths.

2 Modeling the Microstrip Inductance

To develop some intuition about the relationship between line width and resonator frequency we look at S-shaped inductors fabricated on PCBs where the inductance per unit length and thickness is defined:

with w the width of the S-shaped strip and \(\beta\) and \(\alpha\) are determined by fitting to multiple resonators [17]. The inductance change, \(\varDelta L_{m}\), due to small line width change, \(\varDelta w\), can be approximated by Taylor expansion around w:

Similarly the kinetic inductance change, \(\varDelta L_{K}\), due to line width variation, \(\varDelta w\), is

where we have used the kinetic inductance equation from reference [18]: \(L_{k}(T)=\mu _{o}\lambda ^{2}(T)\left( \frac{l}{wd}\right)\). l, w and d are the length, width and thickness of the superconducting strip. \(\lambda (T)\) is the Ginzburg–Landau (GL) magnetic penetration depth at temperature T and \(\mu _{o}\) is the permeability constant.

The corresponding shift in resonator frequency \(\varDelta f_{o}\) is then

and the fractional frequency shift is given by

We also simulate the response of our lumped element resonators using Sonnet while varying the inductor width from 1.5 \(\upmu {\hbox {m}}\) to 2.5 \(\upmu {\hbox {m}}\) in steps of 0.25 \(\upmu {\hbox {m}}\). Figure 1 shows the result of our simulations for each of our two circuit capacitor designs (see Sect. 3).

Simulated fractional resonant frequency shift, \(\varDelta f_{o}/f_{o}\), versus fractional line width variation, \(\varDelta w/w\), for ‘X-pol’ and ‘Y-pol’ resonators as defined in Fig. 2. Inductor line widths were varied from 1.5 \(\upmu {\hbox {m}}\) to 2.5 \(\upmu {\hbox {m}}\) in steps of 0.25 \(\upmu {\hbox {m}}\). \(L_{K}\) is the kinetic inductance of the superconducting thin film in the simulation

3 Test Resonator Design

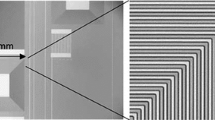

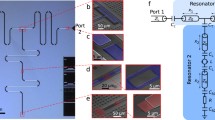

To empirically study the impact of resonator geometry on frequency placement we designed a test device comprised of five nearly identical lumped element resonators with varying inductor line width. In our design (see Figure 2) we have five pixels with each pixel having a ‘X-pol’ resonator and a ‘Y-pol’ resonator. All of the ‘X-pol’ (‘Y-pol’) resonators have the same circuit capacitor design \(C_x\) (\(C_y\)), and the inductor line width for both resonators is varied from 1.8 \(\upmu {\hbox {m}}\) to 2.2 \(\upmu {\hbox {m}}\) in steps of 0.1 \(\upmu {\hbox {m}}\) across the five pixels. With this configuration we expect two groups of resonances corresponding to the two circuit capacitor designs \(C_{x}\) and \(C_{y}\). Within each group we expect five linearly distributed resonances corresponding to the five inductors with different line width.

Images of the test chip and components. (a) Image of chip A which has five pixels and each pixel has two resonators named ‘X-pol’ and ‘Y-pol’ because of the orthogonal direction of the two inductors. (b) Zoom-in of the S-shaped inductors. (c) Zoom-in of one of the pixels. Left interdigital capacitor \(C_{x}\) is connected to the horizontal (X) S-shaped inductor and the right interdigital capacitor \(C_{y}\) is connected to the vertical (Y) S-shaped inductor. (d) Zoom in of a interdigital capacitor \(C_{y}\)

4 Fabrication

The e-beam devices presented here were fabricated on a single silicon wafer, which minimizes the impact from comparing materials from different depositions. To achieve the required 100 nm line width resolution, the resonators were patterned using e-beam lithography with a resolution of 10 nm.

The fabrication process begins with vacuum baking the bare wafer at \({120}^\circ \,{\hbox {C}}\) for six minutes to remove moisture. E-beam resist (PMMA 950 A4) is spun on the wafer at a speed of 4000 rpm for 40 seconds and then baked at \({180}^\circ \,{\hbox {C}}\) for 4 minutes afterward. The resonators are patterned in a single lithography layer. The inductor, capacitor, and connection lines were written with a dose of 720 \({\upmu \,{\hbox {C}}/{\hbox {cm}}^{2}}\), while the feed-through lines as well as the contact pads were written with a dose of 800 \({\upmu \,{\hbox {C}}/{\hbox {cm}}^{2}}\); proximity effect correction effectively lowers the dose for large structures, and the dose was increased purposely to compensate for it. After the pattern is written the wafer was developed with MIBK and IPA with a ratio of 1:3 for 40 seconds and rinsed in IPA for 10 seconds. Following development a 20 second oxygen descum process was used to remove leftover e-beam resist. A 30 nm thick Al film is then deposited at rate of 0.17 nm/second via DC magnetron sputtering with 3 mTorr Ar gas processs pressure and deposition system base pressure of \(1.7\times 10^{-8}\) mbar. The applied cathode voltage is 300 volts. The final processing step is an overnight soak in acetone for lift-off.

The two chips we chose to test were near the center of the wafer to minimize film thickness nonuniformity between the two chips. During fabrication, one of the capacitors on one of our devices (chip B) had a liftoff issue and was discarded from our measurements; this only impacted a single resonator.

5 Test Results

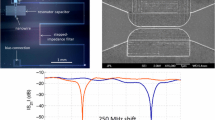

(a) Comparison of resonance frequencies from two chips with same resonator design. The blue trace is for chip A and the orange trace is for chip B. The inset is zoomed in to the two resonances from chips A and B around 1.3917 GHz; an offset of 15 kHz is observed. (b) Resonance frequency scatter for resonators patterned using e-beam lithography and lift-off and resonators patterned using optical lithography and wet etching. Significantly lower frequency scatter was observed in the resonator chips fabricated using e-beam lithography and liftoff

We tested two chips (chip A and chip B) in a dilution refrigerator with base temperature of 10 mK. The input lines have \(\approx\) 70 dB attenuation and the output signal was amplified with a HEMT amplifier with gain of around 40 dB. Superconducting coaxial cables were used between the output of the sample box and the HEMT amplifier to minimize signal loss. The resonances were scanned with a standard \(S_{21}\) measurement using a VNA.

Figure 3(a) shows the measured resonances for both chip A and B. The trace for chip A shows ten resonances with the lower (higher) frequency resonances corresponding to resonators with ‘Y-pol’ (‘X-pol’) capacitor design. Within each group, the resonances differ due to the varying inductor line width. In Fig. 4, we plot the measured fractional frequency shift, \(\varDelta f_{o}/f_{o}\), versus the change in inductor line width, \(\varDelta w\). Our data exhibited a clear linear relationship as predicted by Eq. (8), with a slope that is consistent with predictions from our simulations.

We estimate the frequency scatter from our e-beam+Liftoff process by comparing the frequencies for identically designed resonators and found the largest scatter was \(\sim\) 1 MHz. This is consistent with the 10 nm e-beam resolution and our measured dependence of the inductance on line width. To give a sense of improvement in resonator frequency scatter with better inductor line width control, we compare our result with a similar measurement of frequency scatter for two other sets of resonators patterned with direct write optical lithography and wet etching. The lithography process uses SPR955 photoresist spin coated at 3000 rpm for 45 seconds and baked at \({90}^\circ \,{\hbox {C}}\) for 2 minutes. The wafer was patterned with a 405 nm laser with dose of 140 \({{\hbox {mJ}}/{\hbox {cm}}^{2}}\) followed by a post bake at \({110}^\circ \,{\hbox {C}}\) for 90 seconds. After exposure the wafer was developed with CD26 developer for 1 minute followed by a DI water rinse. The developed wafer was etched with Al etchant for 90 seconds followed by a DI water rinse. We expect a larger inductor line width variation from these resonators and as shown in figure 3(b) a much larger frequency scatter (\(\approx\) 30 MHz) is observed from these two sets of chips, which further validates our conclusion about the influence of inductor line width variation on resonator frequency scatter.

6 Conclusion

We have demonstrated the impact of S-shaped inductor line width variation on the frequency scatter of lumped element resonators. Our results are in good agreement with our simulations and show that control of resonator geometry can be a significant contributor to frequency scatter in large arrays of MKIDs.

Data availability

Data used in this work is available on reasonable request.

References

R.J. Schoelkopf, P. Wahlgren, A.A. Kozhevnikov, P. Delsing, D.E. Prober, The radio-frequency single-electron transistor (rf-set): A fast and ultrasensitive electrometer. Science 280(5367), 1238–1242 (1998)

B.L. Brock, Juliang Li, S. Kanhirathingal, B. Thyagarajan, M.P. Blencowe, and A.J. Rimberg. Fast and ultrasensitive electrometer operating at the single-photon level. Phys. Rev. Applied, 16:L051004, (Nov 2021)

L. Tosi, D. Vion, H. le Sueur, Design of a cooper-pair box electrometer for application to solid-state and astroparticle physics. Phys. Rev. Applied 11, 054072 (2019)

M.D. Shaw, J. Bueno, P. Day, C.M. Bradford, P.M. Echternach, Quantum capacitance detector: A pair-breaking radiation detector based on the single cooper-pair box. Phys. Rev. B 79, 144511 (2009)

P. M. Echternach, B. J. Pepper, T. Reck, and C. M. Bradford. Single photon detection of 1.5 thz radiation with the quantum capacitance detector. Nature Astronomy, 2(1):90–97, Jan 2018

Peter K. Day, Henry G. LeDuc, Benjamin A. Mazin, Anastasios Vayonakis, and Jonas Zmuidzinas. A broadband superconducting detector suitable for use in large arrays. Nature, 425:817 EP –, (Oct 2003)

S. Doyle, P. Mauskopf, J. Naylon, A. Porch, C. Duncombe, Lumped element kinetic inductance detectors. Journal of Low Temperature Physics 151(1), 530–536 (2008)

J. Baselmans, S.J.C. Yates, R. Barends, Y.J.Y. Lankwarden, J.R. Gao, H. Hoevers, T.M. Klapwijk, Noise and sensitivity of aluminum kinetic inductance detectors for sub-mm astronomy. Journal of Low Temperature Physics 151(1), 524–529 (2008)

J. Hubmayr et al., Photon-noise limited sensitivity in titanium nitride kinetic inductance detectors. Applied Physics Letters 106(7), 073505 (2015)

Benjamin A. Mazin, Bruce Bumble, Seth R. Meeker, Kieran O’Brien, Sean McHugh, Eric Langman, A superconducting focal plane array for ultraviolet, optical, and near-infrared astrophysics. Opt. Express 20(2), 1503–1511 (2012)

D.C. Moore, S.R. Golwala, B. Bumble, B. Cornell, P.K. Day, H.G. LeDuc, J. Zmuidzinas, Position and energy-resolved particle detection using phonon-mediated microwave kinetic inductance detectors. Applied Physics Letters 100(23), 232601 (2012)

Sam Rowe et al., A passive terahertz video camera based on lumped element kinetic inductance detectors. Review of Scientific Instruments 87(3), 033105 (2016)

W. Guo, X. Liu, Y. Wang, Q. Wei, L.F. Wei, J. Hubmayr, J. Fowler, J. Ullom, L. Vale, M.R. Vissers, J. Gao, Counting near infrared photons with microwave kinetic inductance detectors. Applied Physics Letters 110(21), 212601 (2017)

J.C. van Eyken, M.J. Strader, A.B. Walter, S.R. Meeker, P. Szypryt, C. Stoughton, K. O’Brien, D. Marsden, N.K. Rice, Y. Lin, B.A. Mazin, THE ARCONS PIPELINE: DATA REDUCTION FOR MKID ARRAYS. The Astrophysical Journal Supplement Series 219(1), 14 (2015)

S. Shu, M. Calvo, S. Leclercq, J. Goupy, A. Monfardini, E.F.C. Driessen, Prototype high angular resolution lekids for nika2. Journal of Low Temperature Physics 193(3), 141–148 (2018)

X. Liu, W. Guo, Y. Wang, M. Dai, L.F. Wei, B. Dober, C.M. McKenney, G.C. Hilton, J. Hubmayr, J.E. Austermann, J.N. Ullom, J. Gao, M.R. Vissers, Superconducting micro-resonator arrays with ideal frequency spacing. Applied Physics Letters 111(25), 252601 (2017)

Goran Stojanovic, Mirjana Damjanovic, Compact form of expressions for inductance calculation of meander inductors. Serbian Journal of Electrical Engineering 1, 01 (2004)

Anthony J Annunziata, Daniel F Santavicca, Luigi Frunzio, Gianluigi Catelani, Michael J Rooks, Aviad Frydman, and Daniel E Prober. Tunable superconducting nanoinductors. Nanotechnology, 21(44):445202, (oct 2010)

Acknowledgements

Work at Argonne, including use of the Center for Nanoscale Materials, an Office of Science user facility, was supported by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences and Office of High Energy Physics, under Contract No. DE-AC02-06CH11357. Zhaodi Pan is supported by ANL under award LDRD-2021-0186

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Li, J., Barry, P.S., Pan, Z. et al. Reducing Frequency Scatter in Large Arrays of Superconducting Resonators with Inductor Line Width Control. J Low Temp Phys 209, 1196–1203 (2022). https://doi.org/10.1007/s10909-022-02893-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10909-022-02893-8