Abstract

Ferroelectric Bi2VO5.5 thin films were fabricated on p-type (100) Si substrates by sol–gel method and then annealed at different temperatures. The microstructures and surface morphologies of the Bi2VO5.5 thin films were examined by X-ray diffraction and atomic force microscope, respectively. The results indicate that the Bi2VO5.5 thin films show high c-axis preferred orientation and are compatible well with p-type Si substrates. The capacitance–voltage characteristics of Pt/Bi2VO5.5/Si capacitors measured at 1 MHz shows a clockwise hysteresis loop. The memory window of the hysteresis loop is 0.42 V with the gate voltage from −4 to 4 V. It is found that the memory window may be determined by the competition between ferroelectric polarization and charge injection.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

1 Introduction

Recently, ferroelectric thin films have attracted more and more interests due to their applications for ferroelectric random access memory (FeRAM) [1], which has been developed as an ultimate memory with both nonvolatility and high-speed of read/write operation cycle [2]. Among these various types of FeRAM, ferroelectric field effect transistor, wherein ferroelectric thin film as the substitute of gate oxide, has the advantage of small cell size, simple process and low power consumption, compared with other field effect transistors (FET). In the past, the ferroelectric materials such as SrBi2Ta2O9 [3], Pb(Zr,Ti)O3 [4], BiFeO3 [5] and (Bi, La)Ti3O12 [6], have been studied. Compared with other materials, the materials with bismuth layer structures have better fatigue properties, which have drawn more attentions of the researchers.

Bismuth vanadate (Bi2VO5.5, BVO) is one of the most promising ferroelectric materials with single bismuth layer structure, particularly for its application to FET-type FeRAM configured [2]. Over the last few years, the BVO thin films have been fabricated by different methods including MOCVD, chemical solution decomposition [2, 7] and pulsed laser deposition [8, 9]. Among these methods, sol–gel has been extensively employed to fabricate ferroelectric oxide thin films because of its simplicity, low cost and easy compositional and structural control of the films [4, 7].

In this paper, we studied the fabrication of ferroelectric Bi2VO5.5 thin films on p-type silicon (100) by sol–gel method; both structural and electrical properties of the films with different annealing temperatures have been investigated; the effects of different annealing temperatures on the structural and electrical properties of the BVO thin films have been demonstrated.

2 Experimental

The BVO thin films were prepared by sol–gel method using bismuth nitrate [Bi(NO3)2] and ammonium metavanadate [NH4VO3] as raw materials. Ammonium metavanadate was initially dissolved in a mixture of acetic acid and ethylene glycol with stirring. Then acetyl acetone was added into the prepared solution to increase its stability. Finally bismuth nitrate was added into the solution. The resultant solution was stirred for 0.5 h to form the BVO precursor. Before spin-coating, the p-type Si(100) substrates were preheated in air at 200 °C for 3 min. Each individual layer, spinning coated at 3,000 rpm for 20 s, was baked at 350 °C for 3 min to remove solvents and residual organics. Totally 8 layers were deposited on the Si substrate. Then the samples were annealed using a rapid thermal process furnace at 550, 600, 650 and 700 °C, respectively. All the processing was performed in the air.

X-ray diffraction (XRD, Rigaku D/max-2200) with CuKα was used for phase analysis of the films. The surface microstructure of the films was examined using contract mode atomic force micrograph (AFM, Dimension 3100). The cross sectional scanning electron micrograph (SEM, JSM-5610) was utilized to confirm the thickness of 400 nm for the film. Top Pt electrodes with a diameter of 300 μm were deposited on the surface of the films through the mask. The capacitance–voltage (C–V) characteristic measurement was carried out at 1 MHz using Alpha-A High Performance Frequency Analyzer.

3 Results and discussion

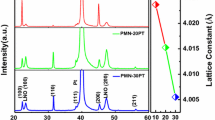

Figure 1 shows the typical X-ray diffraction (XRD) patterns of the BVO thin films deposited on p-type Si annealed at 550–700 °C. As is shown, the diffraction peaks of the films above 600 °C reveal strong BVO (00l) reflections, which indicate the high c-axis-preferred orientation [10] of the BVO films. With the increase of the annealing temperature, the peaks become much stronger and sharper due to further enhancement in crystallization. Typically, the calculated widths at half maximum of (002) are 0.55°, 0.2° and 0.1° for the annealing temperatures at 600, 650 and 700 °C, respectively. The XRD patterns of the BVO films fabricated on Si substrates suggest that higher annealing temperature leads to stronger c-axis-preferred orientation of the films.

Microstructure and surface morphology of the BVO thin films annealed at different temperatures were characterized by AFM. Figure 2a–c show the three dimensional and surface micrographs of the BVO thin films annealed at 600, 650 and 700 °C, respectively. From the pictures, homogeneous distribution of grains in the BVO thin films was observed. The films have relatively smooth surfaces without cracking, which indicates good microstructure qualities of the BVO thin films deposited on the Si substrates. From the two dimensional micrographs of the BVO thin films in Fig. 2, it is obvious that the grain size increases from 250 nm to 650 nm with the annealing temperature increasing from 600 to 700 °C. The root-mean-square (RMS) value of the surface roughness increases with the annealing temperature increasing. The values of RMS increase from 5.085 to 11.048 nm with the annealing temperature increase from 600 to 700 °C. The results demonstrate that the grain size and the value of RMS are dependent on the annealing temperature of the thin film.

The C–V properties of the Pt/BVO/Si structures are shown in Fig. 3. It can be found that the C–V curves show clockwise hysteresis loops for the −4 to 4 V sweep voltage, i.e., the memory window of the metal/ferroelectric/semiconductor (MFS) structure. These hysteresis loops are induced by the process of the switched ferroelectric polarization. It is also obvious that the C–V curves show different shapes with the various annealing temperatures. In order to compare with other annealing temperatures, we define here the memory window as the width of the hysteresis loops at half of its normalized capacitance. When the annealing temperature is 650 °C, the C–V curve shows a maximal memory window and the value is about 0.4 V. However, when the annealing temperatures are 600 and 700 °C, the memory windows decrease to 0.21 and 0.2 V, respectively. The value of the memory window is closely related to the polarization of the ferroelectric layer and the charge injection from the substrate or/and the metal gate electrode [5]. It is reported that the ferroelectric polarization of the BVO thin films increases with the annealing temperature in range of 600–700 °C [7], which can lead to lager memory window. When the annealing temperature reaches 700 °C, the interfaces characteristic of BVO/Si would deteriorate to some extent. Consequently, charge injection at this interface alters correspondingly and in turn can affect the memory window significantly. This may be the main cause for the decrease of the memory window at 700 °C, as shown in Fig. 3.

Figure 4 shows the memory window of the C–V characteristics for PT/BVO/Si structure vs different sweep voltages at 1 MHz. The C–V curves also show hysteresis loops with a clockwise trace as expected for MFS capacitor fabricated on p-type Si. At the sweep voltage 2, 3 and 4 V, the memory window value of the MFS structure are 0.05, 0.11 and 0.42 V, respectively. It is obvious that the value increases slightly with the applied voltage and shows a maximum value of 0.42 V when the sweep voltage is 4 V. The increase of the memory window can be explained by the fact that the polarization and the coercive voltage are being increased with the applied voltage [2, 5]. With the increase of the sweep voltage above 4 V, the memory window decreases. This could be attributed to the charge injection [2]. The results indicate that the memory window increase due to the increase of ferroelectric polarization for higher sweep voltage, while the injection charge which appears at much higher sweep voltage (above 4 V) may decrease the memory window.

4 Conclusions

In summary, the BVO thin films with good structure and morphology were prepared on p-type Si substrates by sol–gel spin coating method. The XRD results indicate that the prepared BVO thin films show high c-axis orientations. AFM results reveal the homogeneous distribution of grains, and the grain size was found to increase with the annealing temperature. The C–V characteristics of the Pt/BVO/Si MFS structure have been discussed in terms of the competition between ferroelectric polarization and charge injection. The maximum value of memory window of BVO was about 0.42 V at the gate bias of 4 V for the sample annealed at 650 °C.

References

J.F. Scott, A.P. Araujo, Science 246, 400 (1989)

N. Kumari, J. Parui, K.B.R. Varma, S.B. Krupanidhi, Solid State Commun. 137, 566 (2006)

M.H. Tang, Z.H. Sun, Y.C. Zhou, Y. Sugiyama, H. Ishiwara, Appl. Phys. Lett. 94, 212–907 (2009)

T.L. Ren, T.Q. Shao, W.Q. Zhang, C.X. Li, J.S. Liu, L.T. Liu, Z.J. Li, Microelectron. Eng. 66, 554 (2003)

C.S. Yeh, J.M. Wu, Appl Phys Lett 93, 15401 (2008)

B.E. Park, K. Takahashi, H. Ishiwara, Appl. Phys. Lett. 85, 448 (2004)

M. Guo, H.M. Deng, P.X. Yang, J.H. Chu, Mater. Lett. 63, 1535 (2009)

N. Kumari, S.B. Krupanidhi, K.B.R. Varma, Appl. Phys. A 91, 639 (2008)

N. Kumari, S.B. Krupanidhi, K.B.R. Varma, Sci. Eng. B 138, 22 (2007)

K. Tsukada, T. Nagahama, M. Sohma, I. Yamaguchi, T. Tsuchiya, T. Manabe, S. Suzuki, T. Shimizu, S. Mizuta, T. Kumagai, Thin Solid Films 425, 97 (2003)

Acknowledgments

This work was supported by the National Natural Science Foundation of China (No. 60990312), the State Key Basic Research Program of China (2007CB924902), Shanghai Leading Academic Discipline Project (B411) and Science and Technology Commission of Shanghai Municipality (10JC1404600).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhang, Z., Deng, H. & Yang, P. Capacitance–voltage characteristics of Pt/Bi2VO5.5/p-Si structures. J Mater Sci: Mater Electron 22, 488–491 (2011). https://doi.org/10.1007/s10854-010-0165-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-010-0165-0