Abstract

With scaling of the gate length downward to increase speed and density, the gate dielectric thickness must also be reduced. However, this practice which has been in effect for many decades has reached a fundamental limitation because gate dielectric thicknesses in the range of tunneling have been reached with the SiO2 dielectric layer for MOSFETs. Consequently, the gate dielectrics with higher dielectric constants, dubbed the “high-κ”, which allow scaling with much larger thicknesses have become active research and development topics. In this review technological issues associated with the likely high-κ materials which are under consideration as well as challenges, and solution to them, they bring about in the fabrication of Si MOSFET are discussed. Moreover, in order to squeeze more speed out of CMOS, channels for both n- and p-type MOSFET enhanced with appropriate strain and the concepts behind them are discussed succinctly. Finally, the longer term approach of replacing Si with other channel materials such as GaAs (InGaAs) for n-channel and Ge for p-channel along with technological developments of their preparation on Si and likely gate oxide developments are treated in some detail.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Since the inception of the integrated circuit in 1959, the Si based semiconductor industry has enhanced the performance of integrated circuit following Moore’s law [1]. By about 1965, Gordon Moore observed that for silicon-based integrated circuits the number of transistors per square centimeter doubled every 12 months. The doubling took hold in the industry and the industry even at the time of the writing lives or dies by the observation providing a tremendous impetus to stay on or about the line extrapolated by Moore’s law. Actually, throughout the 1970s and 80s, the doubling time was closer to 18 months. However, for the past few years, the doubling time has retuned to about 12 months. Having to follow Moore’s law for the past four decades forced the leading-edge companies to manufacture devices with feature sizes below 100 nm (will be approaching even under 10 nm). As can be expected, with shrinking dimensions we have arrived at a point where the device structures, device concepts, choice of dielectrics, etc., used would have to be reevaluated.

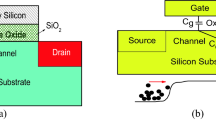

At the heart of the Si revolution, is the metal oxide semiconductor FET, MOSFET. Use of n- and p-channel varieties in unison is the basis for complementary MOSFET. Integrated circuit fabrication based on MOSFET relies on amorphous, thermally grown SiO2 as a gate dielectric. The Si:SiO2 system offers several important materials properties (and therefore electrical properties) including a stable thermodynamic Si:SiO2 interface in addition to superb electrical insulation and interfacial bonding properties. In modern CMOS technology, defect charge densities associated with the Si:SiO2 interface are on the order of 1010/cm2, mid-gap interface state densities are about 1010/cm2 eV, and hard breakdown fields in excess of 10 MV/cm are routinely obtained and are therefore expected regardless of the device dimensions. These outstanding electrical properties clearly present a significant challenge for any alternative gate dielectric candidate.

With scaling, however, in order to avoid severe short channel effects SiO2 must be reduced to the point that leakage current becomes unacceptable. Therefore, a replacement for SiO2 must be found. In more detail, with increasing demand for increased speed and device density, the device dimensions are continually scaled down following what is termed as the Moore’s law. However, reduction of gate dimensions, the corner stone of which is the reduction of the gate or the channel length, requires decreasing oxide thickness in order to prevent the short channel effect and or render it manageable. The thinness required by SiO2 even before the 65 nm node technology (projected to go down to 16 nm by 2016) and lower technology is such that direct tunneling, therefore the undesirable gate leakage current is substantial and increases exponentially with decreasing thickness. This calls for other dielectrics with much higher dielectric constants, thus the term high-κ dielectrics which allow maintenance of the gate oxide capacitance (or the inversion capacitance) needed for reducing short channel effects while still using sufficiently thick oxide layers to prevent current conduction through it. Being such a crucial part of the highly successful CMOS technology naturally paved the way for extensive research and developmental activities to find a replacement for SiO2. At the very minimum, in addition to compatibility with CMOS processing, the high-κ dielectric must have a large dielectric constant, large band discontinuity for both the conduction and valence bands which means large bandgap and low interface and bulk trap density. In this review, after making the case for a different gate dielectric, brought about by scaling trends, various gate dielectrics that have and or are being explored with their associated technologies will be discussed. Because processing is an integral part of any CMOS development, this issue will be discussed as well. This then will pave the way for a discussion of the techniques used to increase speed performance of CMOS as well as the methods under consideration beyond Si channels and gate dielectric related developments.

In this review paper, at first we concern about the growth issues for the high-κ materials. Then we will focus on the fabrication and processing issues for them. At last the high-κ dielectric materials properties and the integration of the high-κ materials with the MOSFET engineering will be discussed. The second motivation of this review paper is to discuss the channel materials and how to increase the MOSFET running speed. We will discuss the GaAs and Ge channel materials for the replacement of the Si n- and p-MOS.

2 Scaling and need for high-κ dielectrics

Following a dramatic ride, characterized by exponential growth, spanning over several decades with relentless scaling to ever smaller dimensions for higher packing density, faster circuit speed, and lower power dissipation, CMOS technology has become the dominant technology for very large scale integration (VLSI). These advances led to computers and networks with far superior performance and dramatically reduced cost per function. In fact it can safely be stated that the semiconductor manufacturing is the only one that provides better performance for less with each passing day. As the device dimensions are scaled downward for increased speed and reduced area per device, avoidance of short channel effects dictate that the oxide thickness be reduced. And finally, the industry is encountering fundamental and technological challenges, some fundamental in nature, which it did not face before [2].

Until present, the CMOS circuit experienced scaling with little or no concern about fundamental limits. Accompanying developments included halo-doping of source and drain (1985), which paved the way for scaling of the channel lengths down to ∼0.1 μm, the basic device structure and thus physics underlying the operation of the MOSFET has remained substantially unchanged over all these years. Together several factors make further evolutionary change difficult for sub-0.1 μm gate lengths such as lithography, controlling diffusion profiles, and generating sufficiently shallow and low-resistance contacts. However, new limits in fundamental nature are being faced, among which are tunneling through thin oxides and narrow depletion layers, as well as increasing variability in device characteristics caused by random impurities due to much reduced device volume. Among these factors, the gate oxide leakage current is considered the most restrictive. Gate oxide thickness must be reduced as channel length is reduced to avoid short channel effects (simply loss of drain current control by the gate bias and increased effect of drain bias on drain current even in what would otherwise has been the saturation regime). This causes a reduction in the ON/OFF current ratios (i.e. exponentially larger off-state drain currents for a given on-state current). Moreover, reduced oxide thicknesses result in increased gate leakage current which is a formidable problem particularly for large density circuits. In addition to the leakage current, the reverse short channel effect is another point of attention for scaling. Halo doping near the source and drain terminals in a submicron MOSFET serves to reduce the size of the depletion region in the vicinity of these junctions. For short channel lengths the halo doping of the source overlaps with that of the drain, increasing the average channel doping concentration, and thus increasing the threshold voltage. This increased threshold voltage requires a larger gate voltage for channel inversion. The conventional SiO2 thin gate dielectric cannot withstand the higher gate voltage bias in a submicron MOSFET.

The thinness required by SiO2 even before the 65 nm node technology (the actual gate length is projected to go down to 6 nm by 2020) (Fig. 1) and lower technology is such that direct tunneling, therefore the undesired gate leakage (Fig. 2) becomes substantial and increases exponentially with decreasing thickness. This calls for other dielectrics with much higher dielectric constants, thus the term high-κ dielectrics which allow maintenance of the gate oxide capacitance (or the inversion capacitance) needed for reducing short channel effects while still using sufficiently thick oxide layers to prevent current conduction through it (Fig. 3). The benefits of high-κ dielectrics can clearly be gleaned from Eq. 1 where in the equivalent thickness for a certain gate capacitance made of SiO2 can be increased by a factor of \( {{\left( {\varepsilon |_{{{\text{high}}\hbox{-}\kappa }} } \right)}} \mathord{\left/ {\vphantom {{{\left( {\varepsilon |_{{{\text{high}}\hbox{-}\kappa}} } \right)}} {{\left( {\varepsilon |_{{{\text{SiO}}_{{\text{2}}} }} } \right)}}}} \right. \kern-\nulldelimiterspace} {{\left( {\varepsilon |_{{{\text{SiO}}_{{\text{2}}} }} } \right)}} \). Approximating the dielectric constant of SiO2 with 4, a 1 nm thick SiO2 gate dielectric (referred to as the equivalent thickness) can be replaced with a 4 nm thick high-κ dielectric with a relative dielectric constant of 16.

Finding a material to replace SiO2 is a more than just a formidable challenge because SiO2 is nearly a perfect dielectric whose only drawback is the relatively low ε, and it turned out to be the major issue placing a roadblock on the long and successful saga of SiO2 dating back to birth of the microelectronics industry based on Si. Despite the fact that there are many dielectrics with much higher dielectrics constant ε (20–100) at present than that of SiO2 it is a formidable task to replace SiO2 because of such issues as lower channel-dielectric interface quality, reliability, high leakage current. To reiterate the main criteria for a gate dielectric include band offsets that block hot charge carriers, chemical stability in contact with both the silicon substrate and the gate material, and low density of interface and bulk states. Attempts to introduce high-κ dielectrics into CMOS technology began as early as 70–80s, but was delayed because of their high defect concentrations, particularly O vacancies, which resulted in charge trapping, transient threshold voltage shifts, and a degradation of Si carrier mobility due to Coulombic scattering. There have been several excellent review papers on different aspects of high-κ dielectrics [3, 4] but the field is progressing very rapidly and is on the verge of converging on a successful replacement for SiO2. De Almeida and Baumvol [4] analyzed in details reaction and diffusion properties of dielectric/gate and dielectric/channel interface. Wilk et al. [3] reviewed the status of the of the high-κ dielectric studies, vista 2000, which was followed by a similar review by Wallace and Wilk [5], vista 2003, with some updates. Since this area of research is studied very intensively, for past few years a great number of publications on high-κ dielectrics appeared, which warrants a reexamination of the field at least succinctly. In deference to what has already been reported, the focus of the present discussion will be on the very recent progress.

HfO2 and ZrO2 high-κ dielectric oxides have received greater interest, commensurate with a large number of reports which has been made devoted to these materials. Also an old timer, Ge, has gained increased attention as a channel material for high mobility FET devices, due to higher low-field intrinsic carrier mobility than that of silicon. Thus, this semiconductor has been the focus of research for many groups and it was used as a substrate for high-κ dielectric growth, therefore, problems facing these materials as a channel layer for high-κ dielectrics in the context of MOSFETs will be discussed in this section. Also the issues related to the passivation and etching of high-κ dielectrics will be discussed.

There are different requirements for DRAMs and metal–oxide–semiconductor field-effect transistor (MOSFET) applications. This then follows that depending on the aim there are different requirements for the dielectric layers to be grown as well. For example, memory capacitors require low leakage current and high capacitance density (per unit area) for charge storage, but the interface quality is not as critical as the switching device. Some level of control of the interface is required primarily to limit interfacial reactions to keep the total capacitance high. Since the main purpose of the capacitor is to store charge, current transport along the interface is not critically important. Also no electric field penetration is required below the bottom electrode. Thus, the key parameters to optimize for DRAMs applications are the leakage current and the dielectric constant, making the main the purpose is to obtain films with dielectric constant (high-κ) and low leakage current. In contrast, the main requirement of a MOSFET device is that electric field penetrates into the Si channel to modulate carrier transport, and therefore, the quality of the dielectric-channel interface must be very high.

The dielectric layer should be uniform in crystalline structure and in physical properties. For this reason the dielectric layer should be either amorphous or extremely high quality single crystalline. All SiO2 dielectric layers used in SiO2/Si based MOSFET and DRAM technologies today are in the amorphous state. There are a number of factors which favor amorphous layers: (i) there is only a single amorphous structure for a given composition that implies uniform physical properties; (ii) there are no dislocations or grain boundaries; (iii) stress can be eliminated by moderate topological variations in a random network rather than through misfit dislocations; (iv) a continuous random network tends to minimize electrically active defects. For these reasons less than simply perfect crystallization is an undesirable feature since it introduces non-uniformities in the scale of grain size. Polycrystalline dielectrics have non-uniform leakage distribution and can give rise to large statistical variations for nanometer sized device across the chip. Because the grain boundaries in crystallized gate dielectrics can serve as pathways for Si, oxygen and or dopant diffusion in or out of the gate the gate dielectric, whichever is applicable, and even to the channel region in the silicon bulk, it is imperative that they be reduced and if not totally eliminated.

There are a number of high-κ dielectrics, which have been and or are actively being pursued for replacing SiO2. A list of dielectrics and their physical properties such as the dielectric constant, band gap, conduction band offsets relative to Si and Ge, and crystal structures is tabulated in Table 1. Beyond silicon dioxide (SiO2) and silicon nitride (Si3N4), a number of high-κ dielectric candidates such as gadolinium oxide (Gd2O3) [6], magnesium oxide (MgO) [7], erbium oxide (Er2O3) [8], neodymium oxide (Nd2O3) [9] praseodymium oxide PrO2 [10], cerium oxide (CeO2) [11, 12], aluminum oxide (Al2O3), lanthanum aluminum oxide (LaAlO3), La2O3 (lanthanum oxide) [13, 14], yttrium oxide (Y2O3) [15], tantalum pentoxide (TaO5) [16, 17], titanium dioxide (TiO2) [18], zirconium dioxide (ZrO2) [19], zirconium silicate (ZrSiO4) [20], hafnium oxide (HfO2) [21, 22] hafnium silicate (HfSiO4) [23], dysprosium oxide (Dy2O3), strontium titanate (SrTiO3), etc. have been proposed and investigated with HfO2 getting special attention.

To be amenable to commercial production, high-κ materials for both capacitors and transistors must simultaneously satisfy a set of requirements such as low leakage current, large band offsets with Si, chemical and thermal stability, and low density of interface states. The TiO2 and Ta2O5 systems have been heavily studied for high-κ applications owing to their high permittivity of κ = 30–110, depending on the crystal structure and method of deposition. However, these dielectrics suffer from such ailments as high leakage current and relatively poor chemical stability. Among the above mentioned potential candidates to replace SiO2 as the gate dielectric, hafnium dioxide (HfO2) and somewhat early on zirconium dioxide (ZrO2) were found to be the most promising combining high dielectric permittivity and thermal stability with low leakage current due to a reasonably high barrier height that limits electron tunneling. Various pertinent properties of the abovementioned oxides are also tabulated in Table 1 with a graphical representation of the known band alignment between Si and various high-κ dielectrics shown in Fig. 4. Currently HfO2 is under intensive investigations with the emphasis being placed on interface states, gate compatibility, structural, physical and chemical stability at both the gate electrode/dielectric and dielectric/channel interfaces, and process compatibility.

3 High-κ dielectric layer growth

Because gate oxide is the most critical component of a MOSFET, extremely reliable high-quality high-κ gate dielectric thin films are imperative. For this reason gate oxide film growth of the films is a very important issue and as such received considerable attention. Several thin film growth techniques such as reactive thermal evaporation [26], atomic layer deposition (ALD) [27, 28], chemical vapor deposition (CVD) [29, 30], pulsed-laser deposition (PLD) [31], and molecular beam-epitaxy (MBE) [32, 33] have all been employed in many efforts to obtain high-quality high-κ dielectric thin films. The properties of the thin films so produced have been reported to be closely dependent on the growth method. Studies to glean an understanding of any correlation amongst the properties of the films, the interfacial layers, and growth conditions have been undertaken. Let us now discuss the deposition methodologies applied to high-κ dielectrics. Below a succinct review of the above mentioned deposition techniques to high-κ material is given.

3.1 Atomic layer deposition (ALD)

The atomic layer deposition (ALD) is one of the methods for preparing ultra thin metal-oxide layers with excellent electrical characteristics and near-perfect films because of the layer-by-layer nature of the deposition kinetics. An ideal ALD process proceeds as a self-limiting mechanism. The growth surface becomes saturated with the governing precursor so that the deposition automatically self-limits at one or two monolayers. ALD is carried out by the surface exchange reactions between the chemisorbed metal-containing precursor fragments and adsorbed nucleophilic reactant molecules. Therefore, the growth rate is independent of the precursor dose but surface-controlled. The ALD mechanism involves a full cycle [34], and one cycle consists of four steps, namely supplying the first and second precursor gases to the surface repeatedly and alternatively until a film of desired thickness is obtained, as shown in Fig. 5. In this 4-step ALD process, the substrate surface is first exposed to a pulse of the first precursor and the chemical absorption of the first precursor is allowed to take place on the substrate surface. Then, an inert gas is allowed into the growth chamber to remove the remaining and un-reacted precursors. Thirdly, the second precursor is introduced into the chamber and allowed to react with the precursor absorbed on the substrate surface. A complete atomic layer deposition takes place during this step. Lastly, the inert gas is allowed into the growth chamber again to expel the gaseous reaction by-products and un-reacted precursors.

Schematic illustration of an ALD growth cycle (1–4) leading to the formation of an imaginary binary oxide film of metal (white circle) and oxygen (gray circle). L refers to the precursor ligand [34]

Similar to other CVD processes, there are many key factors with which one must be concerned and must optimize. Suntola et al. [35] introduced the concept of “ALD-window” to indicate the temperature range where thin film growth proceeds by surface control in an ALD-mode, just as shown Fig. 6. Outside the ALD-window, the growth is limited by precursor condensation, decomposition, and insufficient reactivity.

Scheme of (a) an ALD processing window limited by (b) precursor condensation, (c) insufficient reactivity, (d) precursor decomposition and (e) precursor desorption. If the deposition rate is dependent on the number of available reactive sites as in (f), actual ALD window cannot be observed [34]

As mentioned above, in this so-called surface-controlled ALD mechanism, the growth rate is independent of the precursor pulse length (dose). The only requirement is that there are sufficient precursor molecules (more is fine) to satisfy the adsorption sites on the surface. The excess and un-reacted precursors are then blown away by inert gas purging. However, many of the recently used organometallic precursors for oxide films do not exhibit a distinct ALD window. Thus, the deposition rate in these processes is dependent on the temperature, while the self-limiting feature of the ALD processes remains. Furthermore, this method is known to have a relatively high concentration of residual impurities due to the use of precursors and thus is unfavorable to the quality of the gate dielectric. From this point of view, we can see that the choice of the precursor is very pivotal in improving the crystal quality of ALD grown films.

Many varieties of precursors have been used for the high-κ dielectric material deposition in an attempt to find the optimal growth window for each of the various oxide materials and reduce the by-product contamination. In the case of the most popularly studied high-κ oxides, ZrO2 and HfO2, halide, metal alkoxide, and alkylamide precursors have been widely used for the ALD growth. For instance, the halide precursors ZrCl4 [36], ZrI4 [37], HfCl4 and HfI4 [37] have been used for the crystalline ZrO2 and HfO2 film deposition by ALD. Aarik et al. [38] used HfCl4 and H2O as the precursors and found that the layer-by-layer growth is self-limiting at temperatures above 180 °C. By using the same precursor, Cho et al. [39] found that the film thicknesses decreased with increasing deposition time after reaching a certain maximum value at 300 °C and 400 °C due to the enhanced dissolution of SiO x into the growing films at these temperatures.

Kukli et al. [40] used the alkoxide complex [Hf(mmp)4] and H2O precursor to deposit HfO2 on borosilicate glass and Si(100) substrates by ALD in the temperature range of 275–425 °C. It was shown that the adsorption of hafnium complex was not entirely self-limiting, probably because of the thermal decomposition of the precursors. Crystalline films containing the monoclinic HfO2 phase were grown at temperatures exceeding 300–325 °C. The C–V curves of the as-deposited films (Fig. 7) showed a clockwise hysteresis due to the presence of positive mobile charge in the films. The voltage shift is in the range of 0.5–1 V. The effective permittivities of the dielectrics in Al/HfO2/Si structures varied between 12 and 17. The refractive index measurement shows a value about 1.8–2.0, which is less than the value (2.0–2.2) obtained from the samples deposited by using the HfCl4 precursor. This means that the alkoxide complex [Hf(mmp)4] precursor led to less dense films than those grown from HfCl4.

Capacitance–voltage and dissipation curves measured for Al/HfO2/SiO2/p-Si(100) deposited by ALD using [Hf(mmp)4] and H2O precursor with capacitor at AC signal frequency of 500 kHz [40]

Lee et al. [41] obtained HfO2–Al2O3 films with EOT 22.5 Å and low leakage current (1.0 fA/cell at 1.65 V) by using the liquid alkylamide complex [Hf(NMeEt)4] precursors. Additionally, the HfCl4 precursor also has been tried and compared with the [Hf(NMeEt)4] precursor. Compared with the HfCl4 precursor, the ALD grown HfO2 dielectric films have better step coverage and higher throughput. Relying on these results, those authors stated that the HfCl4 precursor has two major drawbacks. The first one is the poor step coverage. The second one is that the saturation time of the self-limiting reaction for HfCl4 which is directly proportional to the process time is longer than that of the [Hf(NMeEt)4] precursor.

Amorphous praseodymium oxide (PrO2) films have been explored as well for gate oxides. Kukli et al. [42] have grown the PrO2 amorphous films on Si (100) substrates in the temperature range 200–400 °C by using Pr[N(SiMe3)2]3 belonging to the trigonal-bipyramidal coordinated lanthanide (III) system and H2O as the precursor. Crystallization was attained after annealing at 900–1000 °C, and X-ray diffraction data indicated that the composition of the films was Pr9.33(SiO4)6O2. In addition, the films were found to contain considerable amounts of residual hydrogen and residual or diffused silicon. The effective permittivity of 70–100 nm thick films was in the range of 14–16. Annealing at 800 °C in nitrogen increased the effective permittivity slightly to 15.6–21 and decreased the rechargeable trap density. It is evident in Fig. 8 that annealing at 800 °C caused the capacitance to increase and the hysteresis voltage shift decrease. There are two reasons for the reduction in capacitance. Firstly, after annealing a SiO2 interfacial layer is formed. Secondly, the Si atoms diffuse into the metal oxide followed by the oxidation of the diffused Si. The differences in the electrical properties after nitrogen and air (oxygen-assisted) annealing could be attributed to the differences in the microstructure formation. Wakiya et al. [43] suggested that for slightly oxygen-deficient PrO2 the annealing atmosphere caused different phase transitions. In nitrogen ambient, the C-type rare earth structure was detected between 700 °C and 1000 °C before the decomposition of the defect fluorite into the A-type rare earth structure. In oxygen ambient, however, such a transition was not detected.

Capacitance–voltage curves of Al/PrO x /Si capacitors based on 100 and 78 nm thick PrO x films grown on HF etched Si(100) at 250 and 300 °C, respectively, in as-deposited and annealing states. Labels denote the growth temperature and annealing ambient. Annealing was carried out at 800 °C for 1 min in N2 and 3–4 min in air [42]

We have so far discussed the ALD deposition of the HfO2, ZrO2 and PrO2 with aid of precursors. The critical issue for improving the oxide quality seems to center around the choice of precursors with lower contamination and ability to self-limit. In addition to HfO2, ZrO2 and PrO2, other oxide films prepared by ALD deposition and various precursors have been reported. The details for them will not be discussed here due to space limitation. However, those oxides along with the precursors used for their growth are listed in Table 2.

3.2 Pulsed-laser deposition (PLD)

The pulsed-laser deposition (PLD) method is also increasingly being utilized to prepare a wide variety of high-κ dielectric materials in thin-film form owing to its simplicity and fast deposition rate [31]. More importantly, PLD is known for the quality of the layers grown at relatively low substrate temperatures among the thin-film deposition methods. Ratzke et al. [49] applied PLD to deposit the thin films of high-κ praseodymium oxide (PrO y ) and hafnium oxide (HfO x ) on Si substrates using the third harmonic of a Nd:YAG laser for ablation. In this investigation, the two oxide materials were compared with their morphology, chemical composition, and crystalline structure, in particular that at the interface, in mind. The effect of the deposition temperature was also investigated. Both oxide films were observed to exhibit a grainy structure when deposited at substrate temperatures below 750 °C with the grain size increasing from 40 nm at room temperature to about 100 nm at 750 °C. The PrO y films were noted to be much more uniform than HfO2. HfO2 showed increasingly larger holes which penetrated several nanometers into the silicon substrate. In addition, the interface was noted as being significantly different for both materials; a silicate formation for PrO y and a rich abundance of SiO2 and a silicide for HfO2.

Desbiens and El Khakani [50, 51] have grown high-κ silicon oxynitride (SiO x N y ) thin films by using a hybrid deposition process. Those authors combined the PLD plume of silicon species in an oxygen background with a remote plasma-based atomic nitrogen source (ANS) to complete the growth to help increase nitrogen incorporation into the SiO x N y films. At the highest N content (35%), the films exhibited a high-κ value of about 9.5 and a breakdown field as high as 19 MV/cm. The Poole–Frenkel emission with compensation was noted to dominate the conduction mechanism in the SiO x N y films, which typically leads to current leakage. It was noted that the dielectric properties of the SiO x N y thin films could be improved by adding more N, which increases the Si–N bond in the films.

Zirconium silicate films on n-Si (100) substrates with EOT = 1.65 nm have been achieved by using the PLD [52]. After a rapid thermal annealing (RTA) in N2 at 800 °C, the films remained amorphous. However, the amorphous Zr silicate crystallized at 830 °C and the 900 °C RTA led to the phase separation.

Kitai et al. [53] deposited several lanthanoid oxide thin films such as those of PrO x , Sm2O3, Tb4O7, Er2O3 and Yb2O3 on Si(100) wafers by PLD. PrO x film showed thinner (EOT) and lower leakage current. A PrO x thin films with EOT of 4.4 nm prepared at room temperature in high vacuum showed only slight growth of the interfacial layer, with a large hysteresis. After annealing at 600 °C, the leakage current and the hysteresis improved. An EOT of 2.6 nm and a leakage current density of 2 × 10−3 A/cm2 at −1 V were achieved after a 600 °C annealing step.

3.3 CVD growth

Metal orgranic chemical vapor deposition (MOCVD), which is distinguished from CVD by the organometallic sources used, has been widely used in the epitaxy of semiconductor materials and their heterostructures. Especially, in the III–V compound semiconductor materials system, MOCVD is the most widely used equipment for production. Recently, as the high-κ dielectric materials came under intense investigations, MOCVD became a good candidate for the high-κ material deposition on Si substrates. However, what is different from the deposition of the III–V compound semiconductor materials is that many oxide precursors used for the high-κ materials by MOCVD deposition have low pressure and low thermal stability, both of which are detrimental to growth. Therefore, it is necessary to modify a standard MOCVD system to allow e.g. liquid injection where the precursors are dissolved in a solvent, for this technique to be applied fully to high-κ dielectric deposition. Even then, there remain some requirements for the precursors to meet. The precursors must be soluble and stable in the same liquid solution, but they must also not react with each other in the same solution. In addition, it would be convenient for the precursors to have nearly the same vapor pressure at conveniently attained temperatures to avoid multiple refrigeration/heating units that house the precursor sources. To fulfill the all the aforementioned requirements places sever restrictions in the choice of precursors. Below we discuss a few of the reports dealing with the MOCVD deposition of high-κ dielectrics by using different precursors for different oxide layers.

Van Elshocht et al. [54] investigated the effect of MOCVD growth temperature on the physical properties of the HfO2 layers deposited by MOCVD. The organic precursor, tetrakis-diethylamidohafnium (TDEAH), and O2 was used for the MOCVD deposition on Si (100) wafers. From the total thickness measurement of the HfO2 layers, those authors found that the growth rate is dependent on the growth temperature. The deposition rates for the samples processed at 485 °C and 600 °C are almost identical, but less than the growth rate attained at 300 °C. From the RBS data it was found that the Hf atoms in these three samples are quasi identical, which means that the deposition at lower temperatures results in layers with a lower density. In Fig. 9, the densities of different samples deposited at different temperatures are shown. Clearly the density increases with increasing layer thickness and is distinctly lower for layers deposited at 300 °C. The difference in the layer density, caused by the growth temperature, naturally has an effect on the electrical performance of the HfO2 layers. For example, the leakage current density was observed to be much higher for layers that are deposited at 300 °C as compared to layers deposited at 485 or 600 °C (Fig. 10), which yields functional MOS capacitors (EOT = 1.8–2.0 nm). Hence, a low density HfO2 layer appears to result in an increased gate leakage current.

Density (g/cm3) as function of the HfO2 thickness for layers deposited at 300°C (circle) vs. 485 or 600 °C (square) [54]

I–V curves for HfO2-based gate stacks deposited at 300, 485, and 600 °C [54]

Marshall et al. [55] used the alkoxide precursors to deposit hafnium aluminate thin films by the liquid injection MOCVD method. The experiments showed high purity films without any detectable amount of carbon. The (HfO2) x (Al2O3)1−x films showed a structural transition from crystalline to amorphous when the gas-phase concentration of Al precursor was raised from 4% to 7%. While on the topic of liquid injection MOCVD, ZrSi x O y and HfSi x O y have been deposited by this method using the liquid precursors tetrakis(diethylamido)zirconium [Zr(NEt2)3] [56] (for ZrO2 deposition using this precursor, see [57] or tetrakis(diethylamido)hafnium [Hf(NEt2)4] [58] (NEt2 is N(C2H5)2).

Titanium oxide (TiO2) high-κ dielectric layers have also been deposited on the Si0.3Ge0.7 substrates by plasma enhanced chemical vapor deposition (PECVD) at low temperatures (150 °C). The effects of annealing in pure nitrogen ambient on the electrical properties of the TiO2 films were studied by Chakraborty et al. [59] The annealing step was performed in the temperature range of 400–600 °C. Good electrical performance for the gate dielectrics was observed for the dielectric films annealed up to 500 °C in terms of the interface state density, leakage current, and charge trapping properties. Annealing at 600 °C was found to degrade the electrical properties due to Ge segregation and subsequent diffusion into the TiO2 layer.

3.4 MBE growth

Molecular beam epitaxy (MBE) is a very powerful and sophisticated technique, which can precisely control the film growth parameters at the atomic scale and as such it provides uniform, high-quality films. However, up to now there have been only a few publications regarding the MBE growth of ultrathin oxide dielectric films which is to some extent due to the extremely slow growth rate if e.g. the HfO2 is formed by the reaction of metallic components of oxides and molecular oxygen beams and the relative unfamiliarity of the Si processing personnel with MBE.

Investigations have been carried out in an effort to grow high quality high-κ dielectric films by using a modified MBE system. For example, Lu et al. [60] employed a laser molecular beam epitaxy (LMBE) system to grow amorphous HfO2 on (100) n-type silicon. LMBE has been interested to fabricate the oxide based electronics, which combines the merits of both PLD and conventional MBE for depositing films with atomic scale thickness control. First a hafnium metal layer was deposited onto the Si substrate in an ultrahigh vacuum of 8 × 10−9 Torr at 200 °C, then the substrate temperature was raised to 500 °C, and the HfO2 film was deposited onto the Hf layer in Ar/O2 ambient. After growth, a post deposition anneal was carried out at 500 °C for 30 s in N2 gas with residual O2 to oxidize the Hf metal layer by the O ions penetrating during annealing. It was found that the growth of the interfacial layer depends strongly on the oxygen partial pressure in the deposition process. The HRTEM images show the as-deposited Hf layers have good interface quality on Si substrates. The interface between the amorphous HfO2 and Si still remains smooth even after the annealing step. From the I–V measurements, it can be seen that the sample with 15 nm HfO2 film shows the leakage current density of 1.5 × 10−2 A/cm2 at 1 V, which is at least 4 orders of magnitude lower than that of SiO2 with the same equivalent thickness of 1.3 nm.

Hong et al. [61] deposited the HfO2 dielectric layer on p-type Si (100) substrate by using a variant of MBE, the metalorganic molecular beam epitaxy (MOMBE), with hafnium tetrabutoxide Hf(O·t-C4H9)4 as the Hf precursor. It was found that the dielectric constant of the HfO2 layer increases with the oxygen flow rate during deposition. However, the excess oxygen flow also increases the density of trapped charges. I–V measurements indicate leakage current densities of 2.5–2.7 × 10−2 A cm−2 at −1.5 V gate voltage. The monoclinic phase of HfO2 crystal structure was found to be dominant with a dielectric constant κ of approximately 13–16 and the equivalent oxide thickness (EOT) of approximately around 43–52 Å. Vellianitis et al. [62] investigated the lanthanum-based high-κ gate dielectric epitaxy by MBE. The perovskite-like LaAlO3 (LAO) and pyrochlore La2Hf2O7 (LHO) were grown on the rapid thermal SiO2 (RTO)/Si substrates. The LHO and LAO films were deposited at 550 and 400 °C, respectively. Then, Hf and Al were deposited by an electron beam gun and a high temperature effusion cell with a Ta crucible was used for La deposition. The oxide was formed during metal co-evaporation by exposing the substrate to atomic oxygen beams produced by an RF plasma source. The reactive oxygen atoms promote oxidation and prevent the formation of silicides or silicates. The dielectric permittivity of was estimated to be 14.2 and 18.1 for the LAO and LHO, respectively. The leakage current for the LAO with the EOT of 1.1 nm is only 2 × 10−3 A/cm2 at 1 V gate bias and that of the LHO with the EOT of 1.14 nm is only 4 × 10−5 A/cm2 at 1 V gate bias.

Kwo et al. [15] attempted to achieve amorphous and crystalline Gd2O3 and Y2O3 high-κ dielectric materials by MBE. The crystalline Gd2O3 and Y2O3 films are grown in the (110)-oriented Mn2O3 structure of two-fold symmetry on (100) Si. This two-fold degeneracy was effectively removed by using the vicinal (001) Si substrates with 4° misorientation along \( [1\ifmmode\expandafter\bar\else\expandafter\=\fi{1}0] \). The misorientation surface exposes surface steps of double atomic layers, thus giving monodomain Si steps with a spacing of approximately 80 Å for nucleating the (110) Gd2O3 single variety. The film is predominantly oriented in one type of domain, with \( [001]_{{{\text{Gd}}_{2} {\text{O}}_{3} }} \) parallel to the step edges [110]Si. Along the perpendicular direction, \( [1\ifmmode\expandafter\bar\else\expandafter\=\fi{1}0]_{{{\text{Gd}}_{2} {\text{O}}_{3} }} \) is parallel to \( [1\ifmmode\expandafter\bar\else\expandafter\=\fi{1}0]_{{{\text{Si}}}} \). The amorphous Gd2O3 and Y2O3 films are grown on the standard (001) Si substrates. It was found that the amorphous Gd2O3 and Y2O3 films with smoother morphology have lower electrical leakage than the crystalline films. The grain boundaries in the crystalline films form the conduction path as the major leakage origin [63]. An amorphous Y2O3 film with the thickness of 45 Å (κ = 18) shows the leakage current as low as 10−6 A/cm2 at 1 V gate bias with the EOT of 10 Å. Furthermore, after the forming gas anneal at 400 °C, the leakage current can be reduced again by an order of magnitude, which is about five orders of magnitude better than the best data obtained from a SiO2 gate dielectric 15 Å. From the leakage and high-κ nature, it would appear that Y2O3 could replace SiO2. Without the SiO2 at the dielectric/Si interface, there is not such kind of low κ layer problems encountered in the HfO2 and ZrO2 films caused by the Si diffusion into the oxide layer. At last the amorphous Gd2O3 and Y2O3 remains stable without the dielectric property degradation after 850 °C anneal [64]. In addition to the above mentioned dielectrics, lanthanum-based high-κ gate dielectric epitaxy by MBE has also been reported [65]. The perovskite-like LaAlO3 (LAO) and pyrochlore La2Hf2O7 (LHO) were grown on the rapid thermal SiO2 (RTO)/Si substrates. The dielectric permittivity was estimated to be 14.2 and 18.1 for the LAO and LHO, respectively. The leakage current for the LAO with the EOT of 1.1 nm is 2 × 10−3 A/cm2 at 1 V gate bias and that of the LHO with the EOT of 1.14 nm is 4 × 10−5 A/cm2 at 1 V gate bias.

4 High-κ dielectric processing

The treatment of high-κ dielectric processing is incomplete without consideration of the processes used in Si MOSFET production. The obvious requirements are for the high-κ materials to be chemically stable, unreactive and show no, or next to none, degradation during MOSFET processing after the high-κ is deposited. It is for this reason alone high-κ material development is synonymous with Si MOSFET processing. High-κ dielectric materials processing is an important issue for the integration of these materials with the conventional Si MOSFET technology and their application on the Si MOS scaling engineering. In addition, the optimization of the processing is necessary to improve the oxide layer quality and reliability, and reduce the gate leakage. As in the case of any gate oxide, the gate leakage is one of the overriding issues. Impurity atoms are added to the dielectrics to reduce leakage current as well as making them more compatible with CMOS processing.

N incorporation is a widely practiced technique to reduce the leakage current [66] in SiO2. To follow suite N incorporation into high-κ dielectrics has been intensively studied both experimentally and theoretically, and in the process several useful observations have been made. The suppression of crystallization during high temperature treatment, the reduction of B penetration (from the B doped bulk Si and poly-Si gate, the concentration of which is continually increased to combat short channel effects), and the N-induced increase in the dielectric constant have been reported. Accumulation of nitrogen (N) at the SiO2/Si interface can improve the hot carrier resistance, and the use of oxynitrides can also suppress boron diffusion from the poly-Si gate to SiO2. There have been several reports on incorporating nitrogen into the binary metal oxides to increase the crystallization temperature by high-temperature annealing in oxygen free N2 plasma [67, 68], and NH3 ambient [69]. However, the high-κ dielectric materials nitrided by NH3 lead to increased interface trap density and deterioration of the interfacial carrier mobility.

Umezawa et al. [70] investigated the effect of N at the atomic level on the leakage current through HfO2. It was concluded that N atoms act to reduce the leakage current by coupling favorably with oxygen vacancies (VO) in HfO2 and extract electrons from VO. This results in elevating the VO energy level because of the change in the charge state in VO from neutral to positive charge. Consequently, N incorporation removes the electron leakage path mediated by VO related gap states, by deactivating the VO related gap states. The detailed diagram for this leakage path elimination mechanism is shown in Fig. 11.

Schematic illustration of N incorporation effects: (a) N-induced atomistic relaxation around VO. (1) Electron transfer from VO to N atoms; (2) outward movement of Hf4+ ions due to the increase in Hf4+–Hf4+ Coulomb repulsion; (b) N-induced elimination of leakage paths; (3) drastic VO level elevation due to the decrease in attractive Coulomb interaction from Hf4+ ions around VO; (4) removal of leakage paths due to the elimination of a VO level [70]

Huang et al. [71] used nitrogen instead of NH3 and N2O to control crystallization of gate dielectrics. ZrO2 thin films in this work were deposited on n-type Si (100) wafers using a cathodic arc plasma source in a mixture of oxygen and nitrogen ambient. Introduction of nitrogen into the dielectric layer led to increased crystallization temperature. Moreover, the microstructure of the nitrided ZrO2 thin films was improved as determined by X-ray diffraction and atomic force microscopy characterization.

Fluorine (F) has been found to be an effective passivant for reducing the trap density in conjunction with the high-κ gate dielectrics. The F atoms substitute for the O vacancies (FO) in the gate oxides and reduce the charge trap density. For example, F incorporation in the HfSiON gate dielectric through channel implantation can effectively reduce the trap density and lower the threshold voltage (V th) [72]. Comparing with the gate F implantation, the channel implantation can achieve a larger V th shift. After annealing, the implanted F atoms diffuse into the HfSiN layer and slightly suppress the B diffusion into the HfSiN gate stack. The C–V measurements show a positive V th shift with increasing F implant dose and no observable channel mobility degradation occurs with F implantation. In addition, F incorporation has been reported to reduce the CV hysteresis and positive charge trapping of the gate stack and improve the device reliability [73, 74]. However, the gate leakage increases due to the EOT reduction caused by F incorporation. It is argued that F is a very good alternative passivant for the gate oxide because it is the only element that is more electronegative than O but with comparable bond length [75]. With F incorporation, the F atoms are bonded to metal ion dangling bonds resulting in annihilation of oxygen vacancies. As discussed above, different atoms such as F, N and O can be incorporated into the high-κ films to improve their properties. To this end, various models for the mechanisms involved have been put forth. Further studies must be undertaken to gain a deeper understanding of the fundamental physics underlying the processes involved.

Alternatively, Al and Si can be incorporated into the high-κ dielectric layer to improve its thermal stability. The pure HfO2 dielectric layer crystallizes at about 400 °C. However, in the conventional CMOS processing high temperature annealing is frequently used which causes at least partial crystallization of the otherwise amorphous HfO2 dielectric layer. In order to prevent the crystallization, Al and Si have been added to the HfO2 dielectric layer. It is found that by adding 31.7% Al, the crystallization temperature of the HfO2 dielectric layer can be increased by about 400–500 °C above that for pure HfO2 dielectric [76]. However, this comes at a price in that the Al doped HfAlO dielectric exhibits a lower dielectric constant. Furthermore, addition of Al atoms also introduces negative fixed oxide charge due to Al accumulation at the HfAlO–Si interface, resulting in mobility degradation [77]. The fixed charge acts as scattering centers and degrades the channel carrier transport.

An alternative to Al is adding Si atoms into the dielectric layer instead. With 20% Si, a HfO2 dielectric layer was found to withstand a 5 s rapid thermal annealing step at 1000 °C without any obvious HfO2 crystal components in the layer [78]. Structural analysis indicated that the majority of the HfSiO remained amorphous but a small fraction crystallized into the tetragonal or orthorhombic phase. Moreover, HfSiO can fully phase separate into HfO2 and SiO2 via spinodal decomposition after 900 °C O2 RTA treatment [79]. Another point of interest is that during the dielectric layer deposition a thin interlayer of SiO2 is often formed between the dielectric layers and the Si substrate, which is different from the Si incorporation we discussed above. This kind of SiO2 layer formation adds a parasitic series capacitance on the gate stack and should be avoided [80].

As discussed above, the incorporation of Al and Si into HfO2 films suppresses the crystallization and increases the crystallization temperature which is desirable. However, addition of Al and Si causes the dielectric constant of the films to decrease, which is not desirable. To circumvent this, introduction of La and Y into HfO2 has been studied [81]. By adding La atoms, the crystallization temperature of HfO2 can be raised to 900 °C, without compromising on the dielectric constant (κ = 20 can be achieved). Similar to La, Y doping also shows the advantages beyond that which can be obtained with Si and Al doping. With the increase of Y concentration the dielectric constant increases as well. However, the dielectric constant value reaches a peak as a function of Y concentration.

In parallel to developments of high-κ gate dielectrics, fabrication technologies such as appropriate etching must also be developed. The chief requirement is directionality and anisotropy. Among the etching processes, wet etching is the first choice because of its damage free nature. However, the etching selectivity and rate with this method are of the most concern in addition to etch rate control. It has been reported that the as-grown amorphous dielectric films can be easily etched in a dilute HF (DHF) solution [82]. But the etch rate has been reported to reduce (might be even stagnate) after annealing [83]. By subjecting dielectric film to ion bombardment, the etching rate for the annealed films can be greatly increased, but the caveat is the resultant damage. Saenger et al. [84] attempted to use O2 plasma to treat the annealed HfO2 and ZrO2 samples. After one min and 150 W treatment, the etching time for 2.9 nm HfO2 film reduced from more than 10 min to 4 s in an HF 10:1 solution. For the dielectric films deposited by different method, the etching solution and etching rate are different. Han et al. [85] reported the recipes for some dielectric materials deposited with different methods which is tabulated in Table 3.

As discussed above, wet etching of the high-κ dielectric materials is very sensitive to the etching conditions and the etching rate is not so controllable as compared to the dry etching processes. As far as the high-κ/Si etching selectivity, the RIE etching has been comprehensively studied and the etching conditions have been optimized. As clearly stated and understood already, it is imperative that the high-κ materials be etched with conventional Si processing methods and equipment.

Etching characteristics of HfO2 films grown by atomic layer chemical vapor deposition on p-Si (100) wafers have been investigated by Sha et al. [86]. A high-density electron cyclotron resonance plasma reactor was used to conduct etching in BCl3/Cl2 halogen based chemistry by systematically increasing the BCl3 percentage from 0% to 95% at 5 mTorr and RF power of 300 W with ion energy of 75 eV. The etch rate as a function of the BCl3 percentage is shown in Fig. 12. BCl3 is seen to increase the etch rate significantly reaching a maximum of ∼90 Å/min at 40% of BCl3 before turning downward for higher BCl3 concentrations and turning back up again. Furthermore, the etch rate of HfO2 reached a local minimum at a 80% BCl3 concentration and increased slightly for higher BCl3 percentages reaching an etch rate of ∼50 Å/min for BCl3 without Cl2. The decrease in etch rate following the minimum is caused by the reduced density of the dominant ionic species, e.g. BCl and the dominant ion species in BCl3/Cl2 plasmas. Addition of BCl3 in the Cl2 plasma was also found to improve the etch selectivity of HfO2/Si from ∼0.01 in pure Cl2 plasma to ∼0.9 in pure BCl3 plasma at ion energy of 75 eV. The etch selectivity was improved to above 4 as the ion energies reduced toward the threshold energy in pure BCl3 plasma, as shown in Fig. 13. It is argued that the main difference in etching HfO2 in Cl2 and BCl3 plasmas is the oxygen removal from the oxide film by the reducing chemistry of BCl3. It is difficult for the Cl2 plasma to remove oxygen and induce the subsequent chlorination of the surface, which is the cause of lower etch rates. Addition of BCl3 significantly increases the metal oxide etch rate by enhancing the oxygen removal.

HfO2 etch rate as a function of BCl3 percentage in the BCl3/Cl2 plasmas. The experiments were performed at 5 mTorr and 300 W, and an ion energy of 75 eV [86]

Etch rate of HfO2 and Si, and etching selectivity (dash line) as a function of square root of ion energy in BCl3 plasma at 5 mTorr and 300 W [86]

Nakamura et al. [87] studied etching characteristics of high-κ dielectric materials (HfO2) and metal electrode materials (Pt, TaN) using high-density ECR chlorine-containing plasmas. It was found that the HfO2 etching rates of 5 nm/min and more than 10 etching selectivity over Si and SiO2 can be obtained in a BCl3 plasma source without rf bias. A Pt etch rate of more than 10 nm/min and a TaN etch rate of about 200 nm/min with more than 8 selectivity over HfO2 and SiO2 has been obtained in Ar/O2 with high rf bias and in Ar/Cl2 with low rf bias, respectively.

Etching properties of HfO2 based high-κ dielectric films, i.e. HfO2, HfON, HfSiO, and HfAlO, have been investigated by Chen et al. [88] by using inductively coupled plasma (ICP) of Cl2/HBr/CHF3/CF4/O2. Among HfO2, HfON, HfSiO, and HfAlO, the etch rate of HfSiO increased most significantly with increasing rf bias power due to the difference of the ternary network of Hf–Si–O from the binary network of other films of Hf–O, Hf–N, Si–O, and Al–O. Etch rates of HfON were higher than those of HfO2 due to high Hf–N etch rates compared to the Hf–O etch rates. The HfAlO etch rates were lower than those of HfO2 due to the effect of the low Al–O etch rates. A significant amount of fluorides was shown to exist on the surface after the CF4/CHF3 etching. On the other hand, only a small amount of chloride and bromide existed after Cl2/HBr etching. The amount of residues can be reduced with a high temperature post-treatment step.

Norasetthekul et al. [89] investigated and compared the etch rates and mechanisms for HfO2 thin films grown on Si substrates in three different plasma chemistries, i.e. Cl2-, SF6- and CH4/H2-based plasmas, by varying the RIE r.f. source power, chuck power, and discharge composition. The Cl2- and SF6-based plasmas showed a chemical enhancement in the etch mechanism, with the selectivity for Si over HfO2 between 0.2 and 5 obtained by using these two kinds of plasma sources. The HfO2 etch rates as a function of ICP source power for the three different types of plasma chemistries for a fixed r.f. chuck power are shown in Fig. 14. The resulting d.c. self-biases developed at the sample chuck are shown at the bottom of the figure. In the Cl2- and F2-based discharges, an increase in the ion flux and reactive neutral density produces a rapid increase in the HfO2 etch rate. The removal rates with CH4/H2/Ar chemistry were noted to be slower than with pure Ar sputtering for the same conditions. The polymeric film formed during exposure to the CH4/H2/Ar discharge prevents the surface from being ion bombarded to some extent and thus reduces the etch rate of HfO2. Chlorine-based plasma etching was found to be anisotropic for Si except when very heavily doped n-type. Using chemistries mentioned above, highly anisotropic features in HfO2/Si structures have been attained, as shown in the SEM micrographs of Fig. 15.

HfO2 etch rates as a function of ICP source power in three different plasma chemistries (top) and corresponding d.c. self-biases (bottom) [89]

SEM micrograph of features etched into HfO2/Si structures using Cl2/Ar at 10 mTorr. The photoresist mask has been removed [89]

Pelhos et al. [90] investigated etching characteristics of Zr1−x Al x O y thin films in a high-density helical resonator plasma etcher using BCl3 and Cl2 plasmas as a function of gas composition and ion impact energy. Higher concentrations of BCl3 was noted to enhance the etch rate as well as the selectivity of Zr1−x Al x O y vs. Si. On the other hand, increasing the ion energy was seen to increase the etch rates but decrease the selectivity. Etching rates on the order of 700 Å/min and a 1:1 selectivity were observed. The best selectivity was observed in a pure BCl3 plasma, it was further improved (∼3:2) when the ion kinetic energy was minimized. Angle-resolved X-ray photoelectron spectroscopy revealed that the etching rate of Zr1−x Al x O y did not change with time for the range of Cl2/BCl3 ratios and ion energies investigated, whereas the Si etching rate in pure BCl3 plasma and at zero substrate bias decreased with time as a result of formation of an inhibiting B–Si film on the surface.

5 High-κ dielectric properties and challenges

Along with the production of high-κ dielectric materials, their electrical properties and integration with the conventional Si MOSFET technology have taken the central stage. Compared with the conventional SiO2 oxide and poly-Si electrode, the high-κ oxides present many challenges in the context of compatibility with the Si MOSFET technology. In addition to incompatibility with annealing temperatures used for activating poly-gates, the relatively poor quality, compared to SiO2, of the high-κ oxide materials causes charge trapping and makes the Si MOSFET gate unstable. The channel mobility degradation, and threshold voltage shift induced by high-κ materials also need to be addressed.

One of the first issues in the context of integration with MOSFET is the suitable gate electrode for the high-κ oxide stack. Nominally, the poly-Si is the dominant gate electrode. In the case of the poly-Si processing, annealing above 1000 °C is necessary for the activating the dopants in the poly-Si layer, which is problematic for the high-κ oxides. Therefore, it is imperative, that the high-κ oxide gate be thermally stable and withstand such a high temperature annealing step. For the HfO2 gate dielectric, annealing at high temperatures causes crystallization of amorphous HfO2 into the monoclinic polycrystalline which is not insulating [91]. In addition a 5–10 Å layer of SiO2 is formed at the interface, which eliminates in part the benefits to be gained from high-κ dielectric [92]. The solution for this problem is to add Si, N or Al into the high-κ layer, each one of which acts to increase the crystallization temperature. Zhu et al. [93] investigated the effect of Al incorporation on the HfO2 layer. By adding about 30% Al, the HfO2 crystallization temperature can be increased by 400–500 °C. Furthermore the Al additional also causes an increase of the band gap and a decrease of the dielectric constant of HfO2, the former being beneficial but no so for the latter. Nguyen et al. [94] added Si into the HfO2 layer and found that 20% Si can prevent crystallization at the activation temperature used for the poly-gate.

Another issue of importance in considering any gate oxide, and high-κ dielectric is no exception, is that having to do with the channel carrier mobility degradation. Compared with the SiO2 gate, the high-κ gate layer has soft optical phonons and the long-range dipole associated with the interface excitations would degrade the effective electron mobility in the inversion layer of the Si substrate [95]. Yang et al. [96] summarized the effects of all of the scattering and degradation mechanisms on the inversion channel carrier mobility, as shown in Fig. 16. The addition of Si into the HfO2 enhances the mobility, which is argued as being due to the reduction of the remote phonon scattering [97]. As for the N incorporation mentioned above, the mobility is usually reduced. This is because N incorporation induces fixed charge in the high-κ layer and the resulting Coulomb scattering by the fixed charge reduces the carrier mobility [98].

Schematic representation of factors contributing to carrier mobility degradation in a high-κ oxide layer [96]

The threshold voltage (V fb) shift of the poly-Si/ high-κ stack is another challenge that must be considered. By introducing Si atoms into the oxide layer, the V fb approaches to that for the SiO2 case. In order to bring V fb to within <0.3 V, which is necessary for the CMOS circuits, the Hf content in the oxide layer should be below 20%. N incorporation can also reduce the V fb shift but to a limited extent. The threshold voltage shift has been attributed to the Fermi-level pinning at the interface [99, 100], which in turn has been attributed to the interfacial Si–Hf and Si–O–Al bonds of the HfO2 layer as well as the oxygen vacancies at the polysilicon/HfO2 interface. The interface states partially screen the electric field from the gate electrode, preventing it from modulating the channel fully. Therefore, the efficacy of the gate-induced tuning of the channel carriers is somewhat hindered. An efficient method to reduce the threshold voltage shift is to add a layer of Al2O3 on top of the oxide layer. Kim et al. [101] reported the Fermi-level effect free HfO2 gate stack by depositing an Al2O3 capping layer onto HfSiO x . The p-MOS gate threshold shift was only 0.2 V. It is likely that the negative fixed charge is introduced into the oxide layer by adding Al2O3. Frank et al. [102] used an AlN capping layer to prevent the threshold voltage shift and obtained shift values as low as 0.2 V. Besides an Al2O3 cap layer, other oxides have also been applied to prevent threshold voltage shift. La2O3 has been used to passivate HfSiO on N-MOSFET. The thermally stable band-edge N-metal work function based on interdiffusion of a bilayer gate dielectric stack (La2O3/HfSiO) was attained to reduce the threshold voltage by as much as 0.25V. After 0.5–1.0nm La2O3 deposition by MBE or PVD, a post deposition annealing step was used to cause the La2O3 layer to mix with the HfSiO layer to form N-metal work function with TaN metal gate. Compared with La2O3, a 0.5–2nm Dy2O3 cap layer mixed with HfSiO dielectric layer showed a reduction of 0.2V in the threshold voltage.

The last issue that we will discuss here involves the gate electrode used on the high-κ gate oxides. As discussed above, the poly-Si annealing processing causes inter-diffusion of Si. In order to circumvent this drawback, a metal electrode is used instead of a conventional poly-Si variety. However, when incorporating the new metal electrode the complications having to do with the channel mobility, and threshold voltage shift would have to be considered. Another challenge with metal gate is the fact that a poly-Si gate electrode can be used for both n- and p-MOS by simply adding different dopants. But the metal gate with a fixed work function is not as conducive in that there is not as much flexibility in the work function for n- or p-MOS when a metal gate is used.

Two approaches can be implemented for tackling the above problem. The first method is to use the so-called “midgap metals” such as TiN [103] with which the Fermi level would be at the midgap of the Si substrate, as shown in Fig. 17. The advantageous feature of these kinds of metal electrodes is the symmetrical V T value for both n-MOS and p-MOS, because the Fermi level being at the midgap would allow for the same energy difference between the metal Fermi level and the conduction and valence bands of Si. This provides the basis on which a simpler CMOS processing scheme can be crafted, because only one mask and one metal would be required for the gate electrode, and no ion implantation step would be required.

Energy diagrams of threshold voltages for n-MOS and p-MOS devices using (a) midgap metal gates and (b) dual metal gates [3]

Another method involves the use of the different metals for n- and p-MOS, as shown in Fig. 17. So far, many metal electrodes have been applied and studied. However, from the thermal stability point of view, the possible metal choices are limited. Most of the low work function metals are reactive and not stable under the conventional Si MOSFET processing, particularly high temperature annealing. Likely, most of the mid-bandgap metals and high work function metals are stable under these kinds of processing. Callegari et al. [104] used W as the metal gate and investigated the characteristics of the W/HfO2. They found that even with low interface-state densities (N it), low-temperature (<600 °C) processing resulted in very low electron mobilities. The oxygen diffusion is the key point for the mobility degradation. By preventing the oxygen diffusion and interface re-growth, the mobility degradation can be reduced.

Clearly, the high-κ dielectric materials and related methodologies are crucial for continuing the Si-based scaling engineering. A good deal of investigations dealing with different aspects of this problem has been carried out, particularly toward realizing the integration of high-κ dielectrics with conventional Si devices. However, there are still many obstacles that need to be conquered. In terms of the deposition aspects, the precursors and growth conditions for the high-κ films should be honed in and or optimized further. To prevent the crystallization of the dielectric films during subsequent high temperature processing, the thermal stability issue should be studied to increase the crystallization temperature of the high-κ films. The gate electrodes for the high-κ films and processing integration compatibility are also in need of further research and development.

6 New channel materials

Progress in Si-based MOSFET technology and scaling is not limited to the high-κ materials only in that the search is on for channel material for better transport properties as compared to bulk Si. An immediate approach is to use strained Si which allow occupation of only the low lying conduction bands with smaller in plane effective mass. Both compressive and tensile varieties depending on whether n- or p-channel MOSFET is being considered have been developed and already incorporated in high performance chips. The projections to longer term developments go beyond strained Si and include possible channel materials such as (In,Ga)As As for the n-channel device due to its relatively high electron mobility and velocity, and Ge for the p-channel device for its high hole mobility. Needless to say, there is a plethora of challenges that must be faced and overcome before the aforementioned channel materials and possibly others will be implemented. Below, we begin the discussion with strained Si channel and extend it to include GaAs and Ge channels with the associated gate oxide development.

6.1 Strained Si channel

CMOS-based chip speed as well and the density is of paramount importance to the semiconductor industry in particular and electronics industry in general. The conventional Si-based MOSFET is no longer able to fulfill the continued relentless demand for increased speed. The improvement of the channel mobility is a highly important issue for increasing the CMOS circuits speed. A preferred solution is to increase the effective MOSFET mobility while still using the conventional silicon material by utilizing strained silicon channels. The basic idea for the mobility enhancement is to increase the time between carrier scattering events through reducing the effective mass by introducing strained Si channels [105]. Mechanical strain introduced by the lattice mismatch between the Si channel and substrate breaks the crystal symmetry and removes the 2-fold and 6-fold degeneracy of the valence and conduction bands, respectively. This then leads to change of the band scattering rates and the carrier effective mass, which in turn enhances the in-plane mobility of the lower energy conduction electrons. As shown in Fig. 18, under a biaxial in-plane tensile strain (compression out of plane) the band structure of the 6-fold conduction band degeneracy of Si is lifted which results in a 2-fold Δ2 (out-of plane) and 4-fold Δ4 (in-plane) band splitting. The 4-fold degenerate conduction bands move upward in energy at a rate of 2.9 meV/kbar (in terms of stress) and the 2-fold degenerate conduction bands move downward in energy at a rate of 5.8 meV/kbar (in terms of stress). Under a biaxial in plane compressive strain (tensile out of plane) the direction of the shift in energy of these same bands is reversed, again as seen in Fig. 18.

In the biaxial in-plane tensile strain, the electrons populate the two low energy Δ2 bands that also have smaller in-plane electron mass. Biaxial compressive strain (tensile out of plane) also splits the heavy and light hole bands. When used in conjunction with a 2-dimensional hole gas inversion layer, the band splitting caused by quantum confinement is negated by the in-plane biaxial compressive strain. Further increases in the strain begin to split the bands in the opposite direction from the confinement-induced splitting. As a result, high in-plane biaxial compressive strain (tensile out of plane uniaxial strain) results in a considerable valence band splitting which leads to hole mobility enhancement. Essentially, strained silicon can yield higher mobilities by up to 70% for n-channel and up to 30% for p-channel devices.

As for introducing stress in the Si channel, several methods are utilized. One of the most heavily studied way is to epitaxially grow strained-silicon on a relaxed SiGe layer. The unacceptably high dislocation densities have prevented this method from being implemented in the industry. Ignoring this for the moment, the lattice mismatch between Si and SiGe substrate can cause the needed stress in Si. Shown in Fig. 19 are three methods of strain introduction. The common method, in terms of the number of research papers on the topic, is to grow the strained Si layer on a relaxed SiGe buffer layer which in turn is grown on a Si substrate. As mentioned the lattice mismatch between SiGe and Si causes the desired strain as shown in Fig. 19a. An alternate approach takes advantage of Si/SiGe layer growth on a SOI substrate [106], as shown in Fig. 19b. The strained Si short channel MOSFET fabricated on an SOI substrate shows 20–25% device enhancement.

Depending on one’s point of view, a more complicated method called “wafer-bonding” has been used to remove the SiGe layer from the Si substrate on which it is grown to obtain relaxed SiGe (Fig. 19c) [107]. To accomplish this, a series of steps are taken. First, a thin layer of Si is grown on the SiGe layer and an oxide layer formed on the Si layer. After planarizing the oxide surface with a chemical mechanical polishing step, hydrogen is implanted through the oxide and into the SiGe layer, and the wafer is bonded to a silicon wafer (“handle substrate”). Then by thermal annealing a cavity is formed in the SiGe buffer due to the hydrogen implantation. In the SiGe buffer layer the bonded stack splits at the interface created by these cavities, leaving the buried oxide layer, the strained Si layer, and a layer of relaxed SiGe on the new handle wafer. After a thermal annealing step to strengthen the bonding interface, the thin layer of SiGe on top of the transferred strained Si layer is selectively removed by a combination of polishing and chemical etching with a NH4OH-based solution. The processing steps are shown in Fig. 19d.

Besides using the epitaxially growth of SiGe to introduce the strain needed in Si channel, strain can also be attained during the fabrication processing which in general is the preferred method in industry as the SiGe approach leads to somewhat dislocated material. Mechanical stress can be transferred to the Si channel through the Si active area and poly gate if a permanent stressor liner is deposited on the device. Ito et al. [108] fabricated 0.13 μm strain Si CMOSFETs by inserting a nitride contact-etch-stop layer that was deposited by PECVD after the silicide formation. The other steps are the same as those with the conventional CMOS fabrication process. However, there is a drawback in that the internal stress in the nitride layer changes the transconductance and degrades the NMOSFET performance by up to 8% although the PMOSFET performance can be enhanced up to 7%.

The stress can also be introduced by a processing scheme named “stress memorization technique”. In this process, a tensile stressor capping nitride layer is deposited before the dopant activation annealing [109]. After an annealing step, the nitride layer is removed, and then a Co silicide film is deposited. The entire processing steps are shown in Fig. 20. During the annealing process, the stress can be transferred to the channel layer from the nitride layer and “memorized” by re-crystallization of the S/D and poly gate amorphized layers. Since the nitride film is disposable, a very thick capping layer can be used to increase the stress level without any process limitation.

Integration process of strain memorization technique (SMT). The processing can be expressed as five steps corresponding to the three diagrams in the figure: (a) After S/D implantation; (b) oxide and tensile nitride deposition; (c) S/D and poly dopant activation anneal; (d) nitride removal; (e) salicidation and subsequent processes. STI: Shallow Trench Isolation [110]

The last method to form the strain to be discussed here is to fill the source and drain regions with SiGe in p-MOS. The epitaxially grown SiGe will lead to laterally compressive strain in the Si channel because of its larger lattice constant than that of Si. NMOS is protected by a capping layer to prevent Si recess during SiGe epitaxial growth. This structure can form a large uniaxial compressive stress for the p-MOS channel and result in significant hole mobility enhancement [111].

Above, we discussed the approaches used to introduce strain in Si channels. There are, however, some specifics as the properties of strained Si n- and p-MOSFET that deserve further discussion. Since the strained Si n- and p-MOSFETs are used as part of scaling, both types of channel must be fabricated in the realm of the short channel MOSFET structures. Given the importance and extent of the reach of Si technology, a whole lot of investigations have been undertaken in regard to short channel MOSFETs and short channel effects. For n-MOSFET, the first problem is the extrinsic series resistances exacerbated by decreased Si layer thickness. Unless the extrinsic S/D resistance issue is addressed and those resistances are scaled, the gain afforded by strained channel can be negated and the ON current, I on, would be reduced. It is, therefore, important to note that for experimental processes where the gate length is aggressively reduced but other aspects of the transistor remain the same as they are expected of a larger technology node, R sd may constitute a much larger proportion of the total resistance, which could significantly offset any benefit of strained Si on I on for the short channel n-MOSFET. An additional reduction of I on enhancement can be expected if R sd is larger for strained Si compared to bulk Si controls, which may be the case if the S/D implant and anneal process cannot be optimized to compensate for the higher diffusivity and apparent lower electrical activation of As in Si1−x Ge x [112].

Another issue for the strained Si MOSFET is the conduction band offset. Under strain, the Si conduction band will bend and thus the threshold voltage will change if the same polysilicon electrode layer is used in the strained Si MOSFET. It has been reported that the threshold voltage for strained Si MOSFET is 150 meV lower than that for the bulk Si MOSFET case because of the conduction-band offset at the surface [113]. If an n + polysilicon is used as the gate electrode layer, a heavier channel doping is required to compensate the threshold voltage shift. Rim et al. [114] found that for threshold-matched strained Si (on 13% Ge) and bulk Si short-channel n-MOSFETs, the effective vertical field E eff for a given V GT was 0.26 MV/cm higher in the strained Si case. However, only 30% mobility enhancement can be obtained in this sort of device. It is found that the Coulomb-scattering introduced by the heavier doping at high electric fields degrades the mobility enhancement in the strain Si channel [115]. This means that in order to obtain the higher mobility enhancement, the strain Si MOSFET should operate at higher effective vertical fields.

However, if a metal gate electrode is used to replace the polysilicon gate electrode, it is not necessary to increase the channel doping to compensate for the band offset. The offset makes strained Si more compatible with a single metal gate work-function solution for bulk CMOS. Xiang et al. [116] used NiSi as the metal gate electrode material to fabricate the 35 nm strained Si MOSFET and found further enhancement in performance with good control over the short channel effects and no degradation in the gate oxide integrity, compared with the polysilicon MOSFET. For strained Si devices with metal gates, I dsat improvements are about 90% for long channel and 45% for 35 nm MOSFETs.

Another problem that is encountered is the n-type dopant diffusion in the SiGe layer. Usually, As and P have higher diffusivities in SiGe that in Si, which means that the n-type dopants will diffuse into the SiGe layer. This leads to a higher overlap capacitance which exacerbates the short channel effects. Wang et al. [117] found that enhanced diffusion of dopants along the misfit dislocations associated with SiGe/Si leads to increased off-state leakage in strained Si channel devices. They also noted that the process window narrows with increasing thermal budget since both strain relaxation and Ge diffusion are thermally activated. Choosing an optimal process window is, therefore, important for obtaining a robust and manufacturable substrate-strained Si technology.

The last issue we will touch upon for the n-MOSFET is the self-heating effect. Since the SiGe layer has a lower thermal conductivity than bulk Si, SOI-like self-heating in strained Si MOSFETs will reduce the current enhancement (Fig. 21) [118].