Abstract

A two-dimensional (2-D) technology computer-aided design (TCAD)-based simulation study of the back bias in the ultrathin silicon-on-insulator (SOI) tunnel field-effect transistor (TFET) is presented. The transfer characteristics of a conventional TFET called the back-bias TFET (BB-TFET) depend on the back bias and the oxide thickness below the TFET epitaxial layer. The back bias affects the electric field at the source/channel and drain/channel junctions, hence both the ON-state current (\(I_{\mathrm{ON}}\)) and the ambipolar current (\(I_{\mathrm{AMB}}\)) reduce with a negative back-bias voltage. This reduction in \(I_{\mathrm{ON}}\) is not desirable in a TFET, hence a modified TFET structure called the back-bias underdrain TFET (BBUD-TFET) is proposed. In the BBUD-TFET, the back bias is applied on a p-Si pocket placed under the drain region, which is isolated using an ultrathin oxide. The back bias in the proposed BBUD-TFET mainly affects the electric field at the drain/channel interface, having a negligible impact on the source/channel interface. The BBUD-TFET structure is analyzed with \({\mathrm{SiO}}_2\) or \({\mathrm{HfO}}_2\) as the gate oxide. In the BBUD-TFET with \({\mathrm{HfO}}_2\) as the gate oxide, the back bias completely suppresses the ambipolar current without reducing \(I_{\mathrm{ON}}\). Furthermore, the oxide thickness and back-bias voltage are optimized for the BBUD-TFET structure. In this study, 2-D TCAD simulations are carried out to investigate and analyze the performance of the BB-TFET and BBUD-TFET.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Tunneling field-effect transistors (TFETs) are gaining importance due to their suppressed subthreshold swing (SS). However, these devices also suffer from low ON-state current (\(I_{\mathrm{ON}}\)) and high leakage current due to ambipolar conduction, i.e., the conduction of current in the OFF-state (\(I_{\mathrm{OFF}}\)) [1,2,3]. This ambipolar effect is undesirable for the performance of inverter-based logical circuits [4]. On the other hand, the low \(I_{\mathrm{ON}}\) increases the charging and discharging time, hence decreasing the speed of circuits and making the TFET unsuitable to meet International Technology Roadmap for Semiconductors (ITRS) requirements [4, 5]. Therefore, increasing \(I_{\mathrm{ON}}\) while suppressing the ambipolar current (\(I_{\mathrm{AMB}}\)) are the main research challenges to make TFETs suitable for use in low-power circuit applications.

Several techniques have been reported in literature to suppress \(I_{\mathrm{AMB}}\) in TFETs [5,6,7,8,9,10,11,12,13,14]. Hraziia et al. [5] utilized a gate–drain underlap region and a low-\(\kappa\) spacer in the gate–drain region, and placed the contact at the top and bottom of the structure to reduce the ambipolar effect in double-gate (DG)-TFETs. The proposed structure delivered \(I_{\mathrm{AMB}}\)\(\sim 10^{-14} \,{\mathrm{A}}/\upmu {\mathrm{m}}\) with \(I_{\mathrm{ON}}\)\(\sim 10^{5} \,{\mathrm{A}}/\upmu {\mathrm{m}}\). Abdi and Kumar [6] proposed a gate-on-drain overlapping configuration in the DG-TFET to suppress \(I_{\mathrm{AMB}}\). The overlapped gate-on-drain configuration suppresses \(I_{\mathrm{AMB}}\) (\(\sim 10^{-15} \,{\mathrm{A}}/\upmu {\mathrm{m}}\)) with \(I_\mathrm{ON}/I_{\mathrm{OFF}}\) of \(\sim 10^{6}\). Raad et al. [7] reported a TFET structure with three gate materials in which the work function of the gate material on the source and drain sides was taken to be lower than the work function of the gate material in the middle. This device also employed a low-\(\kappa\) dielectric on the drain side and a high-\(\kappa\) dielectric on the source side. The reported TFET suppressed \(I_{\mathrm{AMB}}\) to \(\sim 10^{-16} \,{\mathrm{A}}/\upmu {\mathrm{m}}\) while improving \(I_{\mathrm{ON}}\) to \(\sim 10^{4} \, {\mathrm{A}}/\upmu {\mathrm{m}}\). Narang et al. [8] used a heterogeneous gate oxide with a gate–drain underlap configuration to minimize the \(I_{\mathrm{AMB}}\) (\(\sim 10^{-12} \, {\mathrm{A}}/\upmu {\mathrm{m}}\)) of the device. Similarly, gate material engineering has been used to reduce the \(I_{\mathrm{AMB}}\) of DG-TFETs by Nigam et al. [9]. They took a low-work-function gate material at the source and drain sides and a high-work-function gate material in the middle. This DG-TFET structure has been demonstrated to achieve a SS, \(I_{\mathrm{OFF}}\), and \(I_{\mathrm{ON}}\)/\(I_{\mathrm{OFF}}\) of 19 mV/dec, \(2.29\times 10^{-17} \, {\mathrm{A}}/\upmu {\mathrm{m}}\), and \(7.22\times 10^{11}\), respectively. Sharkar et al. [10] presented a drain engineering approach to lower the \(I_{\mathrm{AMB}}\) of the SOI TFET. Those authors established that the relative increase in thickness of the low-doping drain region over the high-doping drain region increased the tunneling width, leading to an appreciable reduction in \(I_{\mathrm{AMB}}\) (\(\sim 10^{-15} \, {\mathrm{A}}/\upmu {\mathrm{m}}\)). Singh and Kondekar [11] proposed an electrostatically doped ferroelectric Schottky barrier TFET (ED-FE-SB TFET) by analyzing the effect of negative capacitance. The proposed device showed SS, \(I_{\mathrm{AMB}}\), and \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) of 56 mV/dec, \(8.74\times 10^{-9} \, {\mathrm{A}}/\upmu {\mathrm{m}}\), and \(6.74\times 10^{7}\), respectively. Rahimian and Fathipour [12] demonstrated an asymmetric junctionless nanowire (AJN) TFET having an \(n^+\) pocket at the source. The AJN TFET provided SS, \(I_{\mathrm{AMB}}\), and \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) of 38 mV/dec, \(7.5\times 10^{-12} \, {\mathrm{A}}/\upmu {\mathrm{m}}\), and \(3.87\times 10^{9}\), respectively. Ashita et al. [13] reported an electron–hole bilayer (EHB) TFET with double dielectric pockets in the source and drain. The proposed structure achieved an SS, \(I_{\mathrm{OFF}}\), and \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) of 17.75 mV/dec, \(9.09\times 10^{-17} \, {\mathrm{A}}/\upmu {\mathrm{m}}\), and \(2.55\times 10^{9}\), respectively. Further, Bal et al. [14] proposed a dual-material gate (DMG) TFET and studied its energy band modulation profile. The DMG TFET provided SS, \(I_{\mathrm{OFF}}\), and \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) of 17 mV/dec, \(3\times 10^{-13} \,{\mathrm{A}}/\upmu {\mathrm{m}}\), and \(6.67\times 10^{9}\), respectively.

The effect of back biasing on the performance of TFETs has also been studied in literature [15,16,17,18]. Guo et al. [15] improved the \(I_{\mathrm{ON}}\)/\(I_{\mathrm{OFF}}\) ratio and SS of the SOI TFET through back biasing, including the effect of variation in the source and drain doping underneath the gate electrode. A similar study was reported on the germanium-on-insulator (GOI) TFET by Matheu et al. [16]. Sahay and Kumar [17] proposed the inclusion of a heterodielectric box (HDB) over a heavily doped grounded substrate at the channel/drain interface with \({\mathrm{SiO}}_2\) under the source/channel interface and a high-\(\kappa\) (\({\mathrm{HfO}}_2\)) dielectric under the drain region. Those authors reduced \(I_{\mathrm{AMB}}\) to \(\sim 10^{-16} \, {\mathrm{A}}/\upmu {\mathrm{m}}\) due to the increased tunneling width at the drain/channel interface and improved the \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio to \(\sim 10^{10}\). Further, Wang et al. [18] presented an ultrathin-body GeSn TFET with a back gate bias to improve the \(I_{\mathrm{ON}}\), SS, and \(I_{\mathrm{AMB}}\).

Note that the techniques applied to suppress \(I_{\mathrm{AMB}}\) in the cited articles also degrade the \(I_{\mathrm{ON}}\) of the TFET, resulting in a low \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio. Therefore, it is desirable to design a TFET structure that can provide a lower \(I_{\mathrm{AMB}}\) but higher \(I_{\mathrm{ON}}\) simultaneously. In this work, the conventional TFET with a back bias applied on the p-Si layer over the buried oxide (BOX) and under the device is called the BB-TFET. In the BB-TFET structure, \(I_{\mathrm{AMB}}\) is completely suppressed and the SS is improved. However, \(I_{\mathrm{ON}}\) is also reduced in the BB-TFET structure. To overcome this reduction in \(I_{\mathrm{ON}}\), the back-bias underdrain TFET (BBUD-TFET) is proposed, in which the back biasing is applied on the p-Si pocket under the drain region. The BBUD-TFET achieves complete elimination of \(I_{\mathrm{AMB}}\) as well as a significant improvement in SS and \(I_{\mathrm{ON}}\). The performance of the BB-TFET and BBUD-TFET is investigated using 2-D TCAD simulations in the ATLAS device simulator [19].

The calibration of the simulation setup using a prefabricated TFET [20]

2 The simulation setup

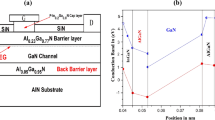

The BB-TFET and BBUD-TFET structures are implemented in the TCAD simulator by invoking suitable models. In this study, the Lombardi mobility (CVT) model is used to include the effect of the concentration- and field-dependent mobility. The Shockley–Read–Hall (SRH) model is chosen to incorporate the phenomenon of carrier recombination. The bandgap narrowing (BGN) model is selected to include the effect of the high concentration in the bandgap. Fermi–Dirac statistics is employed to incorporate certain properties of the highly doped region. Moreover, the nonlocal band-to-band tunneling model is used to simulate the tunneling effect in the devices. To calibrate the simulation setup, a prefabricated TFET [20] is implemented and simulated using the above-mentioned models. Figure 1 shows a comparison of the simulated and fabricated transfer characteristics of the published TFET structure, revealing a good match between the simulated and experimental results.

2.1 The device structures, results, and discussion

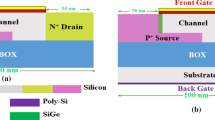

A cross-sectional view of the BB-TFET structure on SOI is shown in Fig. 2. The structure consists of an ultrathin \({\mathrm{SiO}}_2\) layer over the p-Si region placed on the BOX. The various device structural parameters used in this study are: gate oxide (GOX) thickness (\(T_{\mathrm{OX}}) = 1 {\mathrm { nm}}\), channel length \({(L)} = 50\, \hbox{nm}\), channel thickness (\(T_{\mathrm{si}}) = 10\, \hbox{nm}\), \(p^+\)-source region doping \(= 1\times 10^{20} \, {\mathrm{cm}}^{-3}\), n-channel doping \(= 1\times 10^{17} \, {\mathrm{cm}}^{-3}\), \(n^+\)-drain region doping \(= 5\times 10^{18} \, {\mathrm{cm}}^{-3}\), p-Si layer doping \(= 1\times 10^{15} \, {\mathrm{cm}}^{-3}\), and the work function of the gate material \(= 4.7\, \hbox{eV}\), while the dimension of the ultrathin \({\mathrm{SiO}}_2\) (\(T_{\mathrm{OB}}\)) is varied from 2 to 10 nm. A negative back-bias voltage (\(V_{\mathrm{BB}}\)) is applied to the p-Si layer from the drain to source uniformly. The application of \(V_{\mathrm{BB}}\) reduces the electric field at the drain/channel and source/channel interfaces. Note that the electric field at the drain/channel interface is responsible for the \(I_{\mathrm{AMB}}\) in the TFET structure. Therefore, the reduction in the electric field at this interface leads to suppression of \(I_{\mathrm{AMB}}\). The \(I_{\mathrm{ON}}\) of the device depends on the tunneling of carriers at the source/channel interface, hence a reduction in the electric field at this interface results in a degradation in \(I_{\mathrm{ON}}\).

The effect of \(V_{\mathrm{BB}}\) on the transfer characteristics of the BB-TFET is shown in Fig. 3. Note from this figure that the application of a negative \(V_{\mathrm{BB}}\) entirely suppresses the \(I_{\mathrm{AMB}}\) but also decreases the \(I_{\mathrm{ON}}\) of the device. This figure reveals that, when \(V_{\mathrm{BB}}\) is increased from −1 to −2 V, the \(I_{\mathrm{AMB}}\) in the device is completely suppressed but the \(I_{\mathrm{OFF}}\) increases. In the OFF-state condition (\(V_{\mathrm{GS}}= 0\, \hbox{V}\)), the current in the BB-TFET is obtained as \(1.49\times 10^{-11}\, \hbox{A}/\upmu \hbox {m}\), \(1.5\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\), and \(3.8\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\) at \(V_{\mathrm{BB}} = 0\, \hbox{V}\), \(V_{\mathrm{BB}} = -1\, \hbox{V}\), and \(V_{\mathrm{BB}} = -2\, \hbox{V}\), respectively. Further, changing \(V_{\mathrm{BB}}\) from −1 to −2 V significantly reduces the \(I_{\mathrm{ON}}\). In the ON-state condition (\(V_{\mathrm{GS}}= 1.2\, \hbox{V}\)), the \(I_{\mathrm{ON}}\) is found to be \(1.64\times 10^{-6}\, \hbox{A}/\upmu \hbox {m}\), \(8.8\times 10^{-7}\, \hbox{A}/\upmu \hbox {m}\), and \(3.76\times 10^{-8}\, \hbox{A}/\upmu \hbox {m}\) at \(V_{\mathrm{BB}} = 0\, \hbox{V}\), \(V_{\mathrm{BB}} = -1\, \hbox{V}\), and \(V_{\mathrm{BB}} = -2\, \hbox{V}\), respectively. For \(V_{\mathrm{BB}}= -1\, \hbox{V}\), the SS and threshold voltage (\(V_{\mathrm{t}}\)) are calculated as 17.5 mV/dec and 0.84 V, respectively.

The reduction in \(I_{\mathrm{AMB}}\) and \(I_{\mathrm{ON}}\) with \(V_{\mathrm{BB}}\) can be better explained based on the electric field distribution in the structure.

The \(I_{\mathrm{ON}}\) and \(I_{\mathrm{AMB}}\) of the TFET depend on the band-to-band tunneling (BTBT) at the source/channel and drain/channel junctions, respectively [21]. The BTBT rate (\(G_{\mathrm{BTBT}}\)) depends on the local electric field (\(\varepsilon\)) at the junction according to the equation [22]

where A is a constant related to the effective electron mass, B is the tunneling probability constant, and \(\sigma\) is the transition constant. The 2-D electric field distribution in the BB-TFET with and without back bias in the OFF-state is shown in Fig. 4. As depicted in Fig. 4b, in the OFF-state (\(V_{\mathrm{GS}} = 0\, \hbox{V}\)), the application of the back bias drastically reduces the electric field at the drain/channel interface compared with Fig. 4a. This reduction in the electric field at the drain/channel junction leads to complete suppression of \(I_{\mathrm{AMB}}\). Note that, although \(I_{\mathrm{AMB}}\) is suppressed with the back bias, \(I_{\mathrm{OFF}}\) increases as \(V_{\mathrm{BB}}\) is increased from 1 to −2 V due to the higher electric field in the drain region.

Furthermore, the effect of the back bias on the transfer characteristics of the BB-TFET can be explained based on the tunneling probability. The tunneling probability (\(T_{\mathrm{WKB}}\)) in a TFET is given by the Wentzel–Kramer–Brillouin (WKB) approximation, which is written as [2, 23]:

where \(\lambda\) and \(\varDelta \phi\) denote the tunneling width and the effective tunneling energy range, respectively (as shown in Fig. 5). The effective electron mass is \(m^*\), and the bandgap energy is \(E_{\mathrm{g}}\).

Figure 5 shows the energy band diagram of the BB-TFET at different \(V_{\mathrm{BB}}\) values along the cut line \(C_1\) in the OFF-state. This figure reveals a significant overlap between the conduction band (CB) and valance band (VB) at the drain/channel junction without a back bias (\(V_{\mathrm{BB}} = 0\, \hbox{V}\)). This increases the \(T_{\mathrm{WKB}}\) at the drain/channel interface, leading to a large \(I_{\mathrm{AMB}}\). On the other hand, with the application of the back bias, there is no overlap between the CB and VB at the drain/channel interface, hence the \(I_{\mathrm{AMB}}\) is completely eliminated.

In the ON-state (\(V_{\mathrm{GS}}=1.2\, \hbox{V}\)), the effect of the back bias on the electric field and energy band diagram at the source/channel interface is illustrated in Figs. 6 and 7. It is clear from Fig. 6a, b that the back bias also reduces the electric field significantly at the source/channel junction. This decrease in the electric field at the source/channel junction degrades the \(I_{\mathrm{ON}}\) of the BB-TFET. Meanwhile, it is evident from the energy band diagram (Fig. 7) that the \(\lambda\) remains almost unaffected by the back bias, while \(\varDelta \phi\) reduces with an increase in the negative \(V_{\mathrm{BB}}\). As observed from this figure, the reduction in \(\varDelta \phi\) is small at \(V_{\mathrm{BB}} = -1\, \hbox{V}\) as compared with at \(V_{\mathrm{BB}} = -2\, \hbox{V}\). Therefore, the \(I_{\mathrm{ON}}\) decreases by a small amount at \(V_{\mathrm{BB}} = -1\, \hbox{V}\) when compared with \(I_{\mathrm{ON}}\) without a back bias. On the other hand, the \(I_{\mathrm{ON}}\) decreases significantly at \(V_{\mathrm{BB}} =-2\, \hbox{V}\) due to the large reduction in \(\varDelta \phi\).

Although the back bias in the BB-TFET suppresses the ambipolar current completely at \(V_{\mathrm{BB}} = -1\, \hbox{V}\), it also degrades the \(I_{\mathrm{ON}}\). This is due to the fact that the negative back bias reduces the \(\varDelta \phi\) at the drain/channel and source/channel junctions. To overcome this effect of \(V_{\mathrm{BB}}\) on the \(I_{\mathrm{ON}}\) in the BB-TFET, the back bias can be applied under the drain region only, resulting in the new structure called the BBUD-TFET as proposed in Fig. 8. In this structure, a p-Si region is introduced below the drain, being separated from the \(n+\) drain by an oxide with thickness of \(T_{\mathrm{OB}}\). The \(V_{\mathrm{BB}}\) is applied to the p-Si region, which will mainly affect the drain/channel junction but with a negligible effect on the source/channel interface. The other structural parameters of the BBUD-TFET remain identical to those of the BB-TFET to enable comparison of their performance parameters.

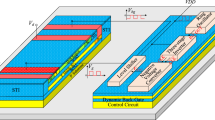

The fabrication steps for the BBUD-TFET are illustrated in Fig. 9. Initially, an SOI wafer with the required n-channel concentration is taken. Photoresist (PR) is applied over the whole wafer then patterned as shown in Fig. 9a. Reactive-ion etching (RIE) is used to remove the desired Sin-epitaxial layer as well as \({\mathrm{SiO}}_2\) (BOX) layer to obtain the trench structure shown in Fig. 9b. The RIE process offers a high selectivity ratio of 35:1 for both Si and \({\mathrm{SiO}}_2\). In the next step, p-type Si is grown in the trench, as shown in Fig. 9c. The growth of Si over \({\mathrm{SiO}}_2\) is achieved using a chemical vapor deposition (CVD) process in which the epitaxial layer is seeded through an opening in the \({\mathrm{SiO}}_2\) surface. This growth is carried out using a mixture of SiH2Cl2, \({\mathrm{H}}_2\), and HCl in the temperature range of 1050 to 1200 °C. To avoid problems related to the occurrence of silicon nucleation over \({\mathrm{SiO}}_2\), which would introduce defects into the overgrowing Si epitaxial layer, the growth process is carried out in a series of growth/etch steps [24]. As illustrated in Fig. 9d, a \({\mathrm{SiO}}_2\) layer with thickness \(T_{\mathrm{OB}}\) is deposited over the p-Si in the trench. In the next step, \(n^+-Si\) is grown over the \({\mathrm{SiO}}_2\) to form the drain region of the TFET, as shown in Fig. 9e. Finally, as shown in Fig. 9f, the proposed BBUD-TFET structure is obtained using the same fabrication steps as applied for a conventional TFET [25, 26]. Note that, in the BBUD-TFET, the p-Si region is aligned with the \(n^+\) drain region, which is advantageous from the fabrication point of view.

The transfer characteristics of the BBUD-TFET for different values of \(V_{\mathrm{BB}}\) are plotted in Fig. 10. Note from this figure that the OFF-state characteristics of the BBUD-TFET are identical to those of the BB-TFET. However, the effect of \(V_{\mathrm{BB}}\) on \(I_{\mathrm{ON}}\) is significantly reduced in the BBUD-TFET. Therefore, the \(I_{\mathrm{ON}}\) in the BBUD-TFET is higher than that in the BB-TFET. At \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{OFF}}\) of the BBUD-TFET are found to be \(1.71\times 10^{-6}\, \hbox{A}/\upmu \hbox {m}\) and \(1.54\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\), respectively. Moreover, at \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the SS and \(V_{\mathrm{t}}\) are obtained as 15.2 mV/dec and 0.79 V, respectively.

It is clear from Fig. 11a, b that the electric field contours at the drain/channel junction are almost identical for both structures. This fact is also illustrated by the energy band diagram shown in Fig. 12, in which there is negligible change in \(\lambda\) and \(\varDelta \phi\). Therefore, the OFF-state characteristics of the BB-TFET and BBUD-TFET are identical.

Figure 13a and b show the effect of \(V_{\mathrm{BB}}\) on the electric field distribution in the BB-TFET and BBUD-TFET in the ON-state condition, respectively. It is observed from this figure that the electric field at the source/channel junction in the BBUD-TFET is higher than that in the BB-TFET with a back bias. Furthermore, it is clear from the energy band diagram shown in Fig. 14 that the \(\lambda\) decreases while \(\varDelta \phi\) increases with the back bias in the BBUD-TFET in comparison with BB-TFET. Therefore, the effect of \(V_{\mathrm{BB}}\) at the source/channel junction of the BBUD-TFET is lesser compared with in the BB-TFET, hence the \(I_{\mathrm{ON}}\) in the BBUD-TFET is higher than that in the BB-TFET.

Moreover, the transfer characteristics of the BBUD-TFET can be further improved by using a high-\(\kappa\) dielectric material as the GOX [27, 28]. In this work, the BBUD-TFET structure is also simulated with the replacement of \({\mathrm{SiO}}_2\) by \({\mathrm{HfO}}_2\) as the GOX. Note that the thickness of the \({\mathrm{HfO}}_2\) is kept the same as that of the \({\mathrm{SiO}}_2\) (1 nm). Figure 15 shows the transfer characteristics of the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX. As shown in this figure, without a back bias (\(V_{\mathrm{BB}}=0\)), both the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{AMB}}\) of the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX are substantially higher than for the BBUD-TFET with \({\mathrm{SiO}}_2\) as the GOX (as shown in Fig. 10). However, the \(V_{\mathrm{BB}}\) in this device also results in complete elimination of the \(I_{\mathrm{AMB}}\) with only slight degradation in \(I_{\mathrm{ON}}\). It is observed that, for \(V_{\mathrm{BB}}=-1\, \hbox{V}\), the device exhibits the lowest \(I_{\mathrm{OFF}}\) without any compromise in \(I_{\mathrm{ON}}\). At \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{OFF}}\) of the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX are found to be \(3.13\times 10^{-4}\, \hbox{A}/\upmu \hbox {m}\) and \(1.77\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\), respectively. Moreover, at \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the SS and \(V_{\mathrm{t}}\) are obtained as 7.6 mV/dec and 0.42 V, respectively.

This improvement in the transfer characteristics of the BBUD-TFET can be explained with the help of the electric field distribution and energy band diagram with \({\mathrm{SiO}}_2\) and \({\mathrm{HfO}}_2\) as the GOX (Figs. 16, 17). As observed from Fig. 16, the electric field at both junctions near the gate is higher in the case of \({\mathrm{HfO}}_2\). On the other hand, the electric field is identical in both structures near the channel/\({\mathrm{SiO}}_2\) interface due to the back-bias effect. The cut line \(C_1\) is taken at the drain/channel interface near to the back surface. The energy bands overlap with each other in both cases, hence the \(I_{\mathrm{OFF}}\) is identical in both devices. The electric field contours and energy band diagram in the BBUD-TFET in the ON-state are shown in Figs. 18 and 19. From Fig. 18, it is observed that the electric field at the source/channel interface in the BBUD-TFET is higher with \({\mathrm{HfO}}_2\) as compared with \({\mathrm{SiO}}_2\). This enhanced electric field at the source/channel junction results in greater energy band bending, as illustrated in Fig. 19.

3 The optimization of the BBUD-TFET

Figure 20 shows the transfer characteristics of the BBUD-TEFT with \({\mathrm{HfO}}_2\) as the GOX for different values of \(T_{\mathrm{OB}}\) at \(V_{\mathrm{BB}}\) = −1 V. Note from this figure that \(I_{\mathrm{OFF}}\) decreases with an increase in \(T_{\mathrm{OB}}\) up to 6 nm. Thereafter, \(I_{\mathrm{AMB}}\) increases due to the reduced control of the \(V_{\mathrm{BB}}\) over the electric field at the drain/channel junction. On the other hand, the \(I_{\mathrm{ON}}\) increases continuously with an increase in \(T_{\mathrm{OB}}\) because, for higher values of \(T_{\mathrm{OB}}\), the effect of \(V_{\mathrm{BB}}\) on the source/channel junction is diminished. To determine the optimum value of \(T_{\mathrm{OB}}\) at \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio are plotted in Fig. 21, clearly revealing that the \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio is maximum for \(T_{\mathrm{OB}} = 6\) nm. Therefore, the optimum value of \(T_{\mathrm{OB}}\) is taken as 6 nm for \(V_{\mathrm{BB}} = -1\, \hbox{V}\). Similarly, the optimum value of \(T_{\mathrm{OB}}\) is found for other values of \(V_{\mathrm{BB}}\) and plotted in Fig. 22. The optimum value of \(T_{\mathrm{OB}}\) increases for higher values of \(V_{\mathrm{BB}}\).

The performance parameters of the BB-TFET and BBUD-TFET structures are compared with other TFETs reported in literature in Table 1. It is evident that the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX provides a \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio of 1.77\(\times 10^{13}\), which is significantly higher than that (\(\sim 10^{2}\)) of the reported dual material control gate (DMCG)-TFET structure [9]. Further, it is also observed that the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX provides the lowest value of SS when compared with the other reported structures.

4 Conclusions

The effect of the back-bias voltage on the transfer characteristics of the BB-TFET and BBUD-TFET is evaluated and investigated using 2-D TCAD simulations. The back-bias voltage in the BB-TFET reduces the electric field at both the source/channel and drain/channel junctions, which leads to a reduction in the tunneling probability and hence a substantial reduction in the \(I_{\mathrm{AMB}}\) and \(I_{\mathrm{ON}}\) of the device. At \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{OFF}}\) of the BB-TFET are found to be 2.24 \(\times 10^{-7}\, \hbox{A}/\upmu \hbox {m}\) and \(1.18\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\), respectively. To overcome the effect of \(V_{\mathrm{BB}}\) at the source/channel junction in the BB-TFET, the conventional TFET structure is modified to the BBUD-TFET, in which the \(V_{\mathrm{BB}}\) affects mainly the drain/channel junction. The BBUD-TFET is then studied with \({\mathrm{SiO}}_2\) or \({\mathrm{HfO}}_2\) as the GOX. The simulation results reveal that the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX offers complete elimination of \(I_{\mathrm{AMB}}\) but with no effect on \(I_{\mathrm{ON}}\). At \(V_{\mathrm{BB}} = -1\, \hbox{V}\), the \(I_{\mathrm{ON}}\) and \(I_{\mathrm{OFF}}\) of the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX are found to be \(3.13\times 10^{-4}\, \hbox{A}/\upmu \hbox {m}\) and \(1.77\times 10^{-17}\, \hbox{A}/\upmu \hbox {m}\), respectively. The \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio of the BBUD-TFET with \({\mathrm{HfO}}_2\) as the GOX is found to be \(1.77\times 10^{13}\), which is much higher than for other TFET structures. With a back bias in the ultrathin SOI TFET, the \(T_{\mathrm{OB}}\) and \(V_{\mathrm{BB}}\) are two important parameters to control the \(I_{\mathrm{AMB}}\) in the device. The improvement in the performance parameters of the BB-TFET and BBUD-TFET can be explained with the help of the electric field contours and energy band diagrams of the devices. The proposed device exhibits superior performance parameters as compared with other TFET structures reported in literature. Thus, the proposed BBUD-TFET is an attractive candidate for use in low-power switching applications.

References

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743 (2007). https://doi.org/10.1109/LED.2007.901273

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329 (2011). https://doi.org/10.1038/nature10679

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095 (2010). https://doi.org/10.1109/JPROC.2010.2070470

Krishnamohan, T., Kim, D., Raghunathan, S., Saraswat, K.: Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and \(<\)60 mV/dec subthreshold slope. In: 2008 IEEE International Electron Devices Meeting (IEEE, 2008), pp. 1–3 (2008). https://doi.org/10.1109/IEDM.2008.4796839

Hraziia, A., Vladimirescu, A., Amara, A., Anghel, C.: An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid State Electron. 70, 67 (2012). https://doi.org/10.1016/j.sse.2011.11.009

Abdi, D.B., Kumar, M.J.: Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187 (2014). https://doi.org/10.1109/JEDS.2014.2327626

Kondekar, P., Sharma, D., Nigam, K., Raad, B.: Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron. Lett. 52(9), 770 (2016). https://doi.org/10.1049/el.2015.4348

Narang, R., Saxena, M., Gupta, R.S., Gupta, M.: Assessment of ambipolar behavior of a tunnel FET and influence of structural modifications. J. Semicond. Technol. Sci. 12(4), 482 (2012). https://doi.org/10.5573/JSTS.2012.12.4.482

Nigam, K., Kondekar, P., Sharma, D.: Approach for ambipolar behaviour suppression in tunnel FET by workfunction engineering. Micro Nano Lett. 11(8), 460 (2016). https://doi.org/10.1049/mnl.2016.0178

Shaker, A., El Sabbagh, M., El-Banna, M.M.: Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs. IEEE Trans. Electron Devices (2017). https://doi.org/10.1109/TED.2017.2724560

Singh, S., Kondekar, P.N.: A novel electrostatically doped ferroelectric Schottky barrier tunnel FET: process resilient design. J. Comput. Electron. 16(3), 685 (2017). https://doi.org/10.1007/s10825-017-0987-6

Rahimian, M., Fathipour, M.: Asymmetric junctionless nanowire TFET with built-in n+ source pocket emphasizing on energy band modification. J. Comput. Electron. 15(4), 1297 (2016). https://doi.org/10.1007/s10825-016-0895-1

Loan, S.A., Alharbi, A.G., Rafat, M.: Ambipolar leakage suppression in electron-hole bilayer TFET: investigation and analysis. J. Comput. Electron. 17(3), 977 (2018). https://doi.org/10.1007/s10825-018-1184-y

Bal, P., Ghosh, B., Mondal, P., Akram, M.W., Tripathi, B.M.M.: Dual material gate junctionless tunnel field effect transistor. J. Comput. Electron. 13(1), 230 (2014). https://doi.org/10.1007/s10825-013-0505-4

Guo, A., Matheu, P., Liu, T.J.K.: SOI TFET ION/IOFF enhancement via back biasing. IEEE Trans. Electron Devices 58(10), 3283 (2011). https://doi.org/10.1109/TED.2011.2161480

Matheu, P., Ho, B., Jacobson, Z.A., Liu, T.K.: Planar GeOI TFET performance improvement with back biasing. IEEE Trans. Electron Devices 59(6), 1629 (2012). https://doi.org/10.1109/TED.2012.2191410

Sahay, S., Kumar, M.J.: Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11), 3882 (2015). https://doi.org/10.1109/TED.2015.2478955

Wang, H., Han, G., Liu, Y., Zhang, J., Hao, Y., Jiang, X.: Theoretical investigation of backgate-biasing effects on ultrathin-body GeSn based tunneling FET. In: 2017 IEEE SOI-3D-Subthreshold Microelectronics Unified Conference, S3S 2017, pp. 1–3 (2018). https://doi.org/10.1109/S3S.2017.8309214

Silvaco Inc., Atlas User’s Manual. Silvaco Inc. (2016)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-\(\kappa\) gate dielectric. IEEE Trans. Electron Devices 54(7), 1725 (2007). https://doi.org/10.1109/TED.2007.899389

Shih, C.H., Chien, N.D.: Bandgap-dependent onset behavior of output characteristics in line-tunneling field-effect transistors. J. Comput. Electron. 16(3), 696 (2017). https://doi.org/10.1007/s10825-017-1020-9

Adell, P.C., Barnaby, H.J., Member, S., Schrimpf, R.D.: Band-to-band tunneling (BBT) induced leakage current enhancement in irradiated fully depleted SOl devices. IEEE Trans. Nucl. Sci. 54(6), 2174 (2007)

Joshi, T., Singh, Y., Singh, B.: Dual-channel trench-gate tunnel FET for improved ON-current and subthreshold swing. Electron. Lett. 55(21), 1152 (2019). https://doi.org/10.1049/el.2019.2219

Jastrzebski, L., Corboy, J.F., McGinn, J.T., Pagliaro, R.: Growth process of silicon over SiO2 by CVD: epitaxial lateral overgrowth technique. J. Electrochem. Soc. 130(7), 1571 (1983). https://doi.org/10.1149/1.2120037

Devi, W.V., Bhowmick, B.: Optimisation of pocket doped junctionless TFET and its application in digital inverter. Micro Nano Lett. 14(1), 69 (2018). https://doi.org/10.1049/mnl.2018.5086

Strangio, S., Palestri, P., Esseni, D., Selmi, L., Crupi, F., Richter, S., Zhao, Q.T., Mantl, S.: Impact of TFET unidirectionality and ambipolarity on the performance of 6T SRAM cells. IEEE J. Electron Devices Soc. 3(3), 223 (2015). https://doi.org/10.1109/JEDS.2015.2392793

Atan, N.B., Ahmad, I.B., Majlis, B.B.Y.: Effects of high-K dielectrics with metal gate for electrical characteristics of 18 nm NMOS device. In: 2014 IEEE international conference on semiconductor electronics (ICSE2014), pp. 56–59 (2014). https://doi.org/10.1109/SMELEC.2014.6920794

Kumar, S., Goel, E., Singh, K., Singh, B., Kumar, M., Jit, S.: A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/high-k stacked gate-oxide structure. IEEE Trans. Electron Devices 63(8), 3291 (2016). https://doi.org/10.1109/TED.2016.2572610

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Joshi, T., Singh, B. & Singh, Y. Controlling the ambipolar current in ultrathin SOI tunnel FETs using the back-bias effect. J Comput Electron 19, 658–667 (2020). https://doi.org/10.1007/s10825-020-01484-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01484-8