Abstract

The challenges which the CMOS technology is facing toward the end of the technology roadmap calls for an investigation of various logical and technological solutions to CMOS at the nano scale. Two such paradigms which are considered in this paper are the reversible logic and the quantum-dot cellular automata (QCA) nanotechnology. Firstly, a new 3 × 3 reversible and universal gate, RG-QCA, is proposed and implemented in QCA technology using conventional 3-input majority voter based logic. Further the gate is optimized by using explicit interaction of cells and this optimized gate is then used to design an optimized modular full adder in QCA. Another configuration of RG-QCA gate, CRG-QCA, is then proposed which is a 4 × 4 gate and includes the fault tolerant characteristics and parity preserving nature. The proposed CRG-QCA gate is then tested to design a fault tolerant full adder circuit. Extensive comparisons of gate and adder circuits are drawn with the existing literature and it is envisaged that our proposed designs perform better and are cost efficient in QCA technology.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The boom that the electronics industry has seen in the last few decades is due to the evident success of the CMOS technology and the miniaturization that has been possible due to the scaling of the basic MOS structure. This paradigm of scaling has helped in maintaining the famous Moore’s law for the industry [1] according to which the number of components on a single chip doubles after approximately every two years. The growth suggests an exponential nature which is hard to maintain since no exponential can continue forever [2]. The ITRS (International Technology and Roadmap for Semiconductors) has pointed out the asperities which the CMOS is facing in surviving through the nano regime and it now seems that the CMOS technology is approaching the end of the roadmap.

In the nano scale the classical laws are no longer applicable for the device and the various quantum mechanical effects start dominating the device physics [3]. Though the present generation CMOS technology is 22 nm [4] many aftereffects can and will arise due to the reduction in the feature size in future. Few such consequences are in terms of leakage currents, power dissipation, oxide thickness, crosstalk and electron-migration. All these effects and consequences call for the development of alternate paradigms for the CMOS in nano regime [5,6,7,8]. Reversible logic and QCA nanotechnology form two such promising alternatives. The following sub-sections present a brief introduction of reversible circuits and QCA technology.

1.1 Reversible Logic

According to Landauer [9], the processing of information in digital circuits leads to the generation of heat due to erasing of bits during the process. This is because of the entropy changes accompanied with the destruction of information. He suggested that for every bit of information that is erased KTln2 joules of energy is dissipated. A few decades back this quantity was negligible since the power dissipation of the circuits was high but as the industry moves toward the ultra-low power architectures this quantity is becoming a matter of concern for VLSI circuits [10]. For targeting this heat generation, reversible logic is the proposed solution. According to this logic if the erasing of the bits is avoided in digital circuits the KTln2 joules of energy loss can be avoided [11,12,13,14,15]. A device is said to be logically reversible if there is a one-to-one mapping between the inputs and outputs and the number of inputs and outputs are equal. Besides this logical reversibility the physical reversibility is also important. This means that the technology that can be used for the implementation of these reversible circuits should be a system which is quantum mechanically reversible. Since CMOS doesn’t satisfy this, new technology alternatives are needed for the implementation of the reversible logic design. One of the technologies which stands as an alternative to the CMOS technology in nano regime and also design the reversible circuits is QCA.

1.2 QCA Nanotechnology

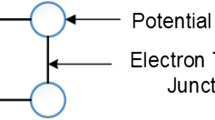

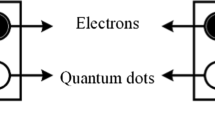

One of the most promising technology as seen by the researchers is the nanotechnology based Quantum Cellular Automata [16,17,18,19]. This technology incorporates a shift from the conventional transistorized designs to designing using nano structures like quantum dots or metal islands. This archetype works on the principles of quantum physics and uses the effects that were a threat to CMOS to its advantage. It was first proposed in 1993 by Craig S. Lent, P. Douglas Tougaw, Wolfgang Porod and Gary H. Bernsteain, at the University of Notre Dame. Quantum-dot Cellular Automata (QCA) is a newly developed paradigm for digital design and offers a breakthrough required for the fulfillment of certain lacking aspects of CMOS technology in the nano regime. Since the technology is new and in the premature phase a lot of scope lies ahead of researchers to take the designing using QCA to a commercial level. The basic component in the QCA circuits consists of a QCA cell as shown in Fig. 1.

The basic cell consists of four quantum dots or metal islands in which two electrons are allowed to localize. The dots are separated by tunnel junctions through which the electrons can move from one site to another. The basic mechanism of working of the cell is the coulombic repulsion between the cells and the quantum mechanical tunneling. Due to coulombic forces the electrons are allowed to only occupy the antipodal sites. This results in two polarization states called the binary zero and the binary one as shown in Fig. 2.

The cell to cell interactions are responsible for the transmission of information between the cells and hence no currents are involved in this technology. The polarization of one cell impacts the polarization of the other cell and so on. The basic building blocks in QCA are the binary wire, the inverter and the majority voter [34, 35]. The basic cell in QCA technology performs both transmission and processing. Various circuits in the designing require crossing of wires just like in CMOS circuits. This is implemented in QCA using QCA wire crossing. There are two types of wire crossings in QCA viz. the multilayer crossover and the coplanar crossover [20, 21].

For the proper functioning of the QCA circuits, they are provided with the clock signal which controls the information flow and also provides the true power gain in the circuits. The clock is provided in four zones with each zone consisting of four phases. The four phases are the switch, hold, release and relax. The clock signal is responsible for raising and lowering the barrier between the sites of electron localization. During the switch phase the barriers are lowered and the electrons are influenced by the neighboring cell polarizations. The switch phase is followed by the hold phase in which the cell is latched and retains its polarization state. During the release and relax phases the cell again loses its polarization and attains a null state. The clock phases need to follow each other in the above sequence for proper information flow via pipelining. The entire clocking process and its different phases are shown in Fig. 3.

The different clock zones in QCA are represented by different colors e.g. clock zone 0 is represented by green, clock zone 1 by magenta, clock zone 2 by blue and clock zone 3 by white in QCA Designer 2.0.3 simulator [22,23,24,25,26]. For the designing of the circuits in QCA, various parameters of designing need to be taken into consideration. These include the cell count, cell area, total area, latency and complexity of the designs.

The rest of the paper has been organized as follows. The proposed 3 × 3 reversible gate (RG-QCA) and its two implementations using majority voter approach and explicit interaction of cells is presented in Section 2 followed by validation of proposed reversible gate as a universal structure and its hardware complexity in Sections 3 and 4 respectively. The full adder design using proposed RG-QCA gate and its QCA implementation is presented in Section 5. The CRG-QCA gate, which is the optimized RG-QCA gate with additional fault tolerance characteristics, is presented in Section 6 followed by the design and QCA implementation of optimal fault tolerant full adder circuit. Finally, the performance comparison of proposed designs with other state-of-the-art designs from the literature is presented in Section 7 followed by the conclusion.

2 Proposed Reversible RG-QCA Gate

In this work, a new 3 × 3 reversible logic gate called the RG-QCA (Reversible Gate– Quantum-dot Cellular Automata) is proposed. The equations at the output of the reversible gate are designed in order to be most suitable for digital circuit implementation. The proposed RG-QCA gate is a 3 input and 3 output gate having its input vector (IV) and output vector (OV) as:

The block diagram of the proposed gate is shown in Fig. 4 and the truth table verifying the gate as reversible is shown in Table 1.

From the above truth table the reversibility of the proposed gate can be verified. As is explicit from the table, there is a one-to-one mapping between the inputs and outputs, which means that for a particular input combination, a unique output combination is present. This reversibility is achieved by designing the equations for the gate appropriately. The encoding as seen from the truth table is different on input and output side but all the combinations are present on both sides.

2.1 RG-QCA Using Conventional Majority Gate Approach

The simplest implementation of RG-QCA gate in QCA can be achieved using the conventional majority voter approach. This design has a large cell count and hence the area and latency of the circuit are also on the higher side. The total cell count of this design is 427 cells which is quite a large number for any QCA design. The QCA implementation of RG-QCA and its simulation waveform are shown in Fig. 5.

The majority equations for the outputs of the gate can be written as in (3)–(5) and the block diagram representation of the majority equations is given in Appendix A.

2.2 RG-QCA Using Explicit Interaction of Cells

For obtaining the most efficient design of the RG-QCA, the gate is redesigned using the best approaches available in literature. Mostly the approaches of explicit interaction of cells has been used in the new design [33]. The final optimized design obtained is highly efficient as compared to the majority logic designs. The cell count of 143 cells including one multilayer crossover has been used in the realization of the RG-QCA. The proposed RG-QCA is shown in Fig. 6.

The performance parameters of the RG-QCA using the conventional majority voter approach and the explicit interaction of cells are discussed in Section 7, Table 9. The percentage improvement that is obtained using the explicit interaction of cells is also shown.

3 RG-QCA as a Universal Structure

For a gate to be efficient the functionality of the gate is the prime parameter. This refers to the maximum number of basic Boolean operations that the gate can perform. A gate is said to be universal if it can implement all the seven basic Boolean functions. The RG-QCA can act as a universal gate by manipulating the various inputs of the gate. The inputs required for each function implementation are given in Table 2.

4 Hardware Complexity of RG-QGA Gate

In the case of the reversible circuits, one important parameter to measure the complexity of the implemented hardware is defined by the number of Exclusive-OR functions and the number of AND and NOT operations that are required to realize the outputs of the gate. The logical calculation for Ex-OR operation is calculated as α, for the AND operation the logical calculation is given by β and for the NOT operation the calculation is defined by the γ. From the equations of RG-QCA we can observe that the equations can be modified to include only these three operations without any change or threat to the reversibility of the gate. The equations for RG-QCA can thus be rewritten as,

From the above equations we see that there is a slight modification in the outputs Q and R, however these variations do not incorporate any changes in the truth table of the RG-QCA and thus can be used interchangeably with the previous RG-QCA output equations. Now the overall hardware complexity can be calculated by counting the number of Ex-OR, AND and NOT operations in the final equations. This results in the following equation for the hardware complexity of RG-QCA. Total Logical Calculation is given as:

where α, β and γ are the logical calculations for Ex-OR, AND and NOT respectively.

The proposed RG-QCA gate can also be used to implement the 13 standard logic functions. Table 3 shows the gate count and reversible parameters like the garbage output and constant input for the implementation of these functions.

5 Full Adder Design Using RG-QCA

From the extensive literature survey that we have done on reversible circuits and QCA we have realized the need for optimized designs of the adder circuits in QCA nano-technology. Adders form the core component of almost all the digital circuits which include the DSP processors, filters, microprocessors etc. The overall performance of the system is highly dependent on the type, speed and performance of the adder circuits incorporated in it. So the current research also focuses on the arithmetic units (like addition) in the reversible logic [27,28,29,30,31,32].

The adder designs in existing literature majorly focus on designs using modified adder equations and not on design using gate which can have additional functionalities in other digital components and architectures. In this paper, a new architecture for the design of full adder using the proposed RG-QCA which is based on explicit interaction of cells [33] has been proposed.

The various parameters of reversible logic which include the garbage output, constant input and quantum cost along with the various parameters in QCA that are the cell count, cell area, total area, latency have been taken into consideration in the design. The design of the new full adder requires two RG-QCA gates for implementation and results in the production of three garbage outputs and needs one constant input. The block diagram representation of the adder is shown in Fig. 7 along with the truth table of the adder in Table 4 to verify the results at the output.

The implemented design and simulation results in QCA Designer are shown in Fig. 8. The explicit interaction of cells not only leads to efficient designing but also improved QCA parameter considerations [34, 35]. The performance parameters of the designs of full adder circuit using the proposed RG-QCA are shown in Table 5. The design of the adder in QCA uses the most efficient design techniques. It is observed that the adder has been designed using a cell count of only 375 cells resulting in an area of 0.1215 μm2 and a total area of 0.37 μm2.

6 Fault Tolerant Designs Using RG-QCA

One of the most important characteristics of the efficient gate design in both reversible logic as well as the QCA technology is extending the design of the gate to include the fault tolerant characteristics. For the proposed RG-QCA gate, the fault tolerant feature is added by increasing one input and output of the gate and designing the equation accordingly. This means that for fault tolerance the 3 × 3 RG-QCA is converted to 4 × 4 CRG-QCA i.e. Conservative Reversible Gate, shown in Fig. 9. Table 6 shows the parity preserving character of the CRG-QCA. The CRG-QCA design in QCA technology, shown in Fig. 10, increases the cell count by only 14 cells which is highly efficient (Table 7).

6.1 Fault Tolerant Full Adder Circuit Design

The utility of the parity preserving gates is the most important in the digital circuits where operations like addition are perfomed. The conservative nature of the gates is important for error detection in the circuits. Designing the gates with such characteristics is of utmost imporatnce in digital designs. Here the CRG-QCA is extended to show application in the design of the full adder circuit. The design of the fault tolerant adder circuit and simulation results in QCA Designer 2.0.3 are shown in Fig. 11 and the performance parameters in Table 8.

7 Discussions

A number of comparisons have been drawn to prove the efficiency of the proposed designs. Table 9 shows the percentage improvement of the optimized RG-QCA design compared to conventional majority voter based design.

Tables 10 draws the comparisons between the existing 3 × 3 reversible gates and proposed RG-QCA gate and it is observed that the RG-QCA gate has the least cell count and hence cell area along with highest area utilization.

The performance comparison of the full adder circuits designed using proposed RG-QCA and CRG-QCA gates with existing state-of-the-art designs is given in Table 11. It is seen that the proposed RG-QCA based optimized full adder has least cell count and highest area usage. Although, the area usage using CRG-QCA gate is relatively low, it is fault tolerant in nature and a 4 × 4 gate and still achieves lower cell count comparable to the other 3 × 3 gate based adder designs. Table 12 shows the efficiency of the proposed CRG-QCA with existing parity preserving gates in QCA. In addition to this, comparison of number of gates required to implement the 13 standard logic functions using RG-QCA gate and other reversible gates has been presented in Table 13 and it is observed that the proposed gate requires least number of gates to implement the functions. Finally, a comparative cost analysis, based on the cost function proposed in [29, 37], is utilized to calculate the overall cost which is a function of number of QCA gates (NG), delay/latency (T) and number of crossovers (C) and are expressed as:

where N M G , N i n v , N R G and N c l k are the number of majority voter gates, number of inverters, number of reversible gates used in the design and number of clocks to get output respectively. Also, l denotes the number of number of layers in the design and is usually 1 for single layer design and 3 for multilayer design. In the proposed adder design, l is equal to 3. Since N M G and C have greater effect on complexity, power and fabrication difficulty, therefore cost has a quadratic relationship with N M G and C and thus n = m = 2 [29, 37]. It is observed from Table 14 that the overall cost is significantly reduced for the proposed full adder design using RG-QCA gate. The graphical area comparisons are also shown in Figs. 12 and 13. Hence, the proposed designs can be used as they show improved behavior in terms of size and complexity.

8 Conclusion

In this paper the alternatives to overcome the limitations that the CMOS technology is facing in the nano regime are discussed. The focus is on two upcoming paradigms namely, the reversible logic and the QCA nanotechnology. The basic theory and preliminaries related to both these paradigms are initially discussed followed by a detailed literature review on both reversible and irreversible circuit designs in QCA technology. The adder circuits which form the main component of maximum digital circuits are chosen as the component of interest here since the need for their efficient designs is of utmost importance. A new Reversible gate RG-QCA which has universal functionality, simplified equations and optimal QCA implementation is first proposed followed by the design of a full adder circuit using the optimal RG-QCA gate. This work also includes the development of fault tolerant designs. All the designs in this paper are based on explicit interaction of cells rather than the conventional majority voter approach. Using this approach a very high percentage improvement has been reported in all our designs. Extensive comparisons of proposed gate, full adder and the fault tolerant designs are drawn with the available designs in the literature. It is envisaged that the proposed designs outperform the existing ones in terms of almost all the QCA parametrs such as cell count, cell area, total area, latency and complexity.

References

Moore, G.E.: Cramming more components onto integrated circuits. Proc. IEEE 86, 82–85 (1998)

Moore, G.E.: No exponential is forever: but “Forever” can be delayed![semiconductor industry]. In: Solid-State Circuits Conference, 2003. Digest of Technical Papers. ISSCC, pp. 20–23. 2003 IEEE International (2003)

Dennard, R., Gaensslen, F., Kuhn, L., Yu, H.: Design of micron MOS switching devices? IEDM Dig. Techn. Pap., p. 344 (1972)

Iwai, H.: Roadmap for 22nm and beyond. Microelect. Eng. 86, 1520–1528 (2009)

Endo, M., Strano, M.S., Ajayan, P.M.: Potential applications of carbon nanotubes. In: Carbon Nanotubes, Edition, pp. 13–62. Springer, Berlin (2007)

Gautier, J.: Beyond CMOS: quantum devices. Microelect. Eng. 39, 263–272 (1997)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4, 49 (1993)

Sugahara, S.: Perspective on field-effect spin-transistors. Phys. Status Solidi (c) 3, 4405–4413 (2006)

Landauer, R.: Irreversibility and heat generation in the computing process. IBM J. Res. Dev. 5, 183–191 (1961)

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17, 525–532 (1973)

Feynman, R.P.: Quantum mechanical computers. Found. Phys. 16, 507–531 (1986)

Fredkin, E., Toffoli, T.: Conservative logic. Int. J. Theor. Phys. 21, 219–253 (1982)

Parhami, B.: Fault-tolerant reversible circuits. In: Fortieth Asilomar Conference on Signals, Systems and Computers, 2006. ACSSC’06, pp. 1726–1729 (2006)

Peres, A.: Reversible logic and quantum computers. Phys. Rev. A 32, 3266 (1985)

Toffoli, T.: Reversible computing. In: Automata, Languages and Programming, pp. 632–644 (1980)

Lent, C.S., Tougaw, P.D., Porod, W.: Bistable saturation in coupled quantum dots for quantum cellular automata. Appl. Phys. Lett. 62, 714–716 (1993)

Porod, W.: Quantum-dot devices and quantum-dot cellular automata. J. Frankl. Inst. 334, 1147–1175 (1997)

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75, 1818–1825 (1994)

Walus, K., Jullien, G.A.: Design tools for an emerging SoC technology: quantum-dot cellular automata. Proc. IEEE 94, 1225–1244 (2006)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14, 497–504 (2015)

Devadoss, R., Paul, K., Balakrishnan, M.: Coplanar QCA crossovers. Elect. Lett. 45, 1234–1235 (2009)

Hennessy, K., Lent, C.S.: Clocking of molecular quantum-dot cellular automata. J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct.–Process. Meas. Phenom. 19, 1752–1755 (2001)

Lent, C.S., Isaksen, B.: Clocked molecular quantum-dot cellular automata. IEEE Trans. Elect. Dev. 50, 1890–1896 (2003)

Liu, M., Lent, C.S.: Bennett and Landauer clocking in quantum-dot cellular automata. In: 10th International Workshop on Computational Electronics, pp. 120–121 (2004)

Orlov, A.O., Amlani, I., Kummamuru, R.K., Ramasubramaniam, R., Toth, G., Lent, C.S., et al.: Experimental demonstration of clocked single-electron switching in quantum-dot cellular automata. Appl. Phys. Lett. 77, 295–297 (2000)

Orlov, A.O., Kummamuru, R., Ramasubramaniam, R., Lent, C.S., Bemstein, G., Snider, G.L.: Clocked quantum-dot cellular automata devices: experimental studies. In: Proceedings of the 2001 1st IEEE Conference on Nanotechnology, 2001. IEEE-NANO 2001, pp. 425–430 (2001)

Ma, X., Huang, J., Metra, C., Lombardi, F.: Testing reversible 1D arrays for molecular QCA. In: 21st IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 2006. DFT’06, pp. 71–79 (2006)

Misra, N.K., Wairya, S., Sen, B.: Design of conservative, reversible sequential logic for cost efficient emerging nano circuits with enhanced testability. Ain Shams Eng. J. (2017)

Roohi, A., Zand, R., Angizi, S., Demara, R.F.: A parity-preserving reversible QCA gate with self-checking cascadable resiliency. In: IEEE Transactions on Emerging Topics in Computing (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: Efficient design of reversible alu in quantum-dot cellular automata. Optik-Intern. J. Light Elect. Opt. 127, 6172–6182 (2016)

Sen, B., Dutta, M., Goswami, M., Sikdar, B.K.: Modular Design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelect. J. 45, 1522–1532 (2014)

Thapliyal, H., Ranganathan, N., Kotiyal, S.: Design of testable reversible sequential circuits. IEEE Trans. Very Large Scale Integ. (VLSI) Syst. 21, 1201–1209 (2013)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Bilal, B., Ahmed, S., Kakkar, V.: QCA based efficient toffoli gate design and implementation for nanotechnology applications. Int. J. Eng. Technol. 9(3S), 84–92 (2017)

Bilal, B., Ahmed, S., Kakkar, V.: Optimal realization of universality of peres gate using explicit interaction of cells in quantum dot cellular automata nanotechnology. Int. J. Intell. Syst. Appl. 9(6), 75–84 (2017)

Thapliyal, H., Ranganathan, N.: Conservative QCA Gate (CQCA) for designing concurrently testable molecular QCA circuits. In: 22nd IEEE International Conference on VLSI Design, 2009, pp. 511–516 (2006)

Liu, W., Lu, L., O’Neill, M., Swartzlander, E.E. Jr.: A first step towards cost functions for quantum cellular automata designs. IEEE Trans. Nanotechnol. 13(3), 476–487 (2014)

Author information

Authors and Affiliations

Corresponding author

Appendix A: Majority Gate Representations

Rights and permissions

About this article

Cite this article

Bilal, B., Ahmed, S. & Kakkar, V. Modular Adder Designs Using Optimal Reversible and Fault Tolerant Gates in Field-Coupled QCA Nanocomputing. Int J Theor Phys 57, 1356–1375 (2018). https://doi.org/10.1007/s10773-018-3664-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-018-3664-z