Abstract

A novel technique for designing analog CMOS integrated filters is proposed. The technique uses digitally controlled current amplifiers (DCCAs) to provide precise frequency and/or gain characteristics that can be digitally tuned over a wide range. This paper provides an overview of the possibilities of using the DCCA as the core element in programmable filters. In mixed analog/digital systems, the digital tuning feature of the proposed approach allows direct interfacing with the digital signal processing (DSP) part. Basic building blocks such as digitally programmable amplifiers, integrators, and simulated active inductors are given. Systematic designs of second-order filters are presented. Fully differential architectures of the proposed circuits are developed. Experimental results obtained from 0.5 μm standard CMOS chips are provided.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Active-RC filters based on the operational amplifier (op-amp) exhibit high linearity. However, the constant gain-bandwidth product of the op-amp limits their frequency range and the lack of programmability restricts them to discrete applications. Tuning properties are essential for analog integrated circuit filtering techniques to compensate for process, component and temperature variations as integrated RC time constants can vary by as much as 50% [1]. Transconductance (gm) circuits are programmable and can operate at high frequencies. However, their linearity and tuning range are poor particularly at low supply levels [2]. The MOSFET-C approach provides wide tuning range [3] but it suffers from poor linearity and limited bandwidth. In addition, linearization techniques of MOSFET-C and gm-C circuits assume the classical MOS transfer characteristics in saturation or triode region. In submicron technologies, the second order effects such as short-channel and mobility degradation become significantly important, further degrading the linearity of these circuits. Switched capacitor (SC) filters exhibit high linearity and accurate frequency response; however, their frequency operation range is limited since they need to operate at sampling frequencies much greater than the signal bandwidths.

On the other hand, the current-mode approach of designing analog integrated circuits shows promising characteristics. This stems from its wide frequency operating range, high slew rate and simple circuitry [4, 5]. Recently, design of current and voltage-mode filters based on current followers and/or voltage buffers (VBs) such as [6–10] has been of growing interest due to their inherent large bandwidth, high linearity, and low power consumption. However, there are two major limitations associated with this approach, which hinder its use in analog integrated circuits. The first is the absence of the programmability feature and the second is the lack of providing fully differential structures with accurate common mode signal level control. In this work, programmability is introduced through varying the gain of the current amplifier and the extension to fully differential architectures is developed. Thus, the proposed technique is expected to become a fundamental analog filtering approach in future. This paves the way for the proposed circuits to be used in high-performance analog and mixed-signal ICs where fully differential signal paths are incorporated. Fully differential architectures are essential to enhance the performance of mixed analog/digital systems in terms of supply noise rejection, dynamic range and harmonic distortion and to reduce the effect of coupling between various blocks [11].

More recently, digitally programmable devices such as those in [12–14] have become attractive for mixed digital-analog applications. Traditionally, resistor and/or capacitor matrices can be used to provide tuning to analog circuits. However, they require relatively large area which typically limits the tuning accuracy to five bits or 3% of the nominal values. The proposed technique uses digitally controlled current amplifiers (DCCAs) which comprise the current division network (CDN) [15] to provide digital tuning of DCCA gains. The CDN is inherently linear (i.e. insensitive to second order effects and valid in all MOS operating regions). Moreover, the CDN can be digitally trimmed up to 10 bits accuracy without component spreading [16]. The gains of the DCCA is utilized to provide precise frequency and/or gain characteristics that can be tuned over a wide range. Poly-silicon resistors and capacitors are used to realize the filter time constants, which results in highly linear filters. In mixed analog/digital systems, the digital tuning feature of the proposed approach allows direct interfacing with the digital signal processing (DSP) part. DSP, available in most modern systems, is utilized to adapt the filter parameters with minimum additional hardware. The DSP is utilized to program the filter to operate at different bandwidths and/or different gain settings. A good example of the proposed technique is the design of an analog baseband chain for multi-standard wireless receivers [17]. In addition, digital automatic frequency tuning scheme such as that described in [18] can be employed to compensate for both components and temperature variations. The DSP tuning scheme avoids the feedthrough problems associated with the real time master-slave tuning approach which limits system dynamic ranges. A conceptual block diagram of digital automatic tuning is depicted in Fig. 1. Digital tuning feature eliminates the use of auxiliary digital to analog converters from the DSP to the analog filters resulting in simplified, flexible and low power system design solutions.

The following section discusses the design and implementation of the building blocks. Section 3 presents some basic applications such as amplifiers, integrators, and simulated active inductances. Several new digitally programmable filters are presented in Sect. 4 where a systematic design procedure to convert well-known active-RC circuits to their DCCA-RC counterparts is described. The development of fully differential architectures of the proposed approach is discussed in Sect. 5.

2 Monolithic CMOS integration

A current follower (CF) is a two terminal device which transfers current signal from a low impedance input terminal to a high impedance output terminal. The DCCA is basically a CF with programmable gain that can be controlled digitally. The DCCA can be described by the following matrix equation:

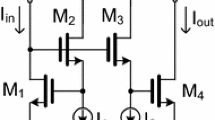

where α represents the current gain of the DCCA and the signs denote the positive (both currents are going in) and negative (one current is going in and the other is out) DCCA. The proposed DCCA with two outputs is shown in Fig. 2. When the CDN is replaced by a short circuit, the DCCA reduces to a unity gain CF. Its operation can be explained as follows. Transistors M1 and M2 provide the required virtual ground needed at the input port X. This is achieved by forcing equal currents in both transistors. Hence, their source potentials will be equal since they share the same gate, provided they operate in saturation region. Since the transconductance of a MOS transistor is small compared to a bipolar transistor, an internal feedback (M6) is incorporated to achieve low input impedance at the X terminal. The feedback reduces the input impedance by the amount of feedback yielding:

where g m and r ds are the transconductance and the output resistance of the MOSFET, respectively. Furthermore, the feedback reduces the distortion but sacrifices some of the bandwidth. The input current I x , which is forced by the constant currents of M2 and M12 to flow into M6, is conveyed to the output port Zp by current copying transistor M7. Cross-coupled current mirrors are used to change the polarity of the current and pass it to port Zn.

Compound digitally controlled current amplifier (DCCA): (a) CMOS implementation (b) Symbol (c) The current division network [16].

The operation of the CDN is similar to that of the R-2R ladder and was explained in [17]. The proper operation of the CDN requires the input node to be current driven while the output node to be virtually grounded. In the proposed DCCA, the CDN is driven by the drain current of M6 while its outputs I o is connected to the virtual ground node X. The current at terminal X (I x ) is provided by the output current of the CDN (I o ) while the negative feedback loop adjusts the current amplifier output (I z ) to be equal to the CDN input (I in ). Therefore, the transfer current characteristic of the DCCA becomes:

where d i is the ith digital bit and n is the size of control word.

The input port virtual ground property of the DCCA facilitates the addition of different signals. But low output impedance VBs are needed to allow the distribution of output signal to several subcircuits. Adoption of VBs along with DCCAs simplifies the design of various signal processing voltage and current-mode circuits. Folded-cascode op-amps, which enjoy high speed, are used to implement the VBs. DCCAs using 6-bit CDNs and the VBs have been fabricated in a 0.5 μm N-well CMOS process. The operation of the proposed DCCA and VB were experimentally verified. Throughout the testing, the supply voltages were set to ±1.6 V and the currents of the DCCA and VB were 600 and 300 μA, respectively. Figure 3 shows the dc current transfer characteristics of the DCCA under several different gain settings. The measured −3 dB bandwidth is more than 40 MHz for the different gain setting. Similarly, the measured ac response of the VB shows a bandwidth exceeding 40 MHz. Measurement results are limited by the maximum frequency that can be measured using the available network analyzer. However, post layout simulation results show that the bandwidth of the DCCF is more than 140 MHz. Also, the ac response of the VB shows a bandwidth exceeding 90 MHz.

3 Basic functions

This section presents several basic analog building blocks based on the proposed technique such as digitally programmable amplifiers, integrators, and active simulated inductors. The four basic amplifier types are shown in Fig. 4. These amplifiers exhibit wide bandwidths at different gain settings. The DCCA of Fig. 4(a) is itself a digitally controlled current amplifier with gain of A i = α. The voltage amplifier shown in Fig. 4(b) has a gain of A v = αR 2/R 1. The gain of transconductance amplifier shown in Fig. 4(c) is G T = α/R while the gain of the transresistance amplifier of Fig. 4(d) is given by R T = αR.

Figure 5 shows ac responses of the voltage amplifier of Fig. 4(b) with 0-to-6 dB gain varied in step of 1 dB. It can be seen that the amplifier exhibits almost constant bandwidth independent of the gain.

Measured ac characteristics of the voltage amplifier of Fig. 4(b) showing several gain settings

Digitally programmable ideal and lossy integrators are shown in Fig. 6. The transfer function of the ideal integrator of Fig. 6(a) is given by:

There are two realizations for the lossy integrator Fig. 6(b, c) with the following transfer functions, respectively:

Although the first employs grounded resistors its time constant is not programmable. On the other hand, the second realization exhibits programmable time constant. A weighted summer circuit utilizing the virtual ground property of the DCCA is shown in Fig. 7. The output voltage is expressed as:

A digitally programmable negative impedance converter (NIC) is shown in Fig. 8. It is straightforward to show that the circuit input impedance is given by:

When Z is a resistor (R), a negative resistor (−R/α) is obtained. Actively simulated inductors can be used in several applications such as active filters, oscillator designs and cancellation of parasitic inductances. Various topologies of active inductors based on op-amps, nullors, current-feedback amplifiers and current conveyors can be found in the literature. However, such active-RC realizations rely on the inaccurate RC time constant to determine the inductance value. Using the proposed technique a digitally programmable active inductor can be implemented. The inductor is obtained from the basic circuit of Fig. 9(a) consisting of a voltage mode integrator with infinite input impedance followed by voltage to current converter with its output fed-back to the input node. The proposed circuit of the lossless inductor is shown in Fig. 9(b). It can be shown that its input impedance is given by:

Obviously, the circuit simulates a lossless inductor with an inductance L = C 1 R 1 R 2/(α 1 α 2) Clearly, the inductance can be tuned digitally via α 1 and/or α 2. On the other hand, a negative lossless inductor can be obtained easily by changing the polarity of one of the DCCA. A lossy inductor with series resistance is shown in Fig. 9(c). The impedance of the circuit can be expressed as:

The circuit simulates a lossy inductor with L = C 1 R 1 R 2/α which can be digitally programmed via α. Similarly, by changing the polarity of the DCCA a negative inductor in series with a negative resistor can be obtained. A parallel lossy inductance circuit is shown in Fig. 9(d). Routine analysis shows that the input impedance is given by:

4 Digitally programmable filters

Two systematic approaches of designing second-order digitally programmable active filters based on the proposed technique are presented. First, biquads filters obtained by substituting the inductor L in a LCR resonator with a circuit with inductive input impedance are provided. Second, filters obtained from their two-integrator loop active-RC counterparts are considered.

4.1 Simulated active inductance based filters

Class of active filters can be obtained using active simulated inductors. This approach has the advantage of realizing inherently very low sensitivity high-order networks directly. Also, the theory and design of passive RLC filter is well-developed with tables and design manuals that can be utilized for direct synthesis. It will be demonstrated that the proposed inductor of Fig. 9(b) exhibits several attractive features when used in filter designs. First, it can be used to provide both voltage and current-mode functions. Second, when it is used to design a bandpass filter an additional lowpass function is automatically provided. A second-order voltage mode LCR bandpass filter is shown in Fig. 10(a). It can be shown that by replacing the passive inductor by the proposed simulated inductor, as shown in Fig. 10(b), the circuit provides both bandpass and lowpass responses given by:

It is worth mentioning that usually the lowpass biquad requires the simulation of a floating inductor, which is more difficult to design. It can be shown that the pole frequency (ω o ), bandwidth (ω o /Q o ), and the quality factor (Q o ) are given by: \( \omega _{o} \, = 1/{\sqrt {LC} }\, = {\sqrt {\alpha _{1} \alpha _{2} /(CC_{1} R_{1} R_{2} )} } \), \( \omega _{o} /Q_{o} = 1/(CR) \) and \( Q_{o} = R{\sqrt {\alpha _{1} \alpha _{2} C/(C_{1} R_{1} R_{2} )} } \). Clearly, center frequency can be tuned digitally using α 1 and/or α 2 without disturbing the bandwidth. Moreover, current mode bandpass and lowpass function can be realized using the same circuit by introducing an additional output current terminal to each of the DCCA and applying current input signal instead of the input voltage. The current transfer functions are given by:

Figure 11 shows the bandpass magnitude responses of the voltage-mode filter while Fig. 12 shows the response of the current-mode lowpass filter where the corner frequencies are varied digitally by controlling both α 1 and α 2, simultaneously. The bandpass filter is tuned from approximately 200 kHz to 600 kHz whereas the tuning range of the lowpass filter corner frequency is from 500 kHz to 5 MHz.

Measured bandpass response of the voltage-mode filter of Fig. 10 showing ωo tuning

Measured lowpass response of the current-mode filter of Fig. 10 showing ωo tuning

A highpass biquad can be obtained using the passive LCR circuit of Fig. 13(a). Using the proposed parallel L-R inductor, the highpass filter of Fig. 13(b) is developed. Also, the circuit provides an additional bandpass function. The transfer functions are given by:

The filter parameters are given by:\( \omega _{o} \, = {\sqrt {\alpha _{1} \alpha _{2} /(CC_{1} R_{1} R_{2} )} } \), \( \omega _{o} /Q_{o} = 1/(CR_{1} ) \) and \( Q_{o} = {\sqrt {\alpha _{1} \alpha _{2} CR_{1} /(C_{1} R_{2} )} } \). Clearly ω o , can be tuned without changing ω o /Q o via programming α 1 and/or α 2. However, the highpass filter output is not associated with a low impedance. Hence, an additional VB may be required to provide that output. Figure 14 shows the response of the highpass filter. The corner frequency is tuned from 20 kHz to 60 kHz. In summary, it can be seen that inductance simulation based circuits result in independent control of pole frequency without disturbing the bandwidth. However, they cannot be used in applications requiring the tuning of ω o without varying Q o . The following subsection develops filters enjoying independent control of ω o without disturbing Q o .

Measured response of the highpass filter of Fig. 17 showing ωo tuning

4.2 Two-integrator loop based filters

Several well-developed active-RC circuits can be converted easily to their DCCA-RC counterparts by using the basic elements presented in Sect. 2. This results in the development of filters exhibiting independent control of ω o without disturbing their Q o . For example, the op-amp based resonator filter shown in Fig. 15(a) consists of a lossy integrator, a lossless integrator and an inverter connected in a loop. Two corresponding DCCA-RC based circuits are developed using the two different lossy integrators as shown in Fig. 15(b, c). Note that the inverter function is embedded in the second DCCA. The transfer function of the bandpass and lowpass outputs of the circuit of Fig. 15(b) are given by:

The filter parameters are expressed as: \( \omega _{o} \, = {\sqrt {\alpha _{1} \alpha _{2} /(C_{1} C_{2} R_{2} R_{3} )} } \), \( \omega _{o} /Q_{o} = 1/(C_{1} R_{1} ) \) and \( Q_{o} = R_{1} {\sqrt {\alpha _{1} \alpha _{2} C_{1} /(C_{2} R_{2} R_{3} )} } \). Therefore, the corner frequency cannot be controlled without disturbing quality factor. On the other hand, the second filter of Fig. 15(c) has the same transfer functions except the second term in the denominator is multiplied by α 1 to become sα 1/(C 1 R 1). Therefore, the different filter parameters become: \( \omega _{o} \, = {\sqrt {\alpha _{1} \alpha _{2} /(C_{1} C_{2} R_{2} R_{3} )} } \), \( \omega _{o} /Q_{o} = \alpha _{1} /(C_{1} R_{1} ) \) and \( Q_{o} = R_{1} {\sqrt {\alpha _{2} C_{1} /(\alpha _{1} C_{2} R_{2} R_{3} )} } \). Hence, it can be seen that ω o can be varied digitally without changing Q o by tuning α 1 and α 2, simultaneously.

The state-variable filter or the universal filter, which provides highpass, bandpass, and lowpass functions, realized by op-amps is shown in Fig. 16(a). It is composed of two lossless integrators and a summer circuit. The DCCA-RC based state variable is shown in Fig. 16(b). Note that the function of the summer is implemented by exploiting the virtual ground and the different current polarity of the DCCA. The transfer functions of the filters are similar to those of the original filter except with the replacement of R 1 and R 2 by R 1/α 1 and R 2/α 2, respectively. This yields the following transfer functions:

Therefore, the parameter ω o and Q o are given by: \( \omega _{o} \, = {\sqrt {\alpha _{1} \alpha _{2} {\text{/}}(C_{1} C_{2} R_{1} R_{2} )} } \) and \( Q_{o} = {\sqrt {\alpha _{2} C_{1} R_{1} {\text{/}}(\alpha _{1} C_{2} R_{2} )} } \). Clearly, ω o can be tuned digitally without disturbing Q o by varying α 1 and α 2, simultaneously. Note that the DCCA-RC based filters employed grounded capacitors, which is recommended by integrated circuit technologies. The measured response of lowpass filter with variable ω o is shown in Fig. 17. The corner frequency is tuned from 600 kHz to 5 MHz. The notch and the allpass filters can be obtained by properly adding the lowpass, bandpass and the highpass filters.

Measured response of the lowpass filter of Fig. 16(b)

5 Fully differential realizations

Fully differential operation is required by most of the modern high-performance integrated circuits. This is attributed to the facts that fully differential operation improves noise rejection, increases the dynamic range particularly at low supply levels and minimizes harmonic distortions. However, a fully differential topology requires the addition of common mode feedback (CMFB) circuitry to control common-mode output voltage and without it common-mode voltage is left to drift. There are several approaches to develop the fully differential architectures for the proposed circuits. One way is to develop fully differential realizations for both the DCCA and VB, which require modifications in their CMOS realizations. This method would require a separate CMFB circuit for each element. Alternatively, a single CMFB circuit can be employed to establish the common-mode voltage of both the DCCA and VB [17] and as shown in Fig. 18. This method is straightforward, easier to develop, and avoids the use of redundant CMFB circuits. Figure 19 shows the design of the fully differential architecture of the DCCA-VB including the CMFB circuit.

Die photograph of the fully differential DCCA-VB element is shown in Fig. 20. It occupies an area of approximately 0.3x0.32 mm2 in a standard 0.5 μm N-well CMOS technology. The inputs of the CMFB circuit are coming from the low impedance outputs of the VBs. This simplifies the design of the input stage of the CMFB circuit to two resistors (Rcm) and two capacitors (Ccm).

The operation of the CMFB circuit was explained in [17]. The measured DC response of the fully differential DCCA-VB with the X’s and Z’s terminals loaded with 1 kΩ resistors is shown in Fig. 21 while the ac response is shown in Fig. 22. The transient response of a square-wave input of 1 Vpp and 1 MHz frequency is shown in Fig. 23. The 1% settling time is approximately 40 ns. The measured input referred noise of the fully differential DCCA-VB is \( 17.3\;{\text{nV/}}{\sqrt {{\text{Hz}}} } \). The nonlinearity of the circuit was determined using the two tones intermodulation test. The measured input third intercept point IIP3 is found to be 31.4 dBm.

Using this fully differential basic building block circuit, fully differential architectures of the proposed circuits can be implemented easily. For example, Fig. 24 shows the fully differential version of the universal filter of Fig. 16(b). The measured bandpass filter function is shown in Fig. 25 where the center frequency is tuned from 48 kHz to 500 kHz. The common mode rejection ratio (CMMR) and power supply rejection ratios (for both negative and positive supplies) were measured to be better than 45 and 40 dB, respectively.

Measured response of the bandpass filter of Fig. 24 showing center frequency tuning

6 Conclusions

A digitally programmable approach of designing analog and mixed signal CMOS integrated circuits is presented. The proposed technique based on digitally controlled current amplifier (DCCA) and unity gain voltage buffer achieves wide frequency operating range. Employing poly-silicon resistors and capacitors, it exhibits high linearity. The DCCA is utilized to provide digital tuning of the design parameters of the proposed circuits. Basic building blocks such as amplifiers, integrators and inductors are developed. Systematic approaches of designing voltage and current-mode filters are described. Circuits based on the proposed technique achieve wide tuning ranges with high resolution without component spreading. The tuning resolution depends on the size of the CDN. With the experimental setup of 6-bit CDN, the gain and frequency characteristics of filters can be adjusted with 1.5% accuracy. However, the resolution can be improved to better than 0.1% when using 10-bit CDN. Fully differential architecture of the proposed approach is developed. The DCCA and VB were fabricated in a standard 0.5 μm CMOS technology. All of the proposed techniques and circuits are experimentally verified.

Non-ideal analysis studying the frequency limitations can be performed to each circuit separately. In general, however, it can be observed that, for all of the proposed circuits, all internal nodes, except those of integrating capacitors, are either at virtual ground or low impedance (output terminal of VBs). Thus all parasitic poles and zeroes are expected to be at very high frequencies. The relatively low band response of the measured filter data is limited by the breadboard implementation of the various filters, in the presence of parasitic capacitances in the order of 20 pF. In integrated circuits, parasitics are much smaller; hence, operation with higher bandwidths can be demonstrated.

References

Durham, A., Redman-White, W., & Hughes, J. (1992). High-linearity continuous time filter in 5-V VLSI CMOS. IEEE Journal of Solid-State Circuits, 27, 1270–1276.

Roberts, G., & Sedra, A. (1988). All current-mode frequency selective circuits. Electronics Letters, 25, 183–194.

Ismail, M., Smith, S., & Beale, R. (1988). A new MOSFET-C universal filter structure for VLSI. IEEE Journal of Solid-State Circuits, SC-23, 183–194.

Toumazou, C., Lidgey, J., & Haigh, D. (1990). Analogue IC design: The current mode approach. London: Peter Peregrinus Ltd.

Wilson, B. (1990). Recent development in current conveyors and current mode circuits. Proceedings of the Institute of Electrical Engineering pt G, 137, 63–77.

Liu, S.-I., Chen, J.-J., & Hwang, Y.-S. (1995). New current mode biquad filters using current followers. IEEE Transactions on Circuits and Systems, 42, 380–383.

Gupta, S., & Senani, R. (2006). New voltage-mode/current-mode universal biquad filter using unity-gain cells. International Journal of Electronics, 93, 769–775.

Senani, R., & Gupta, S. (2006). New universal filter using only current followers as active elements. International Journal of Electronics and Communication, 60, 251–256.

Soliman, A. (1998). Equal-R, equal-C current mode Butterworth lowpass filters. IEICE Transactions on Fundamentals, E81-A, 340–342.

Weng, R.-M., Lai, J.-R., & Lee, M.-H. (2000). New universal biquad filters using only two unity-gain cells. International Journal of Electronics, 87, 57–61.

Rudell, J., Ou, J.-J., Cho, T., Chien, G., Brianti, F., Weldon, J., & Gray, P. (1997). A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone application. IEEE Journal of Solid-State Circuits, SC-32, 2071–2088.

Park, S., Kim, J., & Choi, S. (2005). Digitally controlled wideband CMOS variable gain amplifier (Vol. 2, pp. 896–899). Presented at the 7th International Conference on Advanced Communication Technology (ICACT).

Mahmoud, S., Hashiesh, M., & Soliman, A. (2005) Low-voltage digitally controlled fully differential current conveyor. IEEE Transactions on Circuits and Systems I-Regular Papers, 52, 2055–2064.

Wang, C.-C., Lee, C.-L., Lin, L.-P., Tseng, Y.-L. (2005). Wideband 70 dB CMOS digital variable gain amplifier design for DVB-T receiver’s AGC (Vol. 1, pp. 356–359). Presented at Proceedings of International Symposium Circuits and Systems (ISCAS).

Bult, K., & Geelen, C. (1992). An inherently linear and compact MOST-only current division technique. IEEE Journal of Solid-State Circuits, SC-27, 1730–1735.

Hammershchmied, C., & Huang, Q. (1998). Design and implementation of an untrimmed MOSFT-only 10-bit A/D converter with −79 dB THD. IEEE Journal of Solid-State Circuits, 33, 1148–1157.

Alzaher, H., Elwan, H., & Ismail, M. (2002). A CMOS highly linear channel select filter for 3G multi-standard integrated wireless receivers. IEEE Journal of Solid-State Circuits, 37, 27–37.

Khorramabadi, H., Tarsia, M., & Woo, N. (1996). Baseband filters for IS-95 CDMA receiver applications featuring digital automatic frequency tuning (pp.172–173). Presented at International Solid State Circuits Conference, San Francisco.

Acknowledgment

The author would like to thank the support of KFUPM.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Alzaher, H.A. A CMOS digitally programmable filter technique for VLSI applications. Analog Integr Circ Sig Process 55, 177–187 (2008). https://doi.org/10.1007/s10470-008-9154-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-008-9154-0