Abstract

Leakage power dissipation is the dominant contributor of total power dissipation in nanoscale complementary metal oxide semiconductor (CMOS) integrated circuits. CMOS technology scaling demands for a reduced power supply, low threshold voltage, high transistor density and reduced oxide thickness, which has led to significant increase in leakage power especially during standby mode. Here in this paper, at first we review some of the existing techniques for leakage minimization and pointed out their merits and shortcomings. We then propose a novel transistor level approach called leakage control NMOS transistor (LCNT) for leakage minimization. The proposed technique inserts two leakage control transistors (all N-type) within a standard CMOS logic circuit. The gate terminal of the leakage control transistors are connected with the drain of the pull-up transistors. Performance of the proposed technique is investigated in terms of area, power, delay, and power-delay product applying on some basic gates and benchmark circuits. The performance metrics of the proposed LCNT are then compared with other existing techniques. Extensive SPICE simulations were carried out using 32 nm predictive technology model. Simulation results indicate that the proposed technique is quite efficient in minimizing the leakage power which is found out to be 48.4 %.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent years, increasing demand of portable digital systems has led to rapid and innovative development in the field of low power design. The development of these portable devices requiring high performance and low power dissipation such as in mobile phones, notebook computers and personal digital assistants (PDAs). In high performance digital VLSI systems like microprocessor, digital signal processor and other applications, power dissipation is a major concern. High power dissipation reduces battery life and it requires extra cooling and packaging cost. Power consumption in a logic gate can be expressed (by Sayed and Al Asaad 2006) as

The above equation shows three sources of power consumption, (1) Pdynamic is due to the charging and discharging of output node capacitance, (2) Pshort-circuit is due to the conducting path between the supply and ground, (3) Pstatic is due to the leakage current.

In designing a VLSI circuit area, power dissipation and propagation delay are the major design parameters. Today, complementary metal oxide semiconductor (CMOS) device size has been scale down drastically to achieve the performance metrics of VLSI chips (Ekekwe and Etienne-Cummings 2006). As the technology scaled down to deep nanometer level, the power supply, threshold (Vt) and device geometry gets reduces (Chin et al. 2005). The sub-threshold current continue to increase exponentially, when the Vt of the device is reduced. The leakage current is now a dominant part of total power dissipation as the technology scales down (Butzen et al. 2010).

According to international technology roadmap for semiconductor (ITRS), total power consumption is significantly contributed by the leakage power (as per International Technology Roadmap for Semiconductor 2009). It is expected that leakage power can increase up to 32 times per device (Roy et al. 2000). So it is important to need robust technique to reduce leakage power dissipation.

There are three primary concepts for reducing the leakages at gate level designs. These are body-biasing, multi-threshold techniques and transistor stacking (Tsui et al. 2008). In this paper, we analyze first the leakage minimization techniques, which have been proposed earlier for CMOS VLSI circuits. Then, we propose a new circuit technique called leakage control NMOS transistor(LCNT), which is self controlled and does not require any control circuitry to monitor the state of the circuit.The remainder of the paper is organized as follows. Section 2 describes the background work. Section 3 discusses the proposed design. Section 4 gives the analysis of the results. Finally, Sect. 5 concludes this paper.

2 Background

Many design techniques have been proposed to minimize leakage power. Multi-threshold CMOS (MTCMOS) (Mutoh et al. 1995) has been found to be very effective technique to minimize leakage in standby mode. The main drawbacks of the technique are: firstly, the propagation delay increases due to the presence of high Vt sleep transistor in active mode. Secondly, proper sizing of sleep transistors in a large circuit is a very tedious task. Moreover, timing is a critical concern for sleep signal generation and finally the data retention is also a big problem, when the sleep transistors are turned OFF. The variable threshold CMOS (VTMOS) reduces the standby power by increasing the Vt with body bias. But the major drawback of this technique is that it requires an additional circuitry for body bias generation (Kuroda et al. 1996). In dual threshold CMOS (DTMOS) (Drake et al. 2003), high Vt transistors are used in non-critical path to reduce the leakage current and low Vt transistors are used to improve logic performance. But the overall delay of circuit increases due to high Vt transistors. In stack effect (Narendran et al. 2001), two or more series transistors are turned OFF to reduce the leakage current in standby mode, however area is a penalty in this approach. The sleepy stack (Park et al. 2004) approach combines the sleep and stack approaches. This technique reduces the leakage power and delay, but the area penalty is significant issue in this approach as every transistor is replaced by three equivalent transistors. The leakage feedback approach (Kao and Chandrakasan 2001) solves the problem of data retention by utilizing two additional helper transistors to maintain logic state during sleep mode, but the area and the delay are the other issues in this approach.

Sleepy keeper utilizes the idea of leakage feedback technique (Hun and Mooney 2006). But it does not require any inverter at the output node as because the helper transistors positions are interchanged in the leakage feedback path. Data retention is not a problem in this approach but the signal level at the output node is weak in standby mode.

LECTOR (Hanchate and Ranganathan 2004) technique utilizes two leakage control transistors (LCTs) which are inserted between pull-up network (PUN) and pull-down network (PDN) in a CMOS gate as illustrated in Fig. 1. LCTs causes increase in the resistance of the path from Vdd to ground. In this arrangement, one of the LCT is always near its cutoff region, leading to significant decrease in leakage current. The wiring condition ensures that one of the LCTs will be near to its cutoff region irrespective of logic inputs applied to the logic gate. The basic idea behind this approach is the reduction of leakage power by effective stacking of transistor from supply voltage to ground. It is observed that when more than one transistor is OFF from supply voltage to ground, it is far less leaky than when only one transistor is in OFF state as in Narendra et al. (2001) and Sirichotiyakul et al. (2002). LECTOR does not require any control circuitry to monitor the states of the circuit. In this way it avoids the sacrifice of dynamic power which is consumed by additional circuitry. This technique is good for leakage reduction but this technique is not capable of reducing propagation delay.

GALEOR technique uses the same structure as LECTOR, except that the locations of extra gate leakage transistors (GLT) are now swapped as shown in Fig. 2. These GLTs are high Vt transistors offering higher resistance to leakage currents. A PMOS GLT is located between PDN and output whereas, an NMOS GLT is located between PUN and output (Katrue and Kudithipudi 2008). Leakage power saving is achieved by using high Vt.GLT transistors. GALEOR technique however, suffers a significant problem that the low signal level is very much higher than 0 V and high signal level is very much lower than Vdd. ONOFIC(Sharma and PattanaikM 2014) is a circuit level leakage reduction technique called on/off logic approach.ONOFIC logic block is inserted between PUN and PDN as shown in Fig. 3.

The logic block is called ONOFIC because for any output logic level this logic block must be in ON or OFF condition. If ONOFIC block is in ‘ON’ condition it shows that both the ONOFIC transistors are in linear region while in ‘OFF’ state both the transistors are in cutoff mode. This approach is simple and needs single threshold extra insert transistor. The propagation delay penalty in this technique is also less than LECTOR technique because single NMOS transistor between PUN and PDN is used to control the leakage current. On the other hand, leakage minimization in this technique is not as good as LECTOR technique because only a single NMOS transistor is creating the leakage resistance path between PUN and PDN.

There is another low leakage transistor level approach called INDEP (input dependent) (Sharma et al. 2015). The idea behind this approach is to reduce the leakage power by effective transistor stack in the path from voltage supply to ground. INDEP approach uses two extra inserted transistors between PUN and PDN. The Vt of this approach is same as PUN and PDN. This technique is good in reducing the leakage power. However, the leakage saving in this approach is based on appropriate selection of boolean logic input signals. So, the selection of input signals is needed to be done by algorithms which take extensive computational time.

3 Proposed design

The proposed technique is a circuit level approach for minimizing the leakage current in CMOS logic gate. This technique is called leakage control NMOS transistor (LCNT). Because, it uses two N-type leakage control transistors LCT1 and LCT2 which are inserted between PUN and PDN as shown in Fig. 4. The gate terminal of both LCT1 and LCT2 are connected to NP which is the output node. The switching of both the LCT’s are controlled by the voltage at the node NP.This technique is further illustrated with the help of a CMOS NAND gate as shown in Fig. 5.

When input vector AB = 00, both the NMOS transistors MN1 and MN2 are turned OFFin PDN and both the PMOS transistors are turned ON in PUN. As a result, both the leakage control transistors (LCT1and LCT2) are turned ON. As the LCTs are in series and are turned ON so there is 2 Vt drop which will cause a reduced voltage in the path from output node to ground. Moreover, the two OFF NMOS transistors (MN1 and MN2) are offering more resistance, so we can expect a reduced leakage current. Again, when the input vectors are AB = 01 or 10, it will turn OFF one of the NMOS transistor in PDN and turn OFF one of the PMOS transistor in PUN. So, both the LCTs will behave exactly in the same manner as when the input vector AB = 00. In the case of input vector AB = 11, both the PMOS transistors are turned OFF in PUN and both NMOS transistors are turned ON in PDN. So both the leakage control transistor enters into their cut-OFF region, thereby offering highest resistance (due to stack effect) to any leakage current that would flow from PUN to PDN. Hence, it minimizes the leakage although both the NMOS transistors MN1 and MN2 are ON. Thus, it is clear that when the LCTs are ON they provide a good conducting path with minimum delay.

Whereas, when the LCTs are OFF, it provides the stacking effect. Consequently, it minimizes the leakage current. The proposed technique uses the same Vt devices for the entire circuit. This technique also solves the problem of using dual Vt transistors which can reduce the performance of the circuit. There are few other techniques in the literature which also uses the same Vt such as LECTOR and ONOFIC.

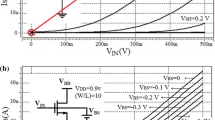

Simulated DC characteristics of conventional, LECTOR, GALEOR and LCNT using 2-input NAND gates are shown in Fig. 6. The DC transfer characteristic is obtained through simulation, keeping input B fixed to 1 V and A is varied from 0 to 1 V. In CMOS circuits, propagation delay of a gate (Park and Mooney 2006) is approximately given by

where, CL is the load capacitance, Vdd is the supply voltage, IDS is the drain current in the saturation, Vt is the threshold voltage and A is a constant. From the expression of propagation delay we can expect that as we increase the load capacitance, delay time (t pd ) will increase. Again with a high drain current (I DS ) delay will be small. In the proposed design, we have a higher output node capacitance. So, we expect delay to rise, but this is nullified by the increase in drain current because of additional capacitive load as observed in DC characteristic. Leakage current in MOSFET devices is mainly guided by sub-threshold leakage current.

Sub-threshold current also vary exponentially with Vt (Kao and Chandrakasan 2000) and can be given as:

where, Vth is thermal voltage, W is width, n is a constant and S = nVth ln0 is the sub-threshold slope of 100 mV/decade, which means for each 100 mV, decrease in Vt will cause an order of magnitude increase in leakage current.

Figure 6 shows the DC transfer characteristics of GALEOR, LECTOR, LCNT and the proposed designs as obtained through T-Spice simulation. LECTOR shows near to ideal DC transfer characteristics with a transition delay time of about 200 µS. If we look at the transfer characteristics of GALEOR, we find that it is the worst amongst all.

In case of LCNT, the logic high is good and approaching to ideal transfer characteristics. However, the logic low is poor. But if we look at the transition time of all the plots, we find that LECTOR is as close as the conventional design and is about 200 µs, however, for LCNT it is 250 µs.

Figure 7 shows the transient curve obtained by TANNER EDA tool at various nodes of all designs simulated for 32 nm technology at 0.8 V supply voltage. It can be observe from the curve LCT NAND gate produces exact output voltage levels. In case of GALEOR technique, the output voltage level is not considered to be a good ‘0’ and a good ‘1’. However, in case of proposed LCNT technique, the output waveform gives a good logic ‘1’ but the logic ‘0’ is not as good as ONOFIC.

4 Results

In this section, we compare and analyze the area, average power, delay and power-delay product (PDP) of the proposed design with conventional, LECTOR, GALEOR and ONOFIC. To analyze the performance matrices, we have used Tanner EDA tool using 32 nm PTM (predictive technology model) technology with a power supply of 0.8 V.

4.1 Leakage power

To estimate the leakage power accurately, at first the static leakage for each static input vector is calculated and thereafter, it is summed up to get the total leakage. This way, the total leakage power is calculated for all possible input vectors. Table 1 show the leakage power results for the case of a two input NAND gate, where the total leakage is computed as the sum of leakages for all possible input vectors. Similarly, for all the benchmark circuits and CMOS logic gates leakage power is calculated and the values are displayed in Table 2. Here in the calculation we have not considered any power dissipation due to switching activity. The percentage of leakage power saving is compared with the conventional circuit. Leakage power dissipation is a function of temperature (Faraji et al. 2013). Comparative results of static power dissipation at different temperature are also shown in Fig. 8. We can observe from the figure that as we go on increasing the temperature, leakage power dissipation of the circuit increases gradually. We have also analysed the comparative results of all the techniques at different technology nodes such as 65, 45 and 32 nm which are displayed in Fig. 9. It is to be noted that with technology scaling apart from Vt, the power supply Vdd is also scaled which causes the overall power dissipation to reduce, although leakage power increases.

Table 3 shows as we go on increasing W/L ratio LCTs in LCNT circuit, the leakage power increases. The leakage power dissipation can be ranked in the increasing order as follows: GALEOR < LCNT < LECTOR < ONOFIC < Conventional.

4.2 Delay

Table 4 shows the comparative analysis of propagation delay in case of conventional, LECTOR, GALEOR and LCNT based circuits. In all the techniques, extra leakage control transistors are inserted to reduce the leakage power but these extra transistors raises the propagation delay of the circuit. The increasing order of propagation delay for different approaches can be given as conventional < ONOFIC < LCNT < LECTOR < GALEOR.Among all the techniques, ONOFIC has the least propagation delay and GALEOR has the highest propagation delay. In LCNT, as two NMOS LCTs are inserted itgives a better speed of operation than LECTOR. From Fig. 10, we can observe that, as we go on increasing the W/L ratio of LCTs, the rise and fall time of LCNT decreases. Figure 11 shows that as technology node shrinks down, the delay of the circuit slightly increases in almost all the techniques which is because of additional leakage control transistors. Whereas in case of conventional circuit the delay remains almost the same.

4.3 Power-delay product (PDP)

Table 5 presents power-delay product (PDP) of all the designs. The (−) sign indicates that power delay product is decreasing with respect to conventional circuit. It can be observed that LCNT technique have minimum PDP.

4.4 Area Comparison

Layout area of each of the target circuit, using a particular design style is measured in microwind tool with 32 nm technology. Table 6 shows the area estimation in the target circuits using the proposed and other existing designs. As the proposed technique uses two additional leakage control transistors, so the area in the LCNT is more than conventional design.

4.5 Active power dissipation

Active power is measured by calculating the average power dissipation while asserting semi-random input vectors. The size of semi-random input vectors depend on the number of inputs present in the circuit. Both the static and dynamic power are included in active power calculation. We measure the active power of CMOS logic gates and benchmark circuits by asserting all the input vectors. Table 7 shows that the proposed design has the highest active power saving than all the other designs. This is because of low dynamic power consumption caused by reduced switching activity in the N-type LCTs and low static power consumption due to stack effect.

5 Conclusion

In nanoscale CMOS circuits, leakage power has become a more dominating component of total power consumption in battery operated portable systems. Here in this paper, LCNT-a new self controlled low leakage approach has been presented for nanoscale CMOS circuits. It has been observed that LCNT provides a better leakage reduction with minimal propagation delay, consequently giving a least value of PDP. We have analyzed and evaluated the performance level of the proposed approach and compared it with the existing leakage reduction techniques. It is found thatthe proposed technique minimizes the average leakage by about 48.40 %.

References

Butzen PF, da Rosa Jr LS, Chiappetta Filho EJ, Reis AI, Ribas RP (2010) Standby power consumption estimation by interacting leakage current mechanisms in nanoscaled CMOS digital circuits. Microelectron J 41(4):247–255

Chin P, Zukowski CA, Gristede GD, Kosonocky SV (2005) Characterization of logic circuit techniques and optimization for high-leakage CMOS technologies. Integr VLSI J 38(3):491–504

Drake AJ, Zamdmer N, Nowka KJ, Brown RB (2003) Analysis of the impact of gate body signal phase on DTMOS Inverters in 0.13 µm PD-SOI. In: IEEE international SOI conference, pp 99–100

Ekekwe N, Etienne-Cummings R (2006) Power dissipation sources and possible control techniques in ultra deep submicron CMOS technologies. Microelectron J 37(9):851–860

Faraji R, Hamid Reza N, Majid Rahimi N, Mohammad A (2013) New SRAM design using body bias technique for low-power and high-speed applications. Int J Circuit Theory Appl 42(11):1189–1202

Hanchate N, Ranganathan N (2004) Lector: a technique for leakage reduction in CMOS circuits. IEEE Trans. VLSI Integr Syst 12(2):196–205

Hun K, Mooney VJ (2006) Sleepy keeper: a new approach to low-leakage power VLSI design. In: Proc. IFIP international conference on very large scale integration, pp 367–372

International Technology Roadmap for Semiconductor (2009). http://www.itrs.net

Kao J, Chandrakasan A (2000) Dual-threshold voltage techniques forlow-power digital circuits. IEEE J Solid-State Circuit 35(7):1009–1018

Kao J, Chandrakasan A (2001) MTCMOS sequential circuits. In: Proceedings of European solid-state circuits conference, pp 332–335

Katrue S, Kudithipudi D(2008) GALEOR: leakage reduction for CMOS circuits. In: 15th IEEE international conference on electronics, circuits and systems, pp 574–577

Kuroda T, Fujita T, Mita S, Nagamatsu T, Yoshioka S, Suzuki K, Sano F, Norishima M, Murota M, Kako M, Kinugawa M, Kakumu M, Sakurai T (1996) A 0.9 V, 150 MHz, 10 mW, 4 mm2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme. IEEE J Solid Circuit 31(11):1770–1779

Mutoh S, Douseki T, Matsuya Y, Aoki T, Shigematsu S, Yamada J (1995) 1 V power supply high-speed digital circuit technology with multithreshold-voltage CMOS. IEEE J Solid-State Circuit 30(8):847–854

Narendra S, Borkar S, De V, Antoniadis D, Chandrakasan AP (2001) Scaling of stack effect and its application for leakage reduction. In: Proc. IEEE ISLPLED, pp 195–200

Narendran S, Borkar S, De V, Antoniadisn D, Chandrakasann A (2001). In: Proceedings ISLPED, pp 195–200

Park JC, Mooney VJ (2006) Sleepy stack leakage reduction. IEEE Trans VLSI Syst 14(11):1250–1263

Park JC, Mooney III VJ, Pfeiffenberger P (2004) Sleepy stack reduction of leakage power. In: Proceeding of the international workshop on power and timing modeling, optimization and simulation, pp 148–158

Roy K, Prasad SC, Horowitz MA (2000) Low-power CMOS VLSI circuit design, chapter 5. Wiley, New York, p 214–219

Sayed A, Al Asaad H (2006) A new low power high performance flip-flop. In: 49th IEEE international midwest symposium on circuits and systems, pp 723–726

Sharma VK, Pattanaik M, Raj B (2014) ONOFIC approach: low power high speed nanoscale VLSI circuits design. Int J Electron 101(1):61–73 (Taylor and Francis)

Sharma VK, Pattanaik M, Raj B (2015) INDEP approach for leakage reduction in nanoscale CMOS circuits. Int J Electron 102(2):200–215 (Taylor and Francis)

Sirichotiyakul S, Edwards T, Oh C, Panda R, Blaauw D (2002) Duet: an accurate leakage estimation and optimization tool for dual-V circuits. IEEE Trans VLSI Syst 10(2):79–90

Tsui CY, Au RYC, Choi RYK (2008) Minimizing the dynamic and sub-threshold leakage power consumption using least leakage vector-assisted technology mapping. Integr VLSI J 41(1):76–86

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lorenzo, R., Chaudhury, S. LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsyst Technol 23, 4245–4253 (2017). https://doi.org/10.1007/s00542-016-2996-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-016-2996-y