Abstract

This paper presents a mathematical modeling insight for the novel heterogate dielectric-dual material gate-GAA TFET (HD-DMG-GAA-TFET) and validating the results with TCAD simulation. By using the appropriate boundary conditions and continuity equations, the Poisson’s equation is solved to obtain the potential profile. The developed model is used to study the analog performance parameters such as subthreshold swing (SS), threshold voltage (Vth), transconductance (gm), drain conductance (gd), device efficiency (gm/Ids), intrinsic gain (gm/gd), channel resistance (Rch) and output resistance (Ro). Further, to optimize the effect of metal work function on analog performance, three different combinations of DMG configurations has been studied. The results demonstrated that for a difference of 0.4 eV, the analog performance of the device is optimized. Low off current and high value of on current resulting into a higher ION/IOFF ratio has been obtained, which is appropriate for sub-nanometre devices and low standby power applications. The analytical results obtained from the proposed model shows good agreement with the simulated results obtained with the ATLAS device simulator.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Continuously scaling down the MOSFETs dimensions to sub-nanometer region lead to escalation in the power consumption (active and passive) in modern microelectronic circuits. Reducing the applied bias (according to the scaling factor) to solve this dilemma leads to reduction in gate overdrive. Along with higher power density, the fundamental limit of kT/q (due to thermal process) which corresponds to a subthreshold swing (SS) of 60 mV/dec also hindered further scaling of threshold voltage (Vth) and off current. To overcome these limitations, there is a renewed interest in exploring new devices that uses a new current mechanism, and that does not involve carriers traveling over a potential barrier. Among various new devices Tunnel FET has been studied extensively in the past few years. TFET uses BTBT mechanism at the tunneling junction (the source channel junction) and normal drift diffusion mechanism away from the tunneling junction (Cho et al. 2011).

TFET has the potential to lower the SS beyond the 60 mV/dec limit of conventional MOSFETs along with the extremely low OFF-current. Therefore, TFET seems to be a well adaptive candidate for ultimately scaled switches and low power devices with excellent immunity to short channel effects (SCEs) (Bhuwalka et al. 2006; Born et al. 2006; Nirschl et al. 2006; Mookerjea et al. 2009). The major roadblock with the planar TFETs is its lower ON-state current (ION), which results in lower operating speed. In order to resolve this issue, numerous kinds of TFETs with various structures and materials such as double-gate, delta layer, SiGe, and PNPN structures have been proposed (Toh et al. 2007; Boucart and Ionescu 2007a, b; Toh et al. 2008; Mallik and Chattopadhyay 2011; Jhaveri et al. 2010; Cho et al. 2011; Lee et al. 2010; Noguchi et al. 2015). To enhance the ION, Silicon nanowire TFET has already been fabricated (Gandhi et al. 2011). Further, a high-k material has been locally inserted (near the source side) in the gate dielectric to form heterogate-dielectric (HD) TFETs (Choi and Lee 2010; Mallik and Chattopadhyay 2011). The presence of high-k dielectric results into a higher band bending due to increase in surface potential (at a constant gate bias) (Jhaveri et al. 2010; Lee et al. 2012; Madan et al. 2015a, b). This higher band bending leads to reduction in tunneling barrier width, which further increases the generation rate and hence the ION.

Another major problem with TFET is ambipolarity. The ambipolarity in the device is the conduction for both high positive and high negative Vgs while keeping the VDS only in one direction (negative for p-type devices and positive for n-type devices) (Cho et al. 2011; Conde et al. 2014; Hraziia et al. 2012; Lee et al. 2010; Shaker et al. 2015). Ambipolarity can be reduced by using a HD structure, in which the gate dielectric is split into two regions; high-k dielectric near the source side and low-k dielectric near the drain side. The higher value of dielectric improves the electrical coupling between the gate and the tunneling junction and hence, increases the tunneling rate. The DMG further helps in the improvement of ON and OFF current characteristics. Lower work function metal near the source side increases the band overlap and hence reduces the tunneling barrier width. This reduced tunneling barrier increases the tunneling probability, and the generation rate which results in higher ION and the higher value of work function near the drain side increases the tunneling barrier width and hence helps in reducing the IOFF. So an optimum value of metal work function value at source and drain side should be chosen to trade-off between ON and OFF characteristics. In this work, a heterogate dielectric, Dual material gate, gate-all around (GAA) structure has been applied to TFET to enhance analog performance of the device (Madan et al. 2014).

The paper is structured as follows: Sect. 2 describes the device structure, parameters and simulation models used in this work, Sect. 3 describes the model formulation for the device Sect. 4 describes the results verification and discussions in which the effect of DMG configuration on the analog performance of the device has been studied. Finally, the conclusions are drawn in Sect. 5.

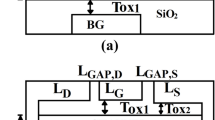

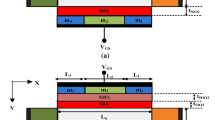

2 Device structure, parameters and simulation models

The device structural parameters used in both simulations and analytical model are fixed: channel length is 50 nm, with L1 (20 nm) and L2 (30 nm), gate oxide thickness (tox) = 3 nm and radius (R) = 10 nm. Further, the source (p+), drain (n+) and channel doping (p) are 1020, 5 × 1018 and 1016 cm−3 respectively. To reduce ambipolarity effect source and drain are doped asymmetrically. In this analysis the analog performance is studied for the three different cases of DMG scheme to optimize the device for better analog performance and the cases are as stated below.

-

Case 1. ΦM1 = 4.1 eV and ΦM2 = 4.8 eV

-

Case 2. ΦM1 = 4.3 eV and ΦM2 = 4.8 eV

-

Case 3. ΦM1 = 4.4 eV and ΦM2 = 4.8 eV

Region 1 consists of dielectric constant ε1 = 21 HfO2 (near the source) and region 2 consists of ε2 = 3.9 SiO2 (near the drain) for all the cases. The source and drain junctions are abruptly doped for an effective band to band tunneling and the interface of high-k and SiO2 is abrupt. The simulation device structure i.e. HD-DMG-GAA-TFET consisting of heterogate dielectric and Dual material gate is shown in Fig. 1. All simulations have been performed using the ATLAS device simulator. The most important model for TFET simulations is the band-to-band tunneling (BTBT) model. Non-local models have a more physical basis and don’t depend on the electric field at the individual mesh points in the simulated device structure, but rather on band diagrams calculated along cross-sections through the device. According to BBT.NONLOCAL, the tunneling happens through the 1D slice, at the tunnel junction, where each slice and the tunnel junction are perpendicular to each other. These slices are parallel to themselves. For nonlocal BTBT model, the quantum tunneling meshing has been used at the source-channel junction. In n-TFET, the electrons tunnel through the valence band of the source to conduction band of the channel by BTBT mechanism and then the carriers drift from channel to drain. Thus, to incorporate the transport away from the tunneling junction drift diffusion model is used (Boucart and Ionescu 2007a, b). The bandgap narrowing model is used in the simulations to incorporate the effect of heavily doped source and drain regions (as tunneling current is a sturdy function of bandgap). Instead of Boltzmann statistics, Fermi–Dirac statistics have been used for the same reason (heavily source and drain doping). The models activated during simulation are as follows: concentration and field dependent mobility model, Shockley–Read–Hall for carrier recombination, non-local band to band tunneling, band gap narrowing, Fermi–Dirac statistics and drift diffusion (Fukuda et al. 2013; Atlas User’s Manual 2014). The parameters used in simulation along with their values are listed in Table 1.

3 Model formulation for HD-DMG-GAA-TFET

Assuming that the influence of the charge carrier and fixed carriers are uniform in the channel, it can be neglected. The parabolic potential profile along the radial direction is assumed and based on the following boundary conditions, the Poisson’s equation is solved.

-

1.

The surface potential is only z-dependent

$$\Phi _{si} (R,z) =\Phi _{si} (z)$$(1) -

2.

The Electric field at the center of the channel is zero

$$\left. {\frac{{d\Phi _{si} (r,z)}}{dr}} \right|_{r = 0} = 0$$(2) -

3.

Electric field at Si/SiO2 interface is continuous

$$\left. {\frac{{d\Phi _{si} (r,z)}}{dr}} \right|_{r = R} = \frac{{C_{fi} }}{{\varepsilon_{si} }}\left[ {V_{GS} -\Phi _{si} (z) - V_{FBi} } \right]$$(3)where; \(V_{FBi} = \phi_{mi} - \phi_{s}\) is the flatband voltage. i = 1and 2 for region 1 and 2 respectively and Φ s is the semiconductor work function.

$$\phi_{s} = \chi_{si} + E_{g} /2q + \phi_{F}$$(4)\({\text{and }}\phi_{F} = k_{B} T/q(\ln (N_{Ch} /n_{i} ))\) is the fermi potential.Where the parameters, symbols and their values are as listed in Table 2.

Cf1 and Cf2 are the capacitances per unit area of the gate dielectric for region 1 and 2 respectively and are given by

where t1 = t2 = tox, is the gate oxide thickness.

Solving Eqs. (1)–(5) we can obtain

The general solution of (6) is

Now using the following boundary conditions at the interface of each region, coefficients Ax and Ay can be determined.

At the source end

And at the drain end

At the interface of region 1 and region 2,

The lateral electric field (2D) is given by

The lateral surface electric field is given by

Transverse electric field (2D)

The tunneling generation rate determined by Eq. (13) is integrated over the volume (πr2 w T) to obtain the drain current. Where w T is the tunneling barrier width defined as the shortest distance between the valence band of the source and conduction band of the channel. It is determined from the surface potential profile, by taking the difference between the points where the surface potential falls by an amount equal to Eg/q below the surface potential and where the potential is Φs and is calculated as:

The tunneling generation rate can be evaluated as

where A, B and γ are the parameters dependent on the effective mass of electron and hole.

where mtunnel is the effective mass = 0.25m0 and m0 is the rest mass of an electron. The values of A (BB.A) and B (BB.B) are listed in Table 1. The average electric field E avg is calculated by integrating the total electric field E Tot over the barrier width \(w_{T}\) as:

The expression for drain current (Ids) is obtained as:

4 Result verification and discussion

Figure 2 shows the comparison of proposed device i.e. HD-DMG-GAA-TFET with the gate all around tunnel FET as reported by Ying et al. (2014). As evident from Fig. 2 that the Vth of GAA-TFET is high as compared to the proposed device. Moreover, the ION of proposed device is 219 times enhanced in comparison to the GAA TFET. Both the lower Vth and higher drain current makes the DMG scheme beneficial for VLSI/analog applications. Therefore in this work, critical analog parameters such as transconductance gm, output conductance gd, early voltage VEA, device efficiency gm/Ids, intrinsic gain Av, channel resistance Rch and output resistance Rout has been studied to analyze the effect of DMG on the device performance.

Drain current–voltage comparison of proposed device HD-DMG-GAA-TFET with gate all around tunnel FET data from Ying et al. (2014)

The effect of gate bias and metal work function on electric field near source and drain side is shown in Fig. 3a. As expected, the electric field is enhanced (near both source and drain side) with an increase in gate bias. Further, as the metal near drain side is constant; hence, the electric field near the drain is almost same for each case. With the increase in the difference in metal work function, the electric field near the source side enhances, which results in an additional lowering of barrier width and thus an increase in tunneling rate is obtained, which eventually leads to greater tunneling current and sought out the primary obstruction of TFET. Further, the SS is the amount of gate voltage required for one decade change in the drain current. In order to reduce the switching power of CMOS circuits, SS of the device should be as low as possible. Moreover, to accurately predict the circuit behavior, the Vth is an important parameter. The influence of metal work functions on the SS and Vth of the device is shown in Fig. 3b.

According to the previously reported work (Choi and Choi 2013), the ION can be enhanced by using a gate metal of lower work function near the source in comparison with metal used near drain side and to reduce the IOFF, metal work function near drain should be high as compared to the metal used near the source. So in order to achieve an optimum device performance, metal near drain is kept constant (ΦM2 = 4.8 eV) and the metal near source side is varied. As we increase the work function of metal near source side from 4.1 to 4.4 eV, the SS of the device is decreasing, but the Vth of the device is increasing. So the metal work function should be chosen such that the device is optimized in terms of both SS and Vth.

The transfer characteristics (Ids–Vgs) are shown in Fig. 4a in both log scale and linear scale for each case. The graph shows the IOFF of the order of 10−17 A and ION of the order of 10−4 A, which results in IOFF/ION ratio of the order of 1013. The lower value of IOFF leads to a lower value of static power dissipation. Again, an increase in difference in metal work function leads to enhancement of ION by 1.5 times in case 1 as compared to case 3, but simultaneously IOFF has also been increased significantly. So we need to optimize the values of metal work function to obtain an optimum value of ION/IOFF ratio depending on the application. The increase in ION is the main advantage of heterogate dielectric and dual material gate. Also, it can be clearly seen from the graph that the model prediction and ATLAS device simulation are in good agreement. Figure 4b shows the variation of ION/IOFF with different metal work function configurations of DMG. It is apparent from the bar graph that as work function of metal 1 increases from 4.1 to 4.3 eV the ION/IOFF ratio enhances by an order of 105 times. Moreover for ɸM1 = 4.4 eV, the ION/IOFF ratio reduces by 0.47 times w.r.t. case 2 and increases w.r.t. case 1. The reduction in ION/IOFF ratio in case 3 w.r.t. case 2 is mainly attributed to enhanced IOFF as shown in Fig. 4a. Transconductance gm, which is basically the first order derivative of the drain current with respect to the gate voltage at constant drain voltage, is shown in Fig. 4c. Transconductance decides the current driving capability of the device for a given input voltage swing. It is clear from Fig. 4c that among the three cases, the higher value of transconductance is achieved for case 1. In each case, the transconductance of the device is very much higher in the case of on state as compared to off state. So for enhanced tunneling current and transconductance, the difference of metal work function should be possibly large.

The output characteristic (Ids–Vds) for each case is shown in Fig. 5a. The saturation mechanism of output characteristics in the case of TFET is mainly attributed to the saturation of tunneling barrier width for higher drain bias at a constant gate bias (Boucart and Ionescu 2007a, b, Madan et al. 2015a, b). It is evident from the figure that the device predicts a qualitative agreement in linear regime and also shows a good saturation in drain current for higher drain voltages. Among the three cases, the tunneling current is enhanced by 2.7 times in case 1 with respect to case 3; thus makes it suitable for analog applications. Figure 5b illustrates the effect of DMG configurations on drain/output conductance gd. Further, in order to achieve high gain, transistors should have low output conductance for analog applications. The output conductance is increasing with an increase in drain bias and then attains maxima and further increase of drain bias reduces the drain conductance because of higher drain resistance at higher drain bias. As we reduce the metal work function difference, output conductance decreases, as is evident from Fig. 5b.

Figure 6a illustrates comparison of the device efficiency gm/Ids for each case. Device efficiency is the ability to convert dc power into ac gain performance at a particular drain bias. For each case, the highest value of gm/Ids is obtained for the weak inversion region and then a linear decrease is obtained with an increase in gate bias. Among the three cases, case 3 has higher device efficiency. For each case, the device efficiency has reached a value greater than 40 V−1 (the fundamental limit of conventional MOSFET) in the subthreshold region. Intrinsic gain is a valuable analog circuit design parameter used for designing amplifiers such as an operational transconductance amplifier (OTA). For better analog performance, an intrinsic gain of the device should be as high as possible. Comparison between of the intrinsic gain for different metal work function configuration with respect to gate bias is presented in Fig. 6b. The intrinsic voltage gain is obtained at the constant drain bias Vds = 1.0 V, making use of the relation Av = gm/gd. Highest intrinsic gain for a metal work function difference of 0.4 eV is attributed to the dominated decrease in output conductance in comparison with the increase in transconductance.

The influence of gate voltage and dual material gate configurations on channel resistance Rch is demonstrated in Fig. 7a. For Vgs = 0 V, no band bending is there, ensuring into higher tunneling barrier width at the tunneling junction, resulting into very high Rch of the order of 1015 Ω. As the gate bias increases, bands in the channel move downwards resulting in lowering of the tunneling barrier width as if a conductive channel is formed and thus drops the Rch to a value of several KΩ’s. Moreover, at lower gate bias, higher Rch has been obtained for the case when metal work function difference is 0.4 eV, which shows a better OFF state characteristics for this configuration in comparison with the rest of the cases when the metal work function difference is 0.7 and 0.5 eV. Another important parameter for analog application is the output resistance or the drain resistance Ro. Drain resistance is numerically equal to the inverse of the output conductance. The variation of output resistance with the drain to source voltage is shown in Fig. 7b. It is clearly shown in the figure that in the linear region, the output resistance is very small, because of strong dependence of the drain current on drain voltage. But as the drain current saturates for the higher drain bias, Ro increases monotonically. It is evident from the figure that for the case when metal work function difference is 0.4 eV, Ro is found to be extremely high due to the better output saturation current as shown in Fig. 7b.

5 Conclusion

The present work is the detailed mathematical modeling insight for the analog performance of HD-DMG-GAA-TFET. The results obtained by simulations and analytical modeling are in good agreement. The tuning of metal work functions has been done to optimize the effect of Dual metal gate on the analog performance, which shows that both device efficiency and device gain are improved for a metal work function difference of 0.4 eV. Decrease in SS and increase in Vth is found on decreasing the difference between work functions of two metal used near source and drain junction. Moreover, IOFF/ION ratio of the order of 1013 has been obtained for the same DMG configuration, making it suitable for low power applications. Enhancement of channel resistance and output resistance is obtained as we decrease the difference of the metal work functions. Moreover, it has been evaluated that SS is less than 60 mV/decade in each case, and device efficiency is more than 40 V−1 in the subthreshold region. This indicates that the developed model also validates with the fact that TFET overcomes the fundamental limit of MOSFET.

References

ATLAS User’s Manual (2014) SILVACO Int., Santa Clara, CA

Bhuwalka KK, Born M, Schindler M, Schmidt M, Sulima T, Eisele I (2006) P-channel tunnel field-effect transistors down to sub-50 nm channel lengths. Jpn J Appl Phys 45:3106–3109. doi:10.1143/JJAP.45.3106

Born M, Bhuwalka KK, Schindler M, Abelein U, Schmidt M, Sulima T, Eisele I (2006) Tunnel FET: a CMOS device for high temperature applications. In: Proceedings of 25th international conference on microelectronics, Belgrade, Serbia and Montenegro, pp 124–127. doi:10.1109/ICMEL.2006.1650911

Boucart B, Ionescu AM (2007a) Length scaling of the double gate tunnel FET with a high-K gate dielectric. Solid-State Electron 51(12):1500–1507. doi:10.1016/j.sse.2007.09.014

Boucart K, Ionescu AM (2007b) Double gate tunnel FET with high-k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. doi:10.1109/TED.2007.899389

Cho S, Sun MC, Kim G, Kamins TI, Park BG, Harris JS (2011) Design optimization of a type-I heterojunction tunneling field-effect transistor (I-HTFET) for high performance logic technology. J Semicond Technol Sci 11(3):182–189. doi:10.5573/JSTS.2011.11.3.182

Choi KM, Choi WY (2013) Work-function variation effects of tunneling field-effect transistors (TFETs). IEEE Electron Device Lett 34(8):942–944. doi:10.1109/LED.2013.2264824

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57(9):2317–2319. doi:10.1109/TED.2010.2052167

Conde AO, Garcia-Sanchez FJ, Muci J, Sucre-Gonzalez A, Martino JA, Agopian PGD, Claeys C (2014) Threshold voltage extraction in tunnel FETs. Solid-State Electron 93:49–55. doi:10.1016/j.sse.2013.12.010

Fukuda K, Mori T, Mizubayashi W, Morita Y, Tanabe A, Masahara M, Yasuda T, Migita S, Ota H (2013) A compact model for tunnel field effect transistors incorporating nonlocal band to band tunneling. J Appl Phys 114(14):144512. doi:10.1063/1.4824535

Gandhi R, Chen Z, Singh N, Banerjee K, Lee S (2011) CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with ≤ 50-mV/decade subthreshold swing. IEEE Electron Device Lett 32(11):1504–1506. doi:10.1109/LED.2011.2165331

Hraziia Vladimirescu A, Amara A, Anghel C (2012) An analysis on the ambipolar current in Si double–gate tunnel FETs. Solid-State Electron 70:67–72. doi:10.1016/j.sse.2011.11.009

Jhaveri R, Nagavarapu V, Woo JCS (2010) Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans Electron Devices 58(1):80–86. doi:10.1109/TED.2010.2089525

Lee DS, Yang HS, Kang KC, Lee JE, Lee JH, Cho S, Park BG (2010) Simulation of gate-all-around tunnel field-effect transistor with an n-doped layer. IEICE Trans Electron 93-C(5):540–545. doi:10.1587/transele.E93.C.540

Lee JS, Choi WY, Kang IM (2012) Characteristics of gate-all-around hetero-gate-dielectric tunneling field-effect transistors. Jpn J Appl Phys 51:06FE03. doi:10.1143/JJAP.51.06FE03

Madan J, Gupta RS, Chaujar R (2014) Influence of heterogeneous gate dielectric on hetero-dielectric-DMG-GAATFET for improved tunneling current. Int J Adv Technol Eng Sci 2(1):41–47

Madan J, Gupta RS, Chaujar R (2015a) Analytical drain current formulation for gate dielectric engineered dual material gate-gate all around-tunneling field effect transistor. Jpn J Appl Phys 54:094202. doi:10.7567/JJAP.54.094202

Madan J, Gupta RS, Chaujar R (2015b) Threshold voltage model of a hetero gate dielectric dual material gate GAA Tunnel FET. Advanced manufacturing, electronics and microsystems: techconnect Briefs 2015, pp 254–257. doi:10.13140/RG.2.1.3081.2003

Mallik A, Chattopadhyay A (2011) Drain-dependence of tunnel field-effect transistor characteristics: the role of the channel. IEEE Trans Electron Devices 58(12):4250–4257. doi:10.1109/TED.2011.2169416

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans Electron Devices 56(9):2092–2098. doi:10.1109/TED.2009.2026516

Nirschl T, Henzler S, Fischer J, Fulde M, Bargagli-Stoffi A, Sterkel M, Sedlmeir J, Weber C, Heinrich R, Schaper U, Einfeld J, Neubert R, Feldmann U, Stahrenberg K, Ruderer E, Georgakos G, Huber A, Kakoschke R, Hansch W, Schmitt-Landsiede D (2006) Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid-State Electron 50:44–51. doi:10.1016/j.sse.2005.10.045

Noguchi M, Kim SH, Yokoyama M, Ichikawa O, Osada T, Hata M, Takenaka M, Takagi S (2015) High Ion/Ioff and low subthreshold slope planar-type InGaAs tunnel FETs with Zn-diffused source junctions. J Appl Phys 118:045712-1–045712-15. doi:10.1063/1.4927265

Shaker A, Ossaimee M, Zekry A, Abouelatta M (2015) Influence of gate overlap engineering on ambipolar and high frequency characteristics of tunnel-CNTFET. Superlattices Microstruct. doi:10.1016/j.spmi.2015.08.008

Toh EH, Wang GH, Samudra G, Yeo YC (2007) Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett 90(26):263507–263510. doi:10.1063/1.2748366

Toh EH, Wang GH, Chan L, Sylvester D, Heng CH, Samudra GS, Yeo YC (2008) Device design and scalability of a double-gate tunneling field-effect transistor with silicon–germanium source. Jpn J Appl Phys 47(4S):2593–2597. doi:10.1143/JJAP.47.2593

Ying L, He Jin, Mansun C, Cai-Xia D, Yun Y, Wei Z, Wen W, Wan-Ling D, Wen-Ping W (2014) An analytical model for gate-all-around silicon nanowire tunneling field effect transistors. Chin Phys B 23(9):097102-1-6. doi:10.1088/1674-1056/23/9/097102

Acknowledgments

Authors would like to thank Microelectronics Research Lab, Department of Engineering Physics Delhi Technological University to carry out this work. One of the authors (Jaya Madan) would like to thank University Grants Commission, Govt. of India, for providing the necessary financial assistance during the course of this research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Madan, J., Gupta, R.S. & Chaujar, R. Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog applications. Microsyst Technol 23, 4091–4098 (2017). https://doi.org/10.1007/s00542-016-2872-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-016-2872-9