Abstract

An improved Chimps optimizer algorithm is proposed in this paper and is applied for the performance optimization of tunnel FET architectures for use in low power VLSI circuits. The steep subthreshold characteristics of TFET improves device performance and make it suitable for low power digital and memory applications. Classical Chimps optimizer has poor convergence and problem to stuck into local minima for high dimensional problems. This research focuses on mathematical model of divergent thinking and sensual movement of chimps in four different forms named attacker, barrier, chaser, and driver for simulation. The improved variant of Chimps optimizer has been proposed in this research and named as Imp-Chimp. To validate the efficacy and feasibility of the suggested technique, it has been examined for standard benchmarks and multidisciplinary engineering design problems to solve non-convex, non-linear, and typical engineering design problems. The suggested technique variants have been evaluated for seven standard unimodal benchmark functions, six standard multi modal benchmark functions, ten standard fixed dimension benchmark functions and engineering design problems (i. e., TFET, BTBT). The outcomes of this method have been compared with other existing optimization methods considering convergence speed as well as for searching local and global optimal solutions. The testing results show the better performance of the proposed method. The paper also demonstrates the tunnel field effect transistor (TFET) as a promising device for low power electronic circuits and an engineering problem where the Imp-Chimp optimizer can be implemented for performance improvement. The TFET is based on the carrier generation using the quantum mechanical process of the band-to-band tunneling (BTBT). TFET can meet the requirements of a device that can perform on low supply voltage with reduced leakage currents and low sub-threshold swing. TFET can be optimized to give similar performance as MOSFET, but with much lower power consumption.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Artificial intelligence as well as machine learning are rapidly increasing because it is easy to implement to solve real-life issues which are continuous or discontinuous, constrained or unconstrained [1. , 2. ]. For handling these characteristics using conventional approaches such as quasi-Newton method, sequential quadratic programming, fast steepest and conjugate gradient etc. faced difficulties to solve them [3. , 4. ]. In existing research, all these methods were tested experimentally and noticed they are not exactly sufficient to obtain effectual solutions to non-continuous, non- differential problems and real life multi-model problems [5]. Thus, meta-heuristics algorithm came into picture which is very simple to understand and easily be implemented to handle several issues. Generally, in optimization, techniques depend on inhabitants to find out solution on optimal and sub optimal which is closer to exact optimal value, located at nearest point. In this algorithm the optimization process starts unless population set of the individuals are generated and then relaying on optimization method every individual act for candidate solution for the problem. Thus, by updating present location with best position, the population will be up to date by reaching maximum iterations. In modern research the meta-heuristics algorithm which gives better efficiency, less expensive and successful in implementation is given prior importance to utilize.

With such qualities embedded, a new hybrid meta-heuristics optimization technique, Imp-Chimp-SHO algorithm proposed in this paper relies on nature-lead and mathematical formulation of search functions were developed to give good competition to already existing meta-heuristics optimizers. The intention to design this optimization technique is motivated by individual intelligence and sensual movement of social carnivores, named Chimps for their mass hunting mannerism in targeting the prey [6]. Hence, a stochastic and meta-heuristic mathematical model intended to handle various optimization problems and is verified by testing experimentally in this research work.

It is a fact that Optimization technique is an extensive field of study and rapid progress in work is visualized as researchers are implementing new methods to give better solutions to various problems targeting challenges and can succeed in findings. In research, past methods ladder to new methods exhibiting their hybrid novel approach to reduce low efficient methods from present. A collection of research papers is presented in literature review to enlist the shortcomings of recent algorithms in this proposed study.

Broadly speaking meta-heuristics are of two types, named single-solution based m-heuristics and population solution based meta-heuristics. Improved Chimp algorithm (ICHIMP) variant belongs to swarm intelligence-based algorithm of the categories of population meta-heuristics, which is combined along with newly introduced swarm intelligence-based algorithm called Spotted Hyena Optimizer algorithm and named as Improved Chimp-Spotted Hyena Optimizer (ICHIMP-SHO) algorithm which is introduced in this paper. Overall, this algorithm is simple to apply and involves very less operators than other population-based algorithms with minimum computational efforts.

2 Literature review

Since few years meta-heuristics techniques came into usage widely because of its efficiency when compared to other existing techniques. These algorithms give better solution to real-life optimization issues. Hence, to solve these optimization issues there is a need of new meta-heuristics algorithm to introduce. As well in ever increasing utilization of engineering applications, meta-heuristics optimization algorithms (MOAs) have its importance. Very rapidly the necessity of latest MOAs is increasing because of solving complicated problems. It acquires distinct profits as: (i) Its plain algorithmic structure helps to implement it easily; (ii) This suits real-life problems in engineering as it is derivation-free mechanism; (iii) When compared to traditional optimization algorithms, this have better ability to minimize local optima; (iv)This is flexible to apply on different problems as its structure doesn’t need any particular changes; (v) Because of its simplicity and efficiency, this can be applied simultaneously in hardware applications as well as in computing applications (like (FPGA)-field programmable gate array) [6]. To limit the drawbacks of classical methods, the meta-heuristics search algorithms were introduced. Few such algorithms are biography algorithm [7], artificial bee colony [8], differential evolution (DE) [9], genetic algorithm [10], cuckoo search algorithm [11], bacterial foraging algorithm [12], flower pollination algorithm [13], chemical reaction optimization [14], firefly algorithm [15], immune algorithm [16], teaching learning algorithm [17], particle swarm optimization algorithm (PSO) [18], grey wolf optimization [19], social spider algorithm [20], gravitational search algorithm [12], bat algorithm [21]. How meta-heuristics algorithms are classified is explained in [22, 23], and with reference to this [24, 25], meta-heuristics algorithms are considered by natural behaviour and divided as single solution based for example variable neighbourhood search [26], Vortex search algorithm (VS) [27], Simulated Annealing (SA) [28], genetic algorithm (GA) [10], Tabu search (TS) [29] is an emerging way to find solution for combinatorial real world problems in covering and scheduling, and cuckoo search algorithm [11], gravitational search algorithm (GSA) [12] are population-based algorithms. Evolutionary programming (EP) [30] is a fast and classical evolutionary programming’s were performed on real world problems, generated a Gaussian random number rather than a Cauchy random number. Harmony search (HS) [31] is inspired by using music production cycle analogy. HS may not need the initial values of the variables for decision. Forest optimisation algorithm (FOA) [32] is for finding maximum value and minimal value with a real application, and found that the FOA can typically find solutions correctly and the reliability of the fruit fly swarm search route obviously has to do with the quantity of fruit fly. Grey wolf optimizer algorithm (GWO) [33] work was inspired by a Swarm intelligence optimization through the grey wolves and the suggested model imitated the grey wolves' social hierarchical and hunting behaviour. Moth flame optimizer (MFO) [34] here, key influence of this optimizer is the moth navigation system called transverse orientation in nature. Moths migrate in darkness by keeping a pre-set moon angle, a very effectual method for long distance flying in a straight line. But such fancy insects are stuck around artificial lights in a useless/deadly spiralling course. Stochastic Fractal Search Algorithm (SFS) [35] centred on random fractals to address global optimization problems with continuous variables, both constrained and unconstrained. In the entire optimization if only one solution carries then it is known as single solution-based algorithm and if there are many different solutions in the whole optimization phase then it is population-based algorithm, and as such the solution may coincide to the optimum very nearly. Optimization problems can find solutions by nature inspired MOAs physical or biological behaviour implementation. They are classified into four main classes [24, 36]: swarm intelligence based algorithm, evolutionary algorithms (EAs), human-based, physics-based algorithms. Evolutionary algorithms replicate features of biological generation like recombining, mutation and selecting process [22]. The famous Evolutionary algorithms are differential evolution (DE) [37] presented the minimization of potentially nonlinear and non-differentiable continuous space functions. It only requires some strong control variables, taken from a perfectly-defined number interval, evolutionary strategy (ES), Biogeography-based optimization (BBO) [38] made analysis of biological species geographical distribution, can be used to deduce algorithms suitable for optimization. Evolutionary Programming (EP), and Genetic algorithm (GA) which is drawn from Darwinian theory. As per [36, 39] physics-based algorithms analogous natural physical laws. The famous algorithms are quantum mechanics based (QMBA), gravitational search (GSA) [40] is influenced by the Gravitational Law and the theory of mass interaction. GSA utilizes Newtonian mechanics theory, and its search agent is the set of masses, central force optimization (CFO), charged system search (CSS), electromagnetism like algorithms (ELA), lightning attachment procedure optimization (LAPO). Big-Bang Big-Crunch (BBBC) [41], adaptive best-mass gravitational search algorithm (ABMGSA) [42]. Thirdly, MOAs are inspired by natural human behaviour. The best examples of them are teaching learning based optimization (TLBO) [25] which comprises of 2 phases, teaching phase and learner phase to interact with both is possible with only tuning and the problem must be rectified in a power system, imperialist competitive algorithm (ICA) [43], socio evolution and learning optimization (SELO) [44]. Fourthly, MOAs imitate social behaviour of organisms like swarms, shoals, flocks or herds [45]. For illustration particle swarm optimization (PSO), hybrid MLP and Salp swarm algorithm (MLP-SSA) [46], bat algorithm (BA), ant colony optimization (ACO), improved monarch butterfly optimization (MBO) algorithm, cuckoo search algorithm (CSA), krill herd (KH) [47], grey wolf optimizer (GWO), Grasshopper optimization approaches, binary salp swarm algorithm (BSSA), ant lion optimizer (ALO) [48], hybrid binary, artificial bee colony (ABC), hybrid dragonfly optimization algorithm and MLP (DOA-MLP) [49], improved whale trainer (IWT) [50]. Harris Hawks optimizer (HHO) [51] is being introduced to tackle different tasks of optimization. The strategy is influenced by nature's cooperative activities and by the patterns of predatory birds chasing, Harris' hawks. Henry gas solubility optimization algorithm (HGSO) [52] imitates the procedures of Henry’s rule. HGSO, aimed at matching the production and conservation capabilities of check room and stop optima local. Photon search algorithm (PSA) [40] Inspired by the properties of photons in the field of physics. Strong ability of global search and convergence. Chaotic krill herd algorithm (CKH) [53] combined chaos theory with Krill herd optimization procedure to speed up global convergence. Bird swarm algorithm (BSA) [54] depends on social interactions of swarm intelligence with bird swarm. Lightning search algorithm (LSA) [55] is a m-heuristic technique used to resolve problems on constraint optimization by following lightning phenomenon applying the concept of fast moving particles called projectiles. Multi-verse optimizer (MVO) [56] a environment lead heuristic algorithm relays on 3 stages named: wormhole, black hole, white hole. Virus colony search (VCS) [57] is a environment inspired method that affects spreading and infection stages of the host cells followed by virus for its survival in the cell environment. To find solutions for real time problems, grasshopper optimization algorithm (GOA) [58] follows grasshopper swarms behaviour. Based on the thinking ability of chicken swarm, chicken swarm optimization algorithm (CSO) [59] came into existence. Grey wolf optimizer-sine cosine algorithm (GWO-SCA) [60] is a meta-heuristics optimizer correlating the nature of wolf with mathematical sine cosine concepts. crow particle swarm optimization algorithm (CPO) [61] is a hybrid combination of crow search algorithm and particle swarm optimization. Whale optimization technique (WOA) [62] is a hybridized combinatorial meta-heuristics technique of Whale and swarm human based optimizers for finding perfect exploratory and convergence capabilities. Spotted hyena optimizer (SHO) [63] is a new meta-heuristic algorithm encouraged by the natural collaborative behaviour of spotted hyenas in searching, encircling, attacking the prey. Multi-objective spotted hyena optimizer (MOSHO) [64] is developed to reduce multiple objective functions. Modified adaptive butterfly optimization algorithm (BOA) [65] is developed based on butterfly observation that produces its own fragrance when travelling in search of food from one place to another place. Binary spotted hyena optimizer (SHO) [66] is a meta-heuristic algorithm introduced on the basis of hunting behaviour of spotted hyena which deals with discrete optimization problems. Hybrid Harris Hawks pattern search algorithm (hHH-PS) [67] is a meta-heuristic optimizer developed to figure out newer version Harris Hawks for finding solution in local and global search. Hybrid Harris Hawks-sine cosine method (hHH-SCA) [68] is influenced by virtuous behaviour of Harris Hawks which added up with mathematical concepts of sine and cosine to increase its ability in exploration and exploitation phases (Fig. 1). Bernstrain-search differential evolution algorithm (EBSD) [69] belongs to family of universal differential evolution algorithms, which is proposed based on mutation and crossover operators. Reliability based design optimization algorithm (RBDO) [70] deals with the uncertainty factors like global convergence, complicated design variables. Basically the two main components of meta-heuristics are exploitation and exploration [24]. Exploration extends searching widely to produce many different solutions, whereas exploitation focuses searching in a specified area assuming that area is the best for present. It is very much important and necessary to balance these two components exploitation and exploration in MOA to keep away the fluctuations in the rate of convergence, as well preventing local and global optimum [71, 72]. Exploitation indicates single solution based meta-heuristics and exploration indicates populated solution based meta-heuristics.

Spotted Hyena optimizer (SHO) is a new upcoming optimizer influenced by the trapping behaviour of spotted hyena. This technique benefits upon other meta-heuristics as:

-

(i)

implementation of algorithm is easy because of its simplicity structure.

-

(ii)

it makes smooth continuous solutions in local optimum.

-

(iii)

it has finer local and global search capability.

-

(iv)

due to continued diminution of search space, SHO convergence rate ids faster. And this solves many types of engineering design problems [66].

Data mining feature selection and unit commitments are the major discrete optimization issues. To solve these problems SHO is used. Feature selection targets unnecessary features and removes them from data set and minimizes computation requirement, dimensionality and results in better accuracy. In practical, the real-time problems may have huge number of features with relevant and irrelevant features. At that time, it is difficult for finding solution. Then, the characteristic selection is treated as combinatorial optimization problem. To solve this selection feature problem binary meta-heuristics algorithms are used. Few examples are binary gravitational search algorithm (BGSA) [73], binary gray wolf optimizer (BGWO) [74], binary bat algorithm (BBA) [75, 76], binary particle swarm optimization (BPSO) [77]. Hybrid particle swarm and spotted hyena optimizer algorithm (HPSSHO) [78] is a novel meta-heuristic algorithm developed to improve convergence speed. Chimp optimization algorithm (ChoA) [6] is designed based on intelligence ability of Chimps in group hunt. This algorithm is developed to solve slow convergence speed, trapping in high-dimensional problems.

A task towards identifying solutions throughout issues for optimization is a hot theme. Is if range of optimization parameters keeps increasing, its sophistication of the optimization problems will be enormous. In addition, several deterministic proposed methods are subject to local optima trapping. The meta-heuristic (MA) nature-inspired optimization techniques are designed to overcome such problems (Table 1). The major elements with these methodologies are population dependence and the absence of initial assumptions. Even so, there's really no optimization technique that can fix yet all optimization issues [79]. This thought initiated to propose a meta-heuristic hybrid variant optimizer named as improved chimp-spotted hyena optimizer (ICHIMP-SHO). It is tested on seven standard unimodal benchmark functions, six standard multi model benchmark functions, ten standard fixed dimension benchmark functions and eleven types of multidisciplinary engineering design problems. The results noticed are excellent than other existing algorithms.

The remaining part of present article contains concepts of improved chimp optimizer (IChimp) algorithm, spotted hyena optimizer (SHO) algorithm, proposed IChimp-SHO algorithm, standard benchmark functions, engineering-based optimization design problems, numerical results and discussions, outcomes of proposed algorithm, conclusion.

3 Proposed improved chimp optimizer

Chimps hunt very cleverly remembering the previous track of their attacks and are very closely related to swarm intelligence strategy and based on this behaviour a innovative algorithm known as Chimp Optimization Algorithm (ChoA) is introduced. Chimps hunt in a group very intelligently based on two phases namely exploration and exploitation. Chimps are divided into four parties specifically named as driver, barrier, chaser, and attacker. They streamline themselves by chasing, driving, blocking, and attacking in trapping the prey.

The mathematical Eqs. (1) and (2) represents driving and chasing of the prey.

Here, \(\vec{A}\), \(\xi\), and \(\vec{C}\) is the coefficient vectors, t is the number of current iterations, Chimp location vector is the \(\vec{Y}_{{{\text{Chimp}}}}\), and \(\vec{Y}_{{{\text{Prey}}}}\) is the vector of prey position.

Coefficient vectors \(\vec{A}\), \(\xi\), and \(\vec{C}\) are found out using Eqs. (5)–(7).

In the improved chimp optimizer, the Eqs. (1) and (2) has been modified as follows:

where ran (1) and ran (5) represents the random integer values and can be given by the following mathematical equation:

where SAN represents the search agent number.

\(\left| {\mathop A\limits^{ \to } } \right|\) non-linearly decreases from 2.5 to 0 in both the phases iteratively. The vectors \(\nu_{1}\) and \(\nu_{2}\) are ranged [1. ]. \(\xi\) the chaotic vector serves chimps in the process of trapping.

In this hunting process usually an attacker chimp leads this operation followed by driver, barrier, and chaser. Mathematically the actions of Chimps are imitated in the sequence initially starting from attacker, driver and then barrier; chaser will give better lead to notice the position of prey. Up till now the location of Chimps is to be updated immediately and store the best positions of Chimps.

This process is reflected mathematically in the Eqs. (9)–(21).

In the modify chimp algorithm, the \(\vec{D}_{{{\text{Attacker}}}}\) has been selected with the help of following equation:

In the modify chimp algorithm, the \(\vec{D}_{{{\text{Barrier}}}}\) has been selected with the help of following equation:

In the modify chimp algorithm, the \(\vec{D}_{Chaser}\) has been selected with the help of following equation:

In the modify chimp algorithm, the \(\vec{D}_{Driver}\) has been selected with the help of following equation:

The Eq. (2) mentioned above can be used to determine the spot of attacker, barrier, chaser and driver as per Eqs. (17)–(20) respectively.

The overall final positions of all the chimps can be obtained by taking the mean of the attacker, barrier, chaser and driver positions as per Eq. (21):

The 2-dimensional and three-dimensional view for the position of chimp from the respective prey has been depicted in Fig. 3a, b, respectively.

To generate the initial arbitrary position of search agents, the below mathematical equation can be adopted:

The PSEUDO Code for calculations of Y1, Y2, Y3 and Y4 are given in Fig. 2a, b.

This work extends an enhanced version of hunting behaviour of Improved Chimp optimizer by means of spotted hyena as depicted in Fig. 3c. To experience this consequence, the driving and chasing Eqs. (1) and (2) of I-Chimp along with hunting behaviour of spotted hyena in Eq. (19) are considered to modify into Eq. (23). The pseudo code for the suggested ICHIMP-SHO algorithm is discussed in Algorithm 1.

4 Standard benchmark functions

A cluster of different benchmark functions [30, 83] is taken to test the efficacy of the proposed ICHIMP-SHO optimization technique. Such benchmark collection is composed of three major benchmark feature classes, such as uni-modal (UM), multimodal (MM) and fixed dimensions (FD) standard benchmarks. UM, MM, FD mathematical formulations are shown in Tables 2, 3, 4, 5 and their characteristics are shown in outcomes and discussion section. For verifying standard benchmark functions performance 30 trail runs are considered.

Thirty search agents are considered in the entire research analysis, and the suggested technique is simulated for maximum 500 iterations. The ICHIMP-SHO algorithm developed was verified on Intel ® Core TM, i7-5600 CPU@2.60 GHz.

5 Results and discussions

In this research work, the introduced improved chimp-spotted hyena optimizer algorithm is tested on three major classes of standard benchmark functions to verify the presentation of the developed ICHIMP-SHO technique. The exploitation and convergence rate of ICHIMP-SHO is tested by unimodal benchmark functions which has single minimum. As the name multimodal replicates which has more than one minimum, hence these functions are utilized to test for exploration and avoid local optimum. The design variables are obtained by the difference between multimodal and fixed dimension benchmark functions. The fixed dimension benchmark functions will store these design variables and maintain a chart of previous data of search space and compares with multimodal benchmark functions.

For comprehensive comparison analysis, a record of results of developed ICHIMP-SHO algorithm were framed which were tabulated in the criteria of mean value, standard deviation, median value, best value, worst value, and parametric tests by performing with 500 iterations and maximum runs of 30.

5.1 Evaluation of (F1–F7) functions (exploitation)

The test results for unimodal (F1–F7) benchmark functions of suggested technique were illustrated in the Tables 6, 7. The mean value, standard deviation were considered for evaluation of the test results with few newly developed meta-heuristic algorithms named LSA [55], BRO [84], OEGWO [85], PSA [40], hHHO-PS [67], SHO [63], HHO [51], ECSA [86], TSO [87] and presented in Table 8. Its characteristic curves, trail runs, convergence comparative curves with other algorithms were depicted in Figs. 4, 5, 6.

5.2 Evaluation of (F8–F13) functions (exploration)

The multimodal benchmark functions (F8–F13) show the design variables in desired number in the exploration phase. The test results were tabulated in Tables 9, 10. As well the comparison of results were done with respect of mean value and standard deviation with other algorithms LSA [55], BRO [84], OEGWO [85], PSA [40], hHHO-PS [67], SHO [63], HHO [51], ECSA [86], TSO [87] and recorded in Table 11. Also its characteristics curves, trail runs, convergence comparative curves with other algorithms were depicted in Figs. 7, 8, 9.

5.3 Evaluation of (F14–F23) functions

The fixed dimensional benchmark (F14–F23) functions do not manipulate the design variables but prepares the previous search space record of multimodal benchmark functions. Tables 12, 13 are the test results of proposed algorithm and Table 14 showcases the comparative analysis of mean value and standard deviation with LSA [55], ECSA [86], TSO [87], PSA [40], hHHO-PS [67], SHO [63], HHO [51]. Figures 10, 11, 12 shows characteristics curves, trail runs, convergence comparative curves with other algorithms.

Hence, the test results for UM, MM and FD benchmarks problems are tabled in Tables 6, 7, 8, 9, 10, 11, 12, 13, 14 and the assessment of proposed optimizer with other meta-heuristics search algorithms for UM, MM and FD benchmarks problems has been given in Figs. 5, 8 and 11 and trail runs solutions for UM, MM and FD benchmarks problems has been shown in Figs. 6, 9, and 12. The above result clearly shows that proposed optimizer presents much better than other algorithms. In sub-sequent sections, the proposed optimizers have been applied to 11 engineering optimizations problems.

6 Engineering design problem

As computing is having a paradigm shift from large desktop devices to battery operated, hand-held or implantable mobile devices the demand for low power electronics is growing more and more. Despite having many superior properties like high input impedance, voltage control, unipolarity, better thermal stability, high switching speed, less noise etc., the most important reason for the widespread popularity of MOSFET, is its comparatively small dimensions and easy scalability. Reduction in the length of MOS devices has many benefits like increased number per chip or high packing density, smaller gate length means smaller gate capacitance and thus high switching speed. Length scaling also leads to voltage scaling of MOSFETs and which in turn results in minimization of power consumption, which makes it a desirable device for low power electronics [88]. However, as the dimensions are scaled further and further, controlling the OFF-state power consumption became a major challenge for MOS devices. The drain current in MOSFET flows due to the thermionic injection of charge carriers from source to channel. With the increase in gate voltage, the barrier potential between the source and the channel reduces, which leads to an increase in the drain current and gives rise to a larger OFF-state current because of subthreshold conduction and an increase in subthreshold slope. For a MOSFET the subthreshold slope may be defined as the amount gate voltage VGS required to change the drain current ID ten folds. Subthreshold slope (SS) should be as small as possible because lower SS results in a higher difference between ON and OFF state currents, thus a larger ION/IOFF ratio and lesser power dissipation at the OFF state. Mathematically the subthreshold slope of MOSFET is represented as:

where CD and Cox are depletion and oxide capacitances of the device, respectively. From Eq. (24) the minimum possible value of SS for a MOSFET is \(\frac{kT}{q}\mathrm{ln}10\), which comes out to be 60 mV/dec at room temperature of 300 K. Therefore, to get an ION/IOFF ratio of 106, we must apply a gate voltage of 6 × 60 mV = 0. 36 V. Thus, it would not be possible to achieve a high ION/IOFF ratio without sacrificing the supply voltage scaling. These basic disadvantages of MOSFET of higher OFF state currents and high subthreshold slope limit their application in low power circuits.

A device prone to these fundamental limitations of MOSFET is the prime requirement now. One such device is the tunnel field effect transistor or TFET. It can provide the solution by controlling the BTBT tunnelling phenomenon and making it the source of drive current in place of thermionic emissions in MOS devices. Structurally TFET is very similar to MOSFET, except that the source and drain here are having opposite doping. This similarity makes TFET very much compatible with MOSFET based circuits. TFETs are found to be immune to various short channel effects which is a major limitation for MOS devices [89]. TFETs are gate-controlled, reverse-biased P–I–N diodes in which the tunnelling current is controlled by the gate voltage [90]. In TFETs steep subthreshold slope lower than 60 mV/dec can be achieved because they are not bound by kT/q, which is the fundamental limit for MOSFETs, which has also been experimentally proved [91]. The energy requirements of TFET to switch between states is also much lower than MOSFET making them better switches compared to MOSFET [92, 93]. TFETs also have very low OFF-state current and high stability to temperature variations because it relies on BTBT tunneling rather than thermionic emissions for device conduction making it one of the finest candidates for low power electronic circuits. Due to low OFF-state current, steep SS and high output resistance, SiGe source TFET can be used for making ultra-low-power cellular neural network (CNN) based associative memory (AM) as well as low power SRAM cells [94,95,96,97,98]. The super-low off current, reduced temperature sensitivity and high transconductance per unit bias current of TFET is exploited in ultra-low power implantable bio-medical sensors employing TFET based Operational Transconductance Amplifier (OTA) and it is found to show sub-nW operating power [99]. TFETs due to its voltage scaling also find use in the development of SRAM memory cells for ultra-low power IoT applications [100].

The major drawback in TFET is the very low ON-state current and ambipolar conduction. A huge amount of research has been done and is still going on to increase the drive current of TFET so that it may commercially be viable in MOS circuits. Embedding a low bandgap material layer (like SiGe) near-source can increase the ON current but at the cost of a rise in OFF current which can be controlled by proper selection of gate metal work function [101, 102]. The use of double gate structure with high k gate dielectric replacing SiO2, can enhance the drive current, give better control over the channel, reduce SS and generate very few variations in device parameters on scaling of channel length [89, 103]. Insertion of dielectric pocket (DP) at the two junctions, i.e. the source-channel and channel-drain junction has led to the improvement of BTBT increasing the efficiency of the device [104]. The use of silicon on insulator (SOI) technology for the construction of TFET was found to be one of the major advances. The entire PIN structure over the buried oxide (BOX) layer can reduce the OFF-state current by reducing the bipolar parasitic conduction [105, 106]. A modified approach to SOI technology is the use of selective buried oxide (SELBOX), which has a small gap in the buried oxide. The SELBOX TFET has the added advantage of the reduction of carriers during the OFF state which is trapped by the gap. It reduces OFF-state current and ambipolarity [107, 108]. Introduction of dual gate dielectric with high k material like HfO2 towards source end and low k dielectric like SiO2 towards drain end helps in reducing ambipolar behaviour, enhances on current and provides for abrupt switching [109]. Another approach to reduce the subthreshold slope and enhance the ON-state current is the use of Ferroelectric oxides as gate dielectric in place of SiO2 [107, 108]. Research has also been carried out to use various geometrical modifications in TFETs structure to enhance its efficiency. Increasing the area of the tunnelling junction also provided enhanced ION/IOFF ratio and steep SS [110]. Vertical TFET or V-TFET is another modified structure that enables the device to have BTBT along a direction perpendicular to the gate called line tunnelling which further improves the on-state current [111]. Vertically grown low bandgap source over the channel with source pocket and hetero material also lead to a decrease in SS and increase of ION due to both line and point tunnelling [112]. Another geometrical modification of the conventional TFET includes a broken gate (BG) structure which reportedly reduces ambipolar current drastically resulting in lower OFF current and reduced power [113]. Use of three dimensional structures like gate-all-around (GAA) gives higher control of the drain current by the gate voltage and leads to superior performance [114]. There are also prospects of increasing the ON current by utilising III-V hetero materials for making TFET [115,116,117]. Newer materials like graphene [118] and Carbon nano tubes (CNT) [119] also showed promising results for implementing TFET devices in modern high density ultra-low power circuits and systems.

The present paper discusses various recent optimization techniques to obtain a suitable range of dimension and performance parameters of different TFET architectures meeting ITRS standards. Further, different transistors presented are mainly aimed at designing novel TFET models using various techniques like geometrical modifications, dielectric engineering, gate work function engineering, using asymmetric hetero materials for source and drain, playing with doping concentrations, varying the gate length for source/channel/drain underlap and overlap etc. to eliminate the fundamental limitations. Some new techniques like charge plasma-based junction less TFETs which greatly reduce fabrication complexity and leakage are also described. Further application of TFETs in biomolecule sensors and various digital circuits are also discussed.

The rest of the paper is arranged in the following order, the first section compares different optimization techniques to obtain an optimum design of TFET with improved subthreshold performances. The next section gives the readers a basic idea about the layout and structure of TFET and compares it with the structure of MOSFET. The following section familiarises with the various performance parameters of TFET like subthreshold parameters and analog/RF performance parameters. The next section discusses some of the popular existing TFET architectures and classifies them. The following section presents a comparative study of various TFET architectures introduced in the previous section based on the performance parameters discussed earlier. The last section concludes our article based on comparative analysis. A glossary is presented at the end of the article to familiarise the readers with abbreviations used in the paper specifically for different TFET architectures.

7 Basic structure of TFET

Let us examine the basic structure of a tunnelling FET now. Section 6 will elaborate on many variations of this structure, but the working principle of the TFET is based on this basic arrangement of regions, doping and terminals. Figure 13a–c shows the basic structure of an n-channel and p-channel TFET respectively.

8 Performance parameters

8.1 Threshold voltage

The threshold voltage (VT) may be defined as the minimum gate to source voltage required for the initiation of current conduction through the channel of a FET. For conventional MOS it is defined as the voltage required at the gate terminal to form an inversion layer at the channel so that a path for the flow of charge carriers is built between source and drain. But for TFET it may be defined as the minimum gate to source voltage required to align the valence band of the source and conduction band of the channel in such a way that that band to band (BTB) tunnelling between them may be initiated. For TFET threshold voltage is independent of temperature.

8.2 Subthreshold slope

The subthreshold slope may be defined as the amount of gate voltage required to produce a unit decade change in drain current [89] in the subthreshold region. Mathematically it may be given as the ratio of change in gate voltage to change in the log of drain current as

For conventional MOSFET devices, it is found to be independent of gate to source voltage and given as [101]

where CD and Cox are depletion and oxide capacitances of the device and \(kT/q\) represents the thermal limit of MOS devices which restricts them to have a minimum subthreshold slope of 60 mV/dec at T = 300 K (room temperature).

But TFET devices are not restricted by the thermal barrier, rather they depend on the tunnelling barrier at the source-channel junction. The subthreshold slope for TFET is given as [102]

Therefore, unlike MOSFET subthreshold slope of TFET is highly dependent on the gate voltage and lightly dependent upon bandgap at the tunnelling junction (source-channel junction). So, clearly sub 60 mV/dec S value may be obtained for TFET by using low VGS.

8.3 ON state current

For TFET, the ON state current ION is a very important performance evaluating parameter, it must be as high as possible for better performance. It is defined as the drain to source current IDS which flows through the device when the gate to source voltage is greater than VT. In other words, it is the drain current when the device is ON. The major contributor to ION is BTBT of electrons at the source-channel junction.

8.4 OFF state current

It is represented as IOFF. It may be defined as the amount of current which flows between drain and source when the gate to source voltage is below threshold voltage or when then the device is considered OFF. Ideally, IOFF should be tending to zero but practically it has some non-zero value due to the presence of finite subthreshold slope. IOFF has some finite value due to various leakage phenomena and ambipolar behaviour of TFET, but it must be maintained as small as possible for good performance.

The ratio between ON-state current and OFF-state current is another important performance parameter. For efficient performance of the TFET \({I}_{\mathrm{ON}}/{I}_{\mathrm{OFF}}\) should be as high as possible.

8.5 Drain induced barrier lowering (DIBL)

The drain induced barrier lowering (DIBL) is a type of short channel effects (SCE) it is responsible for lowering of threshold voltage at high drain biases. It must be as small as possible for better performance of the TFET. The high value of DIBL makes the ON-state current highly dependent on drain voltage rather than gate. It destroys the gate controllability of the device and renders it useless. Mathematically it is defined as the ratio between the difference of threshold voltages measured at high and low drain voltages to the difference between the high and low drain voltages [120].

The value of DIBL is always positive which is ensured by the negative sign in front of the formula as threshold voltage measured at high drain voltage is always lower than that measured at low drain voltage. The unit for DIBL is mV/V and it should be as low as possible.

8.6 Analog/RF performance parameters

The ultra-low-power TFET devices must have good switching speeds to be compatible with modern high-speed processors. The most important high-frequency performance parameters which decide the efficient functioning of TFETs are transconductance (gm), cut-off frequency (fT), gain bandwidth product (GBP) and transit time (τ) [121].

8.7 Transconductance

The transconductance (gm) of a TFET is defined as the rate of change of drain current to change its gate to source voltage when the drain to source voltage is kept constant. Mathematically it is given as,

It can be obtained graphically as the slope of transfer characteristic of TFET.

8.8 Cut-off frequency

Cut-off frequency (fT) is one of the crucial performance parameters for analog/RF operations. It is defined as the frequency at which the small signal, short circuit current gain reduces to one [121]. It is given as

where \({C}_{\mathrm{gs}}\) is gate to source capacitance and \({C}_{\mathrm{gd}}\) is the gate to drain capacitance. The value cut-off frequency should be high for better performance.

8.9 Gain bandwidth product

GBP is another important RF performance parameter; it is a trade-off parameter between gain and bandwidth of the device. It is responsible for determining the selectivity of a circuit. GBP is generally used to determine the device performance at DC gain of 10 [122] and is mathematically given as

8.10 Transit time

Another important parameter that determines the analog/RF performance of TFET devices is the transit time denoted by τ. Transit time specifies the time required for the charge carriers to travel from source of the device to the drain [121]. It is a measure of how fast the device functions. Mathematically it is proportional to the inverse of cut-off frequency, given as

9 Existing TFET architectures and dimensions

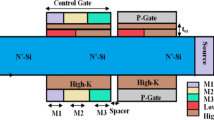

Researchers focused on various structural and geometrical modifications along with use of newer and advanced materials for the construction and modification of the basic tunnel FET structure. Some of these structures are classified and briefly explained here along with there dimensional features. Few of them focused on the use hetero dielectric structure for gate dielectric having a combination of low k and high k materials and use of low band gap material for source. Madan and Chaujar [123] suggested a TFET having gate to drain overlap, hetero gate dielectric and gate wrapped all around the channel structure called GDO HD GAA TFET (Fig. 14). The gate drain overlap suppresses the ambipolar current while hetero material for gate dielectric enhances ION. Further, the gate all around structure improves the gate control over the tunnelling current. Dimensions: channel length, Lg = 50 nm, R = 10 nm, Tox = 2 nm, gate metal Ф = 4. 3 eV, ε2 = 21 (HfO2, high k), ε1 = 3. 9 (SiO2, low k), length of high-k dielectric Lhigh-k = 10 nm and source (p+), channel (p−), Drain (n+) doping are 1 × 1020 cm−3, 1 × 1016 cm−3, 1 × 1018 cm−3 respectively are used.

In their paper Wang et al. [119] proposed a carbon nano tube-based TFET having low doping and heterogeneous gate dielectric termed as LD-HTFET (Fig. 15) and compared its performance with CNT based TFET with high k material as gate dielectric (HK-TFET) and only heterogeneous gate dielectric based TFET (HTFET). The quantum kinetic model is used at the device level for the analysis of switching behaviour and HF figure of merits in presence of light doping and modulation of gate dielectric. The LD-HTFET is found to have better HF and switching figures. Circuit simulations with HSPICE suggested good improvements in terms of static noise margin, delay energy and power delay product. The device dimensions of the LD-HTFET include gate length of 20 nm, thickness of gate oxide of 2 nm, source/drain expansion length Lsd = 20 nm, and gate oxide of ε = 3.9 and 16 for low and high k respectively.

Patel et al. [121] proposed a nanowire TFET having heterogeneous gate dielectric and source made of low bandgap SiGe material called SiGe S NW TFET (Fig. 16) and evaluated its performance to common Si nanowire TFET for implementation of analog circuits like operational amplifiers. Due to construction source using SiGe having narrow bandgap and use of HfO2 (having high value of k) as gate oxide towards the source-channel junction, there is 640 times increase in ON current and subthreshold swing of 6.54 mV/dec obtained as compared to 36.24 mV/dec for the conventional device. Improvement in ON current resulted in increased transconductance which resulted in better RF/analog performance. Change in diameter of the device impacts SS but variation in channel length is insignificant. Device dimensions are, length of drain/source/gate = 20 nm, diameter of nano wire = 20 nm, tox = 2 nm, substrate doping = 1 × 1017 cm−3, drain doping = 1 × 1018 cm−3 and source doping = 1 × 1020 cm−3.

Few researchers used muliple combination of gate metals having varring work functions. For example Raad et al. [124] proposed a hetero gate dielectric based dual-gate metal work function TFET (HGD DW TFET) which suppresses ambipolar behaviour and enhances RF figure of merits. Its structure (Fig. 17) has three gate metals having different work functions, Ф1 = Ф3 = 4.0 eV and Ф2 = 4.6 eV. Low Ф on the drain side reduces ambipolarity and enhances ON current towards the source. SiO2 having a lower value of k is used towards the drain end to reduce ambipolar leakage and enhance RF performance while high k (HfO2) on the source side helps in enhancing drive current by reducing tunnelling width of the source to channel interface. The device dimensions used by them are, LD = LS = 100 nm, LG = 50 nm which includes th = 2 nm of high-density layer, tox = 2 nm, tSi = 10 nm, length of Ф1 and Ф3 = 10 nm and drain/source doping of 1 × 1020 cm−3.

Bagga and Dasgupta [125] proposed Si nanowire-based triple metal gate all around TFET (TM GAA TFET) (Fig. 18). The gate wrapped around the structure with three metals having distinct work functions helps create a barrier to suppress backward tunnelling current from drain and it also bends the energy band near-source which increases the driving current. The device is verified using Poisson’s equation and Kane’s model-based analytical model. In cylindrical coordinates, Poisson’s equation may be written as:

The device dimensions are, length of the channel L = L1 + L2 + L3 = 60 nm where metal M1 length L1 = 10 nm, metal M2 length L2 = 30 nm, metal M3 length L3 = 20 nm, work functions ФM1 = 4. 4 eV, ФM2 = 4. 8 eV, ФM3 = 4. 6 eV, Gate Oxide thickness tox = 2 nm and Si nano wire radius R = 10 nm.

Many work is done on geometrical modification of the channel to make it stand vertical so that both line and point tunneling can be incorporated. Shih et al. [126] proposed a U-shaped gate heterojunction (InGaAs/GaAsSb) vertical tunnelling field effect transistor (U HJ VTFET) (Fig. 19). The structure shows BTBT normal to the Gate surface which improves the ON current. This device has a provision for independent and separate control of ON and OFF currents by insertion of a layer of spacer material at the interface of channel and drain. The Heterojunction of (InGaAs/GaAsSb) provides a very small bandgap of 0.02 eV. Performance-wise the device can achieve 520 µA/µm of drive current, an ION/IOFF ratio of 107. The dimensions of the structure are Lg = 100 nm, Ld = 50 nm on both sides of gate, gate oxide (HfO2) thickness of 2 nm, Gate metal work function 4.7 eV, Source (GaAsSb)-p + doping of 3 × 1019 cm−3 and drain (InGaAs)-n + doping of 2 × 1018 cm−3. The device does not require any complex fabrication steps and is compatible with VLSI technology.

Kim et al. [127] proposed a TFET called VS-TFET having a vertical structure of the drain, channel and source stack with two gates on either side along with lightly doped Si to sandwich the stack from both sides (Fig. 20). The vertical channel in the device empowers it to have BTBT perpendicular to the gate field and great control over the tunnelling current. The device has a gradual doping profile for suppression of ambipolar conduction and NH3 plasma treatment was done to have a better quality of gate dielectric. Very low SS of 17 mV/dec and high ION/IOFF = 104 is obtained in the device. Further it was suggested that the device can be modified for higher performance by constructing the tunnelling junction by narrow band gap materials like SiGe or Ge. The device dimensions include, source height = 100 nm with p-type doping = 5 × 1019 cm−3, channel height = 175 nm with p-type doping = 1 × 1017 cm−3 and drain height = 50 nm with n-type doping = 1 × 1020 cm−3. Uddin Shaikh and Loan [128] proposed a drain-engineered TFET having four gates and a T shaped channel, called DE-QG-TFET as illustrated in Fig. 21. The device has a novel construction having two sources in the lateral direction and a vertically extended drain above the channel which is T shaped and is controlled by four gates. The unique construction highly suppresses ambipolar leakage compared to lateral double gate TFET. The device has double the ON current of a conventional DG TFET and ION/IOFF ratio five orders higher. Further the analog/RF figure of merits are also considerably improved. The device dimensions are, p type source doping of 1 × 1020 cm−1, n type channel doping of 1 × 1017 cm−1, n type drain doping of 5 × 1018 cm−1, tSi = 10 nm, gate oxide SiO2 thickness of 3 nm and gate metal work function of 4.5 eV.

Kumar et al. [129] proposed a-Si nanotube-based TFET having two gates one running through the centre of the channel as a core and another wrapped around outside the channel as a shell (Fig. 22). The device with both inner core gate as well as outer shell based wrapped all-around gate gives better control over the channel and improves drive capacity. It is compared with conventional nanowire TFET for analog and RF performance and found to be much superior. Its vertical device geometry helps in enhancing the ON-state current to a great extent. The dimensions used are channel thickness = 50 nm, tox = 1 nm, radius = 5 nm, source doping = 1 × 1020 cm−3, drain doping = 5 × 1018 cm−3, channel doping = 1 × 1017 cm−3 and gate work function = 4.4 eV.

Research is also done to include the charge plasma based junction less technology to reduce various leakages and minimise fabrication complexity and cost. Nigam et al. [130] designed a TFET based on charge plasma technology having a control gate of dual metals, termed as DMCG-CPTFET (Fig. 23). The device is junction less and based on charge plasma-based electrical doping to reduce the fabrication complexity. The p + source is formed by the deposition of platinum (Ф = 5.93 eV) and the n + drain is formed by the deposition of hafnium (Ф = 3.9 eV) over Si. The gate is made of three metals with different work functions. Metal M1 (Ф1) called tunnelling gate on the source side, M3 (Ф3) called auxiliary gate on the drain side and M2 (Ф2) called control gate at the centre. φ1 = φ3 < φ2 is taken for best performance. The tunnelling gate improves ON state performance while the auxiliary gate suppresses ambipolarity. The device dimensions are, length of gate Lg = 50 nm, thickness of Silicon layer tSi = 10 nm, thickness of oxide layer tox = 1 nm, tunnelling gate length L1 = 10 nm, control gate length L2 = 25 nm and auxiliary gate length L3 = 15 nm.

Yadav et al. [122] proposed doping less TFET having heterogeneous gate dielectric and work function engineering at both gate and drain called HGD DE DMG DL TFET (Fig. 24). The device is doping less based on the charge plasma technology which has large ease in fabrication. Here dual work function is used at two places; over drain it reduces ambipolarity and a gate terminal, works for the enhancement of ON-state current. Again, there is a hetero gate dielectric whose combined effect along with work function modulation both at gate as well as drain results in a reduction in subthreshold slope, threshold voltage and improved high-frequency responses. The device dimensions are the length of drain metal LD = 40 nm with Φ = 3.9 eV, length of the extended portion of drain metal LB = 10 nm with Φ = 4.3 eV, length gate metal LG = 40 nm with Φ = 4.6 eV, length of extended portion gate metal LC = 10 nm with Φ = 4.0 eV, length of source metal LS = 50 nm with Φ = 5.93 eV, the thickness of silicon body tSi = 10 nm and thickness of oxide layer tox = 1 nm.

Yadav et al. [131] proposed a TFET having electrical doping, gate underlapping and heterogeneous body with low bandgap SiGe at source and Si at drain and channel. The device called HM-GUL-ED-TFET is shown in Fig. 25. The gate under-lap helps in suppressing the ambipolarity and gate leakage current (Ig). The Si0. 5Ge material having narrow bandgap at the source helps in improving DC and RF figures of merit. Further the device uses charge plasma-based electrical doping which eases fabrication drastically. The device dimensions include length of electrical drain/source LED = LES = 50 nm with work function = 4.5 eV, tSi = 10 nm, tox = 1.5 nm, control gate length LCG = 30 nm, gate underlap LGUL = 20 nm and substrate doping = 1 × 1015 cm−3.

Devi and Bhowmick [132] proposed a junctionless TFET with a SiGe n + pocket doping near source end called JL-TFET (Fig. 26) which can be applied for the construction of efficient inverter circuits. The device has two metal gates, a fixed gate and a control gate having different work functions. It uses junction less technology, through which its N + -N + -N + structure is converted into PIN using suitable voltage variations at the two gates. A SiGe N + pocket is used near the source end which generates a path for tunnelling current transverse to the gate oxide in addition to the usual lateral path and drastically increases ON state current to about 5.7 × 10−4 A. By varying the fixed gate and control gate work functions to 5 and 4.5 eV respectively, close to 43.6 mV/dec of subthreshold swing value may be attained. Further, RF evaluation also shows superior performance concerning conventional JL-TFET. Dimensions of the device are, doping for source, channel and drain is 1 × 1017 cm−3, gate oxide thickness Tox = 2 nm, channel length Lg = 35 nm, Si thickness TSi = 30 nm, pocket length 20 nm and thickness 10 nm.

Tripathi et al. [133] proposed a junction less TFET having a single gate and a SiGe based pocket near source called JLSGTFET (Fig. 27). The device utilizes junction-less technology for ease of fabrication. Low bandgap SiGe pocket between source and channel reduces the switching capacitance of the device. Ge mole fraction x = 0.3 is used, which improves various electrical parameters like transconductance, junction capacitance and leakage current.

The device attains ION/IOFF ratio of 2 × 108, steep subthreshold slope of 52.3 mV/dec and DIBL = 2.1 mV/V at 300 K. Furthermore, the device parameters are investigated for a wide temperature range from 250 to 400 K and the variations are found to be very low, which makes it ideal for sub 20 nm, ultra-low power, digital applications. The device dimensions are, gate length Lg = 15 nm, SiGe pocket length of 5 nm, channel length of 15 nm, drain/source height of 20 nm and source/drain doping of 1 × 1020 cm−3. Kumar and Raman [134] proposed a charge plasma-based TFET using cylindrical Si nanowire. It uses drain, source and gate electrodes having specific work functions wrapped all around the intrinsic nanowire for inducing the vertical PIN structure. The 2D view of the proposed structure is shown in Fig. 28. The device is investigated for the effects of interface trap charges (ITC) at the channel dielectric interface and the associated noise behaviour is studied. It is found that the ITCs of all polarities degrade ION/IOFF ratio however positive ITCs improve drive current as well as noise behaviour. The device dimensions are, length of source/drain 100 nm, channel length of 50 nm, radius of NW = 5 nm, TOX = 2 nm, gate, source and drain work functions of 4. 5, 5. 93 and 3. 9 eV, respectively.

Buried Oxide (BOX) and Selective Buried Oxide (SELBOX) technology has been incorporated in few researches to enhance the performance of the TFETs. Bhattacharjee et al. [135] proposed a new TFET having a single gate and broken or splitted drain called SD-SG TFET as shown in Fig. 29. In the device drain doping engineering is used to create a splitted or parted drain in which one portion is highly doped and the other lightly, they are arranged in descending order of doping. The parted drain structure greatly reduces ambipolar conduction. Four devices with different relative positioning of the splitted drain (SD) are analysed and evaluated for performance. One has the entire drain bisected into high and low doping called SD SG TFET and the others have either SD at the top called TSD SG, SD at the bottom called BSD SG or SD at the middle, called MSD SG TFET. The BSD-SG TFET showed a maximum ION/IOFF ratio among all structures. All the structures showed better performance compared to conventional TFETs. The dimensions include source doping NS = 1 × 1020 cm−3, channel doping Nch = 1 × 1017 cm−3, drain doping ND1 = 5 × 1018 cm−3 and ND2 = 1 × 1017 cm−3, drain length Xd = 100 nm, source width Ys = 60 nm, channel width W = 60 nm, Tsi = 60 nm and Tox = 1 nm.

Mitra and Bhowmick [120] designed buried oxide (BOX) based TFET having the presence of gate on some portions of both source as well as channel called GOSC TFET (Fig. 30) and compared its performance with conventional FG SOI TFET and GOS SOI TFET when traps are there at all the Si to Oxide interfaces. The effects of trap charges present at the interface of gate oxide and Si and BOX & Si on subthreshold swing, drive current, ambipolarity, Cg and fT is evaluated for all three devices. The traps at the interface of BOX to Si increases ambipolar conduction while traps at the interface of gate oxide to Si reduces ON-state current, the effect of the former is observed to be much more severe. It is found that GOS SOI TFET is most immune to the adverse effects of interface traps. For the GOS TFET performances are observed to be much better with SS of 61. 5 mV/V, VT of 0. 6 V and ION of 37. 5 μm/μA. The device dimensions are, source/drain length = 30 nm, p + source (1021 cm−3), p channel (1016 cm−3), n + drain (5 × 1019 cm−3), Gate work function = 4. 2 eV, Tox = 2 nm, gate channel overlap L = 10 nm and LUN = 30 nm.

Vanlalawpuia and Bhowmick [136] proposed a TFET with L shaped buried oxide layer (BOX) with Ge source region having a very thin δ-doped layer within it (Fig. 31). The use of low bandgap Ge material for source enhances the drive current and the use of δ-doped layer reduces OFF state leakage and ambipolarity. Further the source is positioned vertically below the gate channel stack which results in vertical tunnelling current or BTBT perpendicular to the gate oxide, this results in very high ON current. The sizes and dimensions of each region are fixed after optimization using simulation software. The dimensions include the thickness of δ layer = 1 nm, LUC = 15 nm, Ge source thickness of 16 nm, tOX = 2 nm, source length of 15 nm, drain length of 10 nm and gate length of 30 nm. The source, channel, drain and δ layer doping are 1 × 1020 cm−3, 1 × 1016 cm−3, 5 × 1018 cm−3 and 5 × 1016 cm−3, respectively.

Ahn et al. [137] proposed an InGaAs based planer TFET structure having Zn diffused source and W/ZrO2/Al2O3 gate stack (Fig. 32). Narrow and direct bandgap, group III–V material InGaAs is used for the channel to enhance BTBT and hence the ON current. The mole fraction for In is optimised in such a way that a quantum well (QW) is formed which simultaneously suppresses OFF current while maintaining high ION. Zn is diffused in the source region to achieve an abrupt doping profile for high BTBT. ZrO2/Al2O3 gate stack is used to have optimum gate control over the tunnelling current while maintaining low equivalent oxide thickness (EOT). The device dimensions are optimised for high performance in low power digital circuits.

Ghosh and Bhowmick [138] proposed a TFET device mounted on a selective buried oxide (SELBOX) and having a heterogeneous junction with the presence of a thin δp+ layer of SiGe at the interface of source and channel (Fig. 33). The device is analysed with encouraging results for the impact of flicker noise due to the presence of Gaussian as well as uniform traps, which are a major concern for most TFET devices. The device uses selective BOX having a gap in place of fully depleted (FD) BOX because it reduces OFF current. It uses a low bandgap δ layer of SiGe which enhances BTBT and high k gate dielectric which improves ION. The mole fraction of the δ layer, its position as well as the position of the SELBOX gap are all optimised through simulations. The device dimensions include channel length of 30 nm, δ layer thickness of 3 nm, source/drain length of 35 nm, SELBOX thickness of 10 nm with gap length of 2 nm. The source, channel, drain and δp+ layer doping of 1 × 1020 cm−3, 1 × 1016 cm−3, 5 × 1018 cm−3 and 1 × 1018 cm−3, respectively.

Singh et al. [139] proposed a TFET on SELBOX with the partial ground plane (PGP) having a gate dielectric stack of HfO2 over SiO2 and low bandgap Ge as the source material, termed as GSHJ-PGP-STFET (Fig. 34). The device uses narrow bandgap Ge material for source to enhance BTB tunnelling. The HfO2/SiO2 stack provides for optimum gate control of the tunnelling phenomena and its combined effect with Ge source enhances ON-state current. The SELBOX structure with PGP suppresses OFF state leakage and maintains a good ION/IOFF ratio. The device is found to be much superior to conventional SELBOX TFET and FD BOX TFET in terms of average SS, ION and ION/IOFF ratio.

Cross-sectional view of GSHJ-PGP-STFET [139]

The device dimensions include channel length of 40 nm, source/drain length of 30 nm, SELBOX thickness of 10 nm with a gap width of 4 nm, high and low k gate oxide thicknesses of 2 and 1 nm, respectively. The doping concentrations of source, channel, drain, and PGP region are 1020, 1016, 5 × 1018 and 5 × 1018 cm−3, respectively.

Research is also done to apply the properties of a TFET to make a biosensor. In this direction Verma et al. [140] proposed a TFET based label-free bio-molecule sensor which utilizes vertical dielectric modulation termed as V DMTFET (Fig. 35). The previously established lateral DMTFET (L-DMTFET) is compared with performance. A heavily doped n + pocket is introduced in the device for vertical tunnelling along with lateral tunnelling which increases the ON-state current greatly and reduces subthreshold swing. A gate to source overlap is also there for improving sensitivity. There are two nanocavities in the device the larger one Lc2 = 15 nm below the front gate and Lc1 = 10 nm below the back gate for sensing biomolecules. Filled cavities give higher sensitivities, gate metal M1 (ФM1 = 4. 3 eV) is used near drain end and M2 (ФM2 = 3.8 eV) near source end to enhance the sensitivities. The device dimensions are, length of channel Lch = 42 nm, lengths of the source and drain Ls = Ld = 20 nm, body thickness tSi = 10 nm, oxide tox = 6 nm and cavity thickness tcavity = 5 nm. Doping of source, channel and drain is 5 × 1019, 1 × 1012, and 5 × 1018 cm−3 respectively and n + pocket doping is 5 × 1019 cm−3.

10 Comparison of existing TFET architectures

A detailed parametric analysis along with applications of promising TFET configurations are presented in Table 15. The SD-SG TFET [135] shows the highest ON state current due to its drain doping engineering and splitted drain architecture. Its drain consists of a stack of highly doped region above a lightly doped region, which increases the tunnelling width of the drain channel interface and increases the drive current and reduces ambipolar leakage. Further when the relative position of the splitted drain is varied for channel maximum ON-current and ION/IOFF ratio is found when it is at the bottom. The VS-TFET [127] promises to show the minimum sub-threshold slope of 17 mV/dec but its feature size is very large which will hamper the packing density. It has a vertical structure with channel above and on the sides of the source and a dual gate which controls both lateral and transverse tunnelling, which reduces the SS, but the structure has the drawback of least ION/IOFF ratio. The HM-GUL-ED-TFET [131] has an SS of 19.13 mV/dec and ION/IOFF ratio of 2.73 × 1011 at 30 nm technology node. It is found to be one of the promising candidates for ultra-low power portable devices for analog/RF applications. The device uses gate underlap towards drain side to suppress the ambipolar leakage, gate leakage and low bandgap material for source which enhances band to band tunnelling (BTBT) and hence ON current. Thus, as a combined effect the ION/IOFF ratio is boasted, and SS made steeper. Further the device uses charge plasma-based electrical doping which reduces fabrication complexity and junction leakage. The V-DMTFET [140] shows good results as TFET based label-free biomolecule sensor which senses specific biomolecules based on the relative change in the dielectric constant of the sensing cavities due to the presence of target biomolecules (known dielectric constant). It shows SS of 47 mV/dec and good ION/IOFF ratio. The JLSGTFET [133] has the lowest value of drain induced barrier lowering (DIBL) of only 2.1 mV/V and reasonable other performance parameters like SS, ION and ION/IOFF at 15 nm technology node. It uses junction less technology with a p + Si0. 7Ge0. 3 pocket between the n+ source and n− channel which drastically improves the performance parameters.

A comparison of analog/RF performance parameters of some of the most efficient devices is represented in Table 16. The SiGe-S-NW-TFET [121] shows the highest cut-off frequency and GBP of 950 GHz and 549 GHz respectively. It uses Si nanowire technology with narrow bandgap SiGe material for source and hetero gate dielectric with high-k HfO2 near source end for performance improvement. It also exhibits the lowest transit time of 0.9 ps. The GDO– HD–GAA-TFET [123] with gate-drain overlap, heterogenous gate dielectric and cylindrical gate all around structure has the highest value of transconductance of 0.53 mS.

The device offers high ON current and good gate control along with reduced ambipolarity, but it has low cut-off frequency and poor transit time response. The JL-TFET [132] using junction less technology along with low bandgap SiGe pocket near source exhibits moderate transconductance of 0.1mS and fT of 100 GHz. Cut of the frequency of 130 GHz is obtained by D GAA CS NT TFET [129] with its cylindrical core–shell dual-gate all around structure, but its transconductance is not up to the mark, further its complex structure and fabrication complexity does not justify the performance improvement. The HM-GUL-ED-TFET [131] also shows good fT and moderate gain-bandwidth product. It uses charge plasma-based electrical doping which eases fabrication and reduces leakage.

11 Conclusion

In the proposed research, the hybrid variants of chimp optimizer has been successfully developed, which are based on wholesome attitude roused by amazing thinking and hunting ability with sensual movement for finding optimal solution in global search region. The newly developed improved variant of Chimp optimizer has been successfully tested for various engineering design and standard benchmark optimization problems, which includes unimodal, multi-modal and fixed dimensions benchmark problems. After validating the efficiency of the proposed optimizers for standard benchmarks and engineering design problems, it has been experimentally observed that both the variants are competitive foe finding the solution within the global search space. Based on experimental results and comparative analysis with other methodologies, it has been recommended that the proposed hybrid variants can be universally accepted to solve any of the hard engineering design challenges in global search space. The chimp optimizer is found most suitable to optimize TFET structure in terms of dimension and performance parameters that can be a worthiest replacement candidate of MOSFET in ultra-low power, highly scaled down (high packing density) VLSI circuits. The paper also gives a comprehensive review of the recent advances in TFET technology employing geometrical modifications, gate metal work function engineering, hetero source/channel/drain material with bandgap engineering, multigate, gate dielectric engineering, junction-less techniques etc. for improvement of performance parameters like steep SS, low ambipolarity, high drive current and ION/IOFF ratio. It also analyses the devices based on different analog/RF performance parameters like transconductance, cut-off frequency, GBP, and transit time to suggest the most promising device configuration. Further, it investigates the devices from an application point of view like low power battery operated devices, digital, analog/RF circuits, and biomolecule sensors. The VS-TFET has least SS but low ION/IOFF ratio and large feature size which restricts its applications. At 50 nm node, the SD SG TFET shows the highest ON current and ION/IOFF ratio due to its splitted drain and relative positioning of drain, which enhances high BTBT and low leakage. The HM-GUL-ED-TFET has the best performance features at 30 nm node and boasts electrical doping for ease of manufacture. The JLSGTFET has the least DIBL and good overall performance at 15 nm. In RF analysis, the SiGe-S-NW-TFET exhibits the most superior ac performance with highest fT and GBP of 950 and 549 GHz respectively and with a low transit time of only 0. 9 ps. The GDO-HD-GAA-TFET shows the highest value for gm of 0.53 mS. So, a narrow band-gap vertical TFET with junction less properties for sub 20 nm technology is found to be the most promising TFET configuration for future low power analog/RF and some digital applications. Also, a V-DMTFET is found to be good as a biosensor with a low SS of 47 mV/dec at 42 nm feature size.

Availability of data and material

The associated data will be made available on request.

References

Abbassi R, Abbassi A, Heidari AA, Mirjalili S (2019) An efficient salp swarm-inspired algorithm for parameters identification of photovoltaic cell models. Energy Convers Manag 179(January):362–372. https://doi.org/10.1016/j.enconman.2018.10.069

Faris H et al (2019) An intelligent system for spam detection and identification of the most relevant features based on evolutionary random weight networks. Inf Fusion 48(August):67–83. https://doi.org/10.1016/j.inffus.2018.08.002

(2000) Rapid communications. JAIDS J Acquir Immune Defic Syndr 23(5):374. https://doi.org/10.1097/00126334-200004150-00002

Wu G (2016) Across neighborhood search for numerical optimization. Inf Sci (Ny) 329(61563016):597–618. https://doi.org/10.1016/j.ins.2015.09.051

Wu G, Pedrycz W, Suganthan PN, Mallipeddi R (2015) A variable reduction strategy for evolutionary algorithms handling equality constraints. Appl Soft Comput J 37:774–786. https://doi.org/10.1016/j.asoc.2015.09.007

Khishe M, Mosavi MR (2020) Chimp optimization algorithm. Expert Syst Appl 149:113338. https://doi.org/10.1016/j.eswa.2020.113338

Bhattacharya A, Chattopadhyay PK (2010) Solving complex economic load dispatch problems using biogeography-based optimization. Expert Syst Appl 37(5):3605–3615. https://doi.org/10.1016/j.eswa.2009.10.031

Hemamalini S, Simon SP (2011) Dynamic economic dispatch using artificial immune system for units with valve-point effect. Int J Electr Power Energy Syst 33(4):868–874. https://doi.org/10.1016/j.ijepes.2010.12.017

Noman N, Iba H (2008) Differential evolution for economic load dispatch problems. Electr Power Syst Res 78(8):1322–1331. https://doi.org/10.1016/j.epsr.2007.11.007

Yalcinoz T, Altun H, Uzam M (2001) Economic dispatch solution using a genetic algorithm based on arithmetic crossover. In: 2001 IEEE Porto Power Tech Proc., vol 2, no 4, pp 153–156. https://doi.org/10.1109/PTC.2001.964734

Nguyen TT, Vo DN (2015) The application of one rank cuckoo search algorithm for solving economic load dispatch problems. Appl Soft Comput J 37:763–773. https://doi.org/10.1016/j.asoc.2015.09.010

Swain RK, Sahu NC, Hota PK (2012) Gravitational search algorithm for optimal economic dispatch. Proc Technol 6:411–419. https://doi.org/10.1016/j.protcy.2012.10.049

Abdelaziz AY, Ali ES, Abd Elazim SM (2016) Implementation of flower pollination algorithm for solving economic load dispatch and combined economic emission dispatch problems in power systems. Energy 101:506–518. https://doi.org/10.1016/j.energy.2016.02.041

Bhattacharjee K, Bhattacharya A, Dey SHN (2014) Chemical reaction optimisation for different economic dispatch problems. IET Gener Transm Distrib 8(3):530–541. https://doi.org/10.1049/iet-gtd.2013.0122

Yang X, Soheil S, Hosseini S, Hossein A (2012) Firefly algorithm for solving non-convex economic dispatch problems with valve loading effect. Appl Soft Comput J 12(3):1180–1186. https://doi.org/10.1016/j.asoc.2011.09.017

Aragón VS, Esquivel SC, Coello Coello CA (2015) An immune algorithm with power redistribution for solving economic dispatch problems. Inf Sci (Ny) 295:609–632. https://doi.org/10.1016/J.INS.2014.10.026

Banerjee S, Maity D, Chanda CK (2015) Teaching learning based optimization for economic load dispatch problem considering valve point loading effect. Int J Electr Power Energy Syst 73:456–464. https://doi.org/10.1016/J.IJEPES.2015.05.036

Victoire TAA, Jeyakumar AE (2004) Hybrid PSO–SQP for economic dispatch with valve-point effect. Electr Power Syst Res 71(1):51–59. https://doi.org/10.1016/J.EPSR.2003.12.017

Pradhan M, Roy PK, Pal T (2018) Oppositional based grey wolf optimization algorithm for economic dispatch problem of power system. Ain Shams Eng J 9(4):2015–2025. https://doi.org/10.1016/j.asej.2016.08.023

Yu JJQ, Li VOK (2016) A social spider algorithm for solving the non-convex economic load dispatch problem. Neurocomputing 171:955–965. https://doi.org/10.1016/j.neucom.2015.07.037

Kavousi-Fard A, Khosravi A (2016) An intelligent θ-modified bat algorithm to solve the non-convex economic dispatch problem considering practical constraints. Int J Electr Power Energy Syst 82:189–196. https://doi.org/10.1016/j.ijepes.2016.03.017

Whitley D (2001) An overview of evolutionary algorithms: practical issues and common pitfalls. Inf Softw Technol 43(14):817–831. https://doi.org/10.1016/S0950-5849(01)00188-4

Calvet L, De Armas J, Masip D, Juan AA (2017) Learnheuristics: hybridizing metaheuristics with machine learning for optimization with dynamic inputs. Open Math 15(1):261–280. https://doi.org/10.1515/math-2017-0029

Heidari AA, Mirjalili S, Faris H, Aljarah I, Mafarja M, Chen H (2019) Harris hawks optimization: algorithm and applications. Futur Gener Comput Syst 97:849–872. https://doi.org/10.1016/j.future.2019.02.028

Rao RV, Savsani VJ, Vakharia DP (2012) Teaching-learning-based optimization: an optimization method for continuous non-linear large scale problems. Inf Sci (Ny) 183(1):1–15. https://doi.org/10.1016/j.ins.2011.08.006

Hansen P, Mladenović N, Moreno-Pérez JA (2010) Variable neighbourhood search: methods and applications. Ann Oper Res 175(1):367–407. https://doi.org/10.1007/s10479-009-0657-6

Doʇan B, Ölmez T (2015) A new metaheuristic for numerical function optimization: Vortex Search algorithm. Inf Sci (Ny) 293(August):125–145. https://doi.org/10.1016/j.ins.2014.08.053

Takeang C, Aurasopon A (2019) Multiple of hybrid lambda iteration and simulated annealing algorithm to solve economic dispatch problem with ramp rate limit and prohibited operating zones. J Electr Eng Technol 14(1):111–120. https://doi.org/10.1007/s42835-018-00001-z

Naama B, Bouzeboudja H, Allali A (2013) Solving the economic dispatch problem by using Tabu Search algorithm. Energy Procedia 36:694–701. https://doi.org/10.1016/j.egypro.2013.07.080

Yao X, Liu Y, Lin G (1999) Evolutionary programming made faster. IEEE Trans Evolut Comput 3(2):82–102

Geem ZW, Kim JH, Loganathan GV (2001) A new heuristic optimization algorithm: harmony search. SIMULATION 76(2):60–68. https://doi.org/10.1177/003754970107600201

Ghaemi M, Feizi-Derakhshi MR (2014) Forest optimization algorithm 41(15):6676-6687

Mirjalili S, Mirjalili SM, Lewis A (2014) Grey wolf optimizer. Adv Eng Softw 69:46–61. https://doi.org/10.1016/j.advengsoft.2013.12.007

Mirjalili S (2015) Moth-flame optimization algorithm: a novel nature-inspired heuristic paradigm. Knowl-Based Syst 89:228–249. https://doi.org/10.1016/j.knosys.2015.07.006

Salimi H (2015) Stochastic fractal search: a powerful metaheuristic algorithm. Knowl-Based Syst 75:1–18. https://doi.org/10.1016/j.knosys.2014.07.025

Nematollahi AF, Rahiminejad A, Vahidi B (2017) A novel physical based meta-heuristic optimization method known as lightning attachment procedure optimization. Appl Soft Comput J 59:596–621. https://doi.org/10.1016/j.asoc.2017.06.033

Storn R, Price K (1997) Differential evolution—a simple and efficient heuristic for global optimization over continuous spaces. J Glob Optim. https://doi.org/10.1023/A:1008202821328

C. Verma, Z. Illés, V. Stoffová and P. K. Singh Predicting Attitude of Indian Student’s Towards ICT and Mobile Technology for Real-Time: Preliminary Results IEEE Access, 8:178022-178033. doi: 10.1109/ACCESS.2020.3026934.

Biswas A, Mishra KK, Tiwari S, Misra AK (2013) Physics-inspired optimization algorithms: a survey. J Optim 2013:1–16. https://doi.org/10.1155/2013/438152

Liu Y, Li R (2020) PSA: a photon search algorithm. J Inf Process Syst 16(2):478–493

Erol OK, Eksin I (2006) A new optimization method: big bang-big crunch. Adv Eng Softw 37(2):106–111. https://doi.org/10.1016/j.advengsoft.2005.04.005

Mosavi MR, Khishe M, Naseri MJ, Parvizi GR, Ayat M (2019) Multi-layer perceptron neural network utilizing adaptive best-mass gravitational search algorithm to classify sonar dataset. Arch Acoust 44(1):137–151. https://doi.org/10.24425/aoa.2019.126360

C. Verma, V. Stoffová, Z. Illés, S. Tanwar and N. Kumar (2020) Machine Learning-Based Student’s Native Place Identification for Real-Time IEEE Access, 8:130840-130854. doi: 10.1109/ACCESS.2020.3008830.