Abstract

Temperature-dependent current-voltage \(\left( {I - V} \right) \), and frequency dependent capacitance-voltage \(\left( {C - V} \right) \) and conductance-voltage \(\left( {G - V} \right) \) measurements were performed in order to analyze characteristics of CdZnTe/Si structure. Obtained profiles enable us to understand the different characteristics of the diode structure such as the carrier conduction mechanism and the nature of the interfacial layer. Over the temperature range between 220 and 340 K, taking consideration of the disparity in the forward-biased current, the diode parameters such as saturation current \(\left( {I_{0} } \right)\), zero-bias barrier height (\({{\Phi}}_{B0}\)) and ideality factor \(\left(n\right)\) have been obtained. The barrier height increased (0.53 to 0.80 eV) while the ideality factor decreased (4.63 to 2.79) with increasing temperature from 220 to 340 K, indicating an improvement in the junction characteristics at high temperatures. Due to the inhomogeneity in barrier height, the conduction mechanism was investigated by Gaussian distribution analysis. Hence, the mean zero-bias barrier height (\({\overline{\Phi}}_{B0}\)) and zero-bias standard deviation (\({\sigma }_{0}\)) were calculated as 1.31 eV and 0.18, respectively. Moreover, for holes in p-type Si, Richardson constant was found to be 32.09 A cm−2 K−2 via modified Richardson plot. Using the capacitance-voltage \(\left( {C - V} \right) \) and conductance-voltage \(\left( {G - V} \right) \) characteristics, series resistance \(({R}_{s})\) and density of interfacial traps \(({D}_{it})\) have been also investigated in detail. A decreasing trend for \({R}_{s}\) and Dit profiles with increasing frequency was observed due to the impurities at the CdZnTe/Si interface and interfacial layer between the front metal contact and CdZnTe film.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

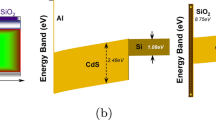

Cadmium Zinc Telluride (CdZnTe) is a ternary II-VI semiconductor material with a high atomic number which provides strong absorption [1, 2]. It also has excellent optoelectronic properties and low leakage current due to its wide bandgap properties. CdZnTe is used in many important applications, such as solar cells [3], photodiodes [4], photoconductors [5], room temperature gamma-ray [6], X-ray detectors [7], infrared windows [8] and light-emitting diodes [9]. In this study, a detailed analysis of electrical properties of the CdZnTe/Si structure has been examined and it has been observed that Si semiconductor material could be a suitable heterojunction partner. The reasoning behind the production of CdZnTe/Si diode is the fact that the properties of Si material are very well-known which assists the evaluation of the electrical response of the film in the junction.

National Renewable Energy Laboratory (NREL) and EPIR Technologies conducted studies to develop CdZnTe-based top cells grown on p-Si solar cells as a platform to manufacture high-efficiency tandem cells [10]. Additionally, CdZnTe thin films deposited on Si substrates by molecular-beam epitaxy (MBE) have been studied to facilitate the production of HgCdTe IR detectors [11]. MOVPE growth of thick single crystal CdZnTe epitaxial layers on Si substrates were also studied for nuclear radiation detection applications [12]. In accordance with the corresponding studies, it was necessary to examine the electrical properties of the thermally evaporated CdZnTe/Si diode in a wide range of temperatures and frequencies for possible future applications. Therefore, we have conducted temperature-dependent current-voltage (I–V), frequency-dependent capacitance-voltage \(\left( {C - V} \right) \)and conductance-voltage \(\left( {G - V} \right) \)measurements under dark conditions. Temperature-dependent \(\left( {I - V} \right) \) measurements were performed to analyze the dominant conduction mechanisms through the junction and to determine the main diode parameters. In addition, frequency-dependent \(\left( {C - V} \right) \) and \(\left( {G - V} \right) \)measurements have been conducted to investigate junction properties and to understand the effect of the deep levels on the capacitance. Long-lived traps which are important to identify the physical processes in the diode, the relation between the formation of deep traps and possible degradation mechanisms were explored by extended range of frequencies [13].

2 Experimental details

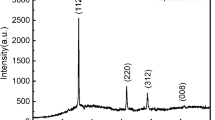

CdZnTe/p-Si diode structure was prepared on p-type Si substrate having \((100)\) orientation and l Ω∙cm bulk resistivity with 2 × 1017 cm−3 doping concentration. The RCA-cleaned substrate was etched in a 10% HF solution for 10 s immediately before loading into the deposition chamber. Al back contact was thermally evaporated and annealed at 450 °C under the continuous N2 flow to enhance the ohmicity of Al-contact. Then, CdZnTe layer was deposited by thermal evaporation method with a chamber pressure of 1 × 10−6 mbar at room temperature. The CdZnTe crystal pieces, which is used as a source material, were obtained from the ingots produced by Vertical Gradient Freeze (VGF) method in METU-CGL (Crystal Growth Laboratory) with the purity of 99.999% [14]. The rate of evaporation and film thickness were monitored and controlled by InficonXTM/2 quartz crystal monitor and CdZnTe film was deposited with a 5 Å/s evaporation rate and the final film thickness of this layer was measured as ~ 750 nm by Dektak 6 M profilometer. Deposited CdZnTe/p-Si was dipped into a solution of 2.1 g CdCl2 in 100 ml methanol and annealed for 15 min at 300 °C under N2 atmosphere prior to Au front contact formation. CdCl2 treatment is a critical step to improve device performance. Then, 100 nm thick Au front contact was deposited using electron-beam evaporation and the fabricated structure was annealed at 100 °C to enhance the adhesion of the contacts to the film surface. The schematic cross-section of the Au/CdZnTe/p-Si/Al diode structure is shown in Fig. 1.

The temperature-dependent I–V measurements were performed using Keithley 2401 source-meter for the bias voltage of ± 3 V in the temperature range of 220–340 K. For these measurements, a CTI-Cryogenics Model 22 refrigerator system combined with Model SC helium generator was used, and the temperature on the diode was adjusted using a Lakeshore DRC-91C controller. Additionally, the room temperature \(\left( {C - V} \right) \) and

\(\left( {G - V} \right) \)measurements were carried out in a wide frequency range from 1 kHz to 1 MHz using computer-controlled Hewlett Packard 4192A LF model impedance analyzer.

3 Result and discussion

3.1 Temperature-dependent current–voltage analysis

Temperature-dependent \(\left( {I - V} \right) \) measurements were performed to determine the dominant conduction mechanisms and obtain the main diode parameters. Zero-bias barrier height (ϕB0) and ideality factor (\(n\)) are the two important parameters determined from \(\left( {I - V} \right) \) plots using thermionic emission (TE) theory. According to the diode equation [15], the forward-biased current can be modeled as;

where \({I}_{0}\) is the reverse-saturation current, \(q\) is the electronic charge, \(V\) is the voltage value in the forward bias region, \(n\) is the ideality factor, \(k\) is the Boltzmann constant and \(T\) is the ambient temperature. Figure 2 shows the \(\left( {I - V} \right) \) characteristics of CdZnTe/Si diode structure at various ambient temperatures. According to the measurement results, the forward current is higher than the reverse-biased current for all temperature values.

Intercepts of the \(\left( {I - V} \right) \) plot with the current axis give the value of the I0 values at any given temperature. I0 value was used to estimate the ϕB0 values using the relation

where \(A^*\) is the effective Richardson constant and \(A\) s the device area. \(A^*\) value for p-type Si was used as 32 Acm−2 k2 under the assumption of uniform barrier height formation in the diode [15]. The obtained \(n\), \({I}_{0}\), and \({\Phi}_{B0}\) values for each temperature are tabulated in Table 1.

As stated in Table 1, the increase in \({\Phi}_{B0}\) and decrease in \(n\) with increasing temperature indicates an improvement in the junction [16]. The increase in \({\Phi}_{B0}\) with temperature provides smaller leakage current and therefore an increase in the rectification behavior. However, at lower temperatures, the ideality factor much greater than unity results in deterioration of the device parameters [17]. Because of the observed temperature dependency in the analysis, the current transport at low temperatures was controlled by the current flowing across the patches of low barrier heights, resulting in a higher \(n\) value [18]. An apparent increase in the n and a decrease in the barrier height at low temperatures are probably caused by inhomogeneous barrier formation from low barrier patches [19]. However, TE theory is based on homogeneous barrier height formation in the junction. Considering the inhomogeneous barrier height formation and deviation from TE theory, Gaussian distribution (GD) of barrier height was studied based on a mean value \(\bar{\Phi}_{B0}\) with the standard deviation of \({\sigma }_{0}\) to explain the carrier transport mechanism across the junction [20,21,22,23]. This approximation has been achieved by determining the degree of barrier height variation under the Tung’s theoretical approach [24] and a good linear relationship between \({\Phi}_{B0}\) and \(n\) was obtained in Fig. 3. In Tung’s model, bias and temperature dependent diode parameters extracted from bias and temperature independent patch parameters [24].

GD model was used to describe the potential fluctuations considering a continuous barrier distribution at the interface. Using the GD model, the total current is expressed as a sum of the current flows in all individual barrier patches [25]. Therefore, the total junction current dominated by low barrier patches is given as:

with modified reverse saturation current,

where \({n}_{ap}\) and \({\Phi}_{ap}\) are the apparent ideality factor and apparent barrier height, respectively. Using GD function, \({\Phi}_{ap}\) can be expressed as the temperature variation in \({\Phi}_{B0}\):

As represented in Fig. 4(a), \({\Phi}_{B0}\) has a linear relation with \(q/2kT\) and from the analysis of intercept and slope, \(\bar{\Phi}_{B0}\) and \({\sigma }_{0}\) have been determined, respectively. The value of \({\sigma }_{0}\) was found to be 0.18 while the \(\bar{\Phi}_{B0}\) value was obtained as 1.31 eV. In the GD model, \({\sigma }_{0}\), which is a measure of the barrier homogeneity, shows 14% deviation from the mean value \(\bar{\Phi}_{B0}\). According to the obtained values, the forward-biased current mechanism in CdZnTe/Si diode conforms to a junction with GD of barrier height due to inhomogeneity of the interface layer and non-uniformity of interface charges. According to the GD model, \({\rho }_{2}\) and \({\rho }_{3}\), the coefficients indicating the voltage deformation of the barrier height distribution can be extracted from the following equation

While Eq. 6 examines the relation between temperature and \(n\), Fig. 4(b) shows the corresponding voltage deformation of the GD of the barrier height with respect to \(n\). The voltage coefficients were determined from the intercept and slope of the straight line as, \({\rho }_{2}\) = 0.0153 V and \({\rho }_{3}\) = 0.387, respectively.

Finally, modified Richardson constant \({A}^{*}\) was calculated for GD type inhomogeneous barrier height. Using Eq. 3, modified \({A}^{*}\) can be determined as

The modified Richardson plot using Eq. 7 was given in Fig. 5. The \({\overline{\Phi}}_{B0}\) and \({A}^{*}\) values were found as 1.32 eV and 32.095 Acm−2 k−2 from the slope and intercept of the

\(ln[\left({I}_{0}/{T}^{2}\right)-\left({q}^{2}{\sigma }_{0}^{2}\right)/\left(2{k}^{2}{T}^{2}\right)]\) vs. \(q/kT\) plot, respectively. The value of \({\overline{\Phi}}_{B0}\) obtained using Eqs. 4 and 7, were found to be very similar. Even the inhomogeneity of the barrier height exists in the diode, the modified \({A}^{*}\) value was in accordance with the reported values [26].

3.2 Frequency-dependent capacitance–voltage analysis

In this study, the frequency dependence of the forward and reverse bias \( \left( {I - V} \right) \) and \( \left( {G - V} \right) \) characteristics of Au/CdZnTe/p-Si/Al diode structure have been investigated in the frequency range of 1 kHz – 1 MHz and voltage range of \(\pm\) 3 V at room temperature.

As can be seen in Fig. 6a, b, capacitance and conductance of the diode show sensitivity to applied voltage and frequency. Capacitance values are decreasing while conductance increases with increasing frequency. The obtained higher values of capacitance at low frequencies in Fig. 6a can be attributed to the carrier charges at surface traps and their relaxation time, since they can easily follow the ac signal and yield an excess in the measured capacitance [27]. The capacitance at high frequency represents the response of free carriers, while capacitance at low frequency represents the response of not only free carriers but also deep trap levels [27,28,29]. Significant amount of deep trap levels may co-exist with the shallow levels and contribute noticeably to the space charge [30]. This is because the CdZnTe film may be non-intentionally doped which suggests that the free carriers are due to the defects. These defects may be intrinsic to the polycrystalline CdZnTe or due to extrinsic impurities such as Cl resulting from CdCl2 treatment [31]. Ideally, the \( \left( {C - V} \right) \) and \( \left( {G - V} \right) \) characteristics are expected to be independent of frequency. Several mechanisms can give rise to a frequency dependent capacitance and conductance such as, Schottky barrier behavior, deep traps in CdZnTe, Cl diffusion, the front contact, interface traps and high series resistance [32, 33].

Additionally, \({R}_{s}\) (series resistance) and \({D}_{it}\) (Density of interface traps) are important parameters that significantly change both the \( \left( {C - V} \right) \) and \( \left( {G - V} \right) \) characteristics from ideal cases [32]. \({R}_{s}\) parameter is effective in the forward bias region for high frequencies, while \({D}_{it}\) is effective at low frequencies.

3.2.1 Series resistance (\({\mathbf{R}}_{\mathbf{s}}\))

It should be noted that the value of series resistance can affect both capacitance and conductance characteristics. The value of voltage-dependent resistance \({R}_{i}\) can be extracted in the total measured range as

where \(\omega\)\((2\pi f)\) is the angular frequency and \({C}_{m}\) and \({G}_{m}\) are the measured capacitance and conductance values for any voltage. Although this approach evaluates the effects of parasitic resistance in the total measured range, at sufficiently high frequencies \((f\ge 300 kHz)\) and in the positive voltage region, it can be used to calculate the \({R}_{s}\) values [22, 23, 32].

The applied bias voltage and frequency dependence profile of the \({R}_{s}\) were evaluated according to Eq. 8 for high frequencies, and its characteristic behavior is presented in Fig. 7. As shown in the figure, the value of \({R}_{s}\) increased with decreasing frequencies due to the impurities at CdZnTe/Si interface layer, front metal contact, and CdZnTe layer.

3.2.2 The density of interface traps \({(\mathbf{D}}_{\mathbf{i}\mathbf{t}}\))

\({D}_{it}\) can be attributed to the periodic lattice structure at the surface, surface preparation, interfacial layer, and impurities in the semiconductor. Hill-Coleman approximation technique is a quantitative method to obtain the density of interface traps [34]. According to this approximation, frequency-dependent \( \left( {C - V} \right) \) and corresponding \(G/w-V\) plots are required for the estimation of \({D}_{it}\). As a result, frequency dependence distribution of \({D}_{it}\) can be determined as [35];

where \(q\) is the elementary charge, \(A\) is the diode area, \({G}_{m}/w\) is the max-peak value of the measured conductance as shown in Fig. 8(a), \({C}_{m}\) is the corresponding measured capacitance value and \({C}_{i}\) is the interfacial capacitance.

The conductance can be considered as a measure of the interface trap density. It indicates loss mechanisms resulting from the capture of interface traps and emission of carriers [36]. To determine the distribution of density of interface trap, \(G/w\) was calculated using each \( \left( {C - V} \right) \) and \( \left( {G - V} \right) \) plots at several modulation frequencies. \(G/w-V\) is then plotted to extract the maximum value of \(G/w\) at each frequency which in turn gives rise to \({D}_{it}\).

The frequency distribution of the calculated \({D}_{it}\) values is given in Fig. 8(b) and the profile of the \({D}_{it}\) shows a decreasing behavior when the applied frequency increased. When interface traps exist at the interface, the device behavior deteriorated due to these traps and their lifetime [36]. At low frequencies, the interface traps can follow the ac signal and cause an increase in calculated \({D}_{it}\). Nevertheless, the interface traps at high frequencies cannot follow an ac signal [34].

4 Conclusion

In this study, the electrical properties of the CdZnTe/p-Si structure were investigated using temperature-dependent \( \left( {I - V} \right) \) and frequency-dependent \( \left( {C - V} \right) \) and \( \left( {G - V} \right) \) profiles. These profiles allowed us to understand the carrier conduction mechanism and the nature of the interfacial layer of the CdZnTe/p-Si structure. \( \left( {I - V} \right) \) analysis indicated that the junction behavior showed good rectification. Hence, Si material can be considered as a suitable heterojunction partner to CdZnTe. Due to the inhomogeneity of the barrier height, as the temperature of the ambient increased, \(n\) value of the diode decreased while \({\Phi}_{B0}\) was increasing. It has been confirmed that the inhomogeneity of the barrier height had a Gaussian Distribution behavior with \({\overline{\Phi}}_{B0}\) and \({\sigma }_{0}\) as 1.31 eV and 0.18, respectively. Additionally, using a modified Richardson plot, modified \({A}^{*}\) was calculated as 32.09 A cm−2 K−2 which was approximately the same as the theoretical value for p-Si. Moreover, capacitance results showed sensitivity to frequency and decreased with increasing frequency. \({R}_{s}\) value was observed to be more effective on the impedance measurements at high frequencies in the forward bias region while \({D}_{it}\) was effective at low frequencies. Such non-uniformity in CdZnTe/Si structure was expected due to the diffusion mechanism of the extrinsic impurities such as Cl and the distribution of deep level traps from the complex nature of CdZnTe deposition and processing.

References

D. Bonnet, P. Meyers, J. Mater. Res. 13, 2740 (1998)

L. Kosyachenko, in Sol. Energy, edited by Radu D. Rugescu (IntechOpen, 2010).

A. Rohatgi, R. Sudharsanan, S.A. Ringel, M.H. MacDougal, Sol. Cells 30, 109 (1991)

S. Chusnutdinow, V.P. Makhniy, T. Wojtowicz, G. Karczewski, Acta Phys. Pol. A 122, 1077 (2012)

Y. Zhang, L. Wang, R. Xu, J. Huang, J. Tao, H. Meng, J. Zhang, J. Min, Appl. Surf. Sci. 388, 589 (2016)

A. E. Bolotnikov, S. Babalola, G. S. Camarda, Y. Cui, S. U. Egarievwe, A. Hossain, G. Yang, and R. B. James, (2009).

T.E. Schlesinger, J.E. Toney, H. Yoon, E.Y. Lee, B.A. Brunett, L. Franks, R.B. James, Mater. Sci. Eng. R Reports 32, 103 (2001)

D.S. Hobbs, B.D. MacLeod, Wind. Dome Technol. Mater. IX 5786, 349 (2005)

P. Bouchut, J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 9, 1794 (1991)

M. Carmody and A. Gilmore, NREL Subcontract Rep. 1 (2011).

T.J. de Lyon, J. Electrochem. Soc. 141, 2888 (1994)

M. Niraula, K. Yasuda, S. Namba, T. Kondo, S. Muramatsu, Y. Wajima, H. Yamashita, Y. Agata, I.E.E.E. Trans, Nucl. Sci. 60, 2859 (2013)

D. Grecu, U. Jayamaha, G. Rich, and V. G. Karpov, Conf. Rec. IEEE Photovolt. Spec. Conf. 680 (2000).

Ö. B. Balbasi, Y. Ergunt, C. Dogru, M. Ünal, M. P. Kabukcuoglu, M. Parlak, and R. Turan, in Proc. SPIE 10762, Hard X-Ray, Gamma-Ray, Neutron Detect. Phys. XX, 107620R (San Diego, California, 2018), p. 29.

S.M. Sze, D.C. Mattis, Phys. Today 23, 75 (1970)

S.S. Hegedus, W.N. Shafarman, Prog. Photovoltaics Res. Appl. 12, 155 (2004)

A.A. Ojo, W.M. Cranton, I.M. Dharmadasa, Next Generation Multilayer Graded Bandgap Solar Cells (Springer, Cham, Switzerland, 2019)

F.E. Jones, B.P. Wood, J.A. Myers, C. Daniels-Hafer, M.C. Lonergan, J. Appl. Phys. 86, 6431 (1999)

Ş. Aydoǧan, M. Saǧlam, A. Türüt, Appl. Surf. Sci. 250, 43 (2005)

C. Bozkaplan, A. Tombak, M.F. Genişel, Y.S. Ocak, K. Akkilic, Mater. Sci. Semicond. Process. 58, 34 (2017)

M. Terlemezoglu, O. Bayrakli, H.H. Güllü, T. Çolakoğlu, D.E. Yildiz, M. Parlak, J. Mater. Sci. Mater. Electron. 29, 5264 (2018)

H.H. Güllü, M. Terlemezoǧlu, O. Bayrakli, D.E. Yildiz, M. Parlak, Can. J. Phys. 96, 816 (2018)

O.B. Sürücü, H.H. Güllü, M. Terlemezoglu, D.E. Yildiz, M. Parlak, Phys. B Condens. Matter 570, 246 (2019)

R.T. Tung, Mater. Sci. Eng. R Reports 35, 1 (2001)

R.T. Tung, Phys. Rev. B 45, 13509 (1992)

R.C. Neville, J.J. Loferski, Phys. Today 35, 65 (1982)

Y. Badali, Ş. Altındal, İ. Uslu, Prog. Nat. Sci. Mater. Int. 28, 325 (2018)

M. J. Deen and F. Pascal, Springer Handbooks 1 (2017).

L.C. Kimerling, J. Appl. Phys. 45, 1839 (1974)

J.V. Li, A.F. Halverson, O.V. Sulima, S. Bansal, J.M. Burst, T.M. Barnes, T.A. Gessert, D.H. Levi, Sol. Energy Mater. Sol. Cells 100, 126 (2012)

J.S. Park, S. Kim, Z. Xie, A. Walsh, Nat. Rev. Mater. 3, 194 (2018)

Ş. Altindal, A. Tataroǧlu, I. Dökme, Sol. Energy Mater. Sol. Cells 85, 345 (2005)

J. Poortmans and V. Arkhipov, Thin Film Solar Cells Fabrication, Characterization and Applications (John Wiley and Sons, 2006).

Dieter K. Schroder, Semiconductor Material and Device Characterization, Third Edition (John Wiley & Sons, 2005).

W.A. Hill, C.C. Coleman, Solid. State. Electron. 23, 987 (1980)

R. Engel-Herbert, Y. Hwang, and S. Stemmer, J. Appl. Phys. 108, (2010).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interests regarding the publication of this manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Balbasi, C.D., Terlemezoglu, M., Gullu, H.H. et al. Electrical characterization of CdZnTe/Si diode structure. Appl. Phys. A 126, 614 (2020). https://doi.org/10.1007/s00339-020-03772-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-03772-3