Abstract

The temperature and carrier-trapping effects on the electrical characteristics of a 4H silicon carbide (4H-SiC) metal–oxide–semiconductor field effect transistor (MOSFET) dimensioned for a low breakdown voltage (BVDS) are investigated. Firstly, the impact of the temperature is evaluated referring to a fresh device (defects-free). In particular, the threshold voltage (Vth), channel mobility (µch), and on-state resistance (RON) are calculated in the temperature range of 300 K to 500 K starting from the device current–voltage characteristics. A defective MOSFET is then considered. A combined model of defect energy levels inside the 4H-SiC bandgap (deep and tail centers) and oxide-fixed traps is taken into account referring to literature data. The simulation results show that the SiO2/4H-SiC interface traps act to increase RON, reduce µch, and increase the sensitivity of Vth with temperature. In more detail, the deep-level traps in the mid-gap have a limited effect in determining RON once the tail traps contributions have been introduced. Also, for gate biases greater than about 2Vth (i.e., VGS > 12 V) the increase of mobile carriers in the inversion layer leads to an increased screening of traps which enhances the MOSFET output current limiting the RON increase in particular at low temperatures. Finally, a high oxide-fixed trap density meaningfully influences Vth (negative shifting) and penalizes the device drain current over the whole explored voltage range.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Metal–oxide–semiconductor field effect transistors (MOSFETs) in silicon carbide (SiC) are very attractive devices in modern power electronics [1]. They are widely appreciated for their high efficiency, low on-state resistance (RON), and noticeable switching capabilities. Typical SiC MOSFETs are designed to support high blocking voltages (BVDS) ranging from 600 to 1700 V [2,3,4]. Recent papers, however, have also investigated low breakdown voltage 4H-SiC MOSFETs to be used for photovoltaic (PV) module-level applications enabling operation in harsh conditions with considerable lifetime [5,6,7,8,9,10]. Power optimizers in PV modules are generally rated for voltages in the order of 100–200 V.

The main technological issue of an SiC-based MOSFET is the effective quality of the silicon oxide (SiO2) interface that could make the device much less efficient. Defects occurring at the SiO2/4H-SiC interface, in fact, heavily affect the device current capability [11,12,13,14]. In more detail, the interface trap effects tend to decrease the carrier mobility in the channel region through the enhanced scattering mechanisms of free carriers. At the same time, traps increase the RON value and the sensitivity of the threshold voltage (Vth) with temperature.

In this context, the aim of the paper is to investigate, by means of a careful numerical simulation study, the electrical characteristics of a 4H-SiC MOSFET designed for low-voltage ratings (BVDS = 150 V) over a wide range of temperatures. Without loss of generality with respect to different designs dimensioned for higher blocking voltages, explicit interface trap effects due to a detailed density of states in the inversion region and a fixed trap density in the oxide are considered referring to literature data. A preliminary study at room temperature, which neglects defect and trap effects, was presented in Refs. [5, 6] emphasizing the use of fast and rugged 100-V-class switches.

The obtained results clarify the role of interface traps in reducing carrier mobility in the channel region (µch). Also, Vth decreases as a function of both trap density and temperature. In particular, a high oxide-fixed trap density meaningfully influences Vth. Finally, this analysis indicates that deep-level traps at the 4H-SiC interface have only a limited effect in determining the MOSFET RON once the tail traps contributions have been introduced. The RON value is 200 kΩ μm2 for a defective device at VGS = 10 V, VDS = 1 V, and T = 300 K. This result is compared to the state-of-the-art of a commercial Si-MOSFET with the same BVDS supporting the opportunity to explore the use of 4H-SiC also for low-voltage applications where efficiency, robustness, miniaturization, and temperature control are critical targets.

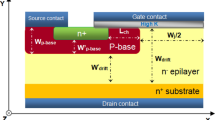

2 MOSFET structure

The schematic cross-section of the considered vertical n-channel 4H-SiC MOSFET single-cell is shown in Fig. 1. The different geometrical parameters are labeled as follows: Wcell is the cell width, WG is the gate contact width, Lch is the device channel length, WJ is the distance between the base regions, XN+ is the n+-source junction depth, XP is the p-base junction depth, Wdrift is the n-drift region thickness, \(W_{{_{\text{drift}} }}^{\prime }\) is the base-to-substrate distance, and Wsub is the starting substrate thickness. The source contact shorts the source and base regions to prevent the switch-on of the parasitic substrate(n+)–epilayer(n)–base(p)–source(n+) bipolar junction transistor. The reference geometrical and doping parameters used during the simulations are summarized in Table 1.

From Table 1, the distance between the n+-source region and the n-epilayer (i.e., XP–XN+) is 0.8 μm. The epilayer thickness ensures a BVDS value close to 150 V.

Although simplified for simulation purposes, the proposed structure is in principle compatible with a manufacturing process based on doping by ion implantation [15,16,17].

3 Physical models

The numerical simulation analysis was performed using the Atlas-Silvaco TCAD physical simulator [18]. The device structure was fine meshed wherever appropriate and in particular around the p–n junctions and the surface channel region under the SiO2/4H-SiC interface. The total number of mesh points was about 32,000 and the mesh spacing was scaled down to 0.5 nm at the interfaces.

The key physical models taken into account include the material bandgap temperature dependence, apparent bandgap narrowing effect, Auger and Shockley–Read–Hall recombination phenomena, incomplete doping activation, impact ionization, and carrier lifetime and carrier mobility expressions depending on temperature and doping concentration [19,20,21,22,23,24]. Moreover, Fermi–Dirac statistics and multidimensional dependent anisotropic effects as well as scattering mechanisms that degrade the channel mobility were considered during the simulations.

Parameters details about the simulation setup for 4H-SiC-based devices are reported in recent manuscripts of ours where the models prediction capabilities are also supported by experimental results obtained on implanted diodes over wide ranges of current and temperature [25,26,27,28,29,30].

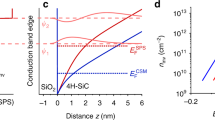

In this paper, to address the defect and trap effects at the SiO2/4H-SiC interface, we solve Poisson’s equation in the channel region in the form

where an overall trapped charge contribution QT is considered in addition to the ionized donor \((N_{\text{D}}^{ + } )\) and acceptor \((N_{\text{A}}^{ - } )\) impurity concentrations to describe the variation of the electrostatic potential ψ with the local (total) charge density.

According to [31], the incomplete ionization of impurities is given by

where ND and NA are the substitutional n-type and p-type doping concentrations, NC and NV are the electron and hole density of states varying with temperature, gc = 2 and gv = 4 are the degeneracy factors of the conduction and valence band, and ED = 100 meV and EA = 200 meV are the donor and acceptor energy levels assuming nitrogen and aluminum as doping species, respectively.

The interface density of states (DoS) in the 4H-SiC inversion layer is modeled by the following expression [32, 33]:

where \(D_{{it,{\text{M}}}}\) is a Gaussian distribution of deep states in the mid-gap and \(D_{{it,{\text{T}}}}\) is the sum of two exponentially decaying band tail states close to the conduction and valence band-edges, respectively. In more detail, we can write

where EC and EV are the conduction and valence band energies, UC and UV are characteristic energy decays, \(D_{{t,{\text{TC}}}}^{0}\) and \(D_{{t,{\text{TV}}}}^{0}\) are the band edge intercept densities, WM takes into accounts the spectral width of the mid-gap Gaussian distribution, and EM is the energy value of the defect density peak \(D_{{t,{\text{M}}}}^{0}\).

In Eq. (3) each term acts either as donor-like or acceptor-like level for free carriers [18]. In other words, a donor-like center is positively charged (ionized) when empty and neutral when filled (with an electron), while an acceptor-like center is negatively charged (ionized) when filled and becomes neutral when empty.

The total charge Qt is therefore expressed by

where referring to the terms \(D_{{it,{\text{M}}}}\) and \(D_{{it,{\text{T}}}}\) introduced above, \(D_{{it,{\text{D}}}}^{ + }\) and \(D_{{it,{\text{A}}}}^{ - }\) are the ionized densities for donor-like and acceptor-like traps, respectively. In particular, each ionized density depends upon the trap density and the relative probability of ionization that is in the form of

Here, vn and vp are the carrier thermal velocities, and σn and σp are the trap capture cross sections for electrons and holes, respectively. Finally, en and ep are the trap emission rates given by

where Ei is the intrinsic Fermi level and ni is the intrinsic carrier concentration.

The fundamental DoS parameters used during the simulations are listed in Table 2 [18, 33, 34]. In particular, the trap density reference values are assumed as in Ref. [33].

Finally, the Caughey–Thomas expression describes the temperature-dependent carrier mobility as

where the µ0n,p terms are the carrier mobilities assumed at room temperature, N is the local doping concentration, \(N_{\text{n,p}}^{\text{crit}}\) is the doping concentration at which the mobility is halfway between its maximum and minimum value, and α, β, γ, and δ are process-dependent coefficients [35]. This model was experimentally validated for SiC in Ref. [36].

The expected mobility reduction due to the carrier saturated drift velocity (vsat = 2 × 107 cm/s) was modeled for high electric fields by using

where E is the electric field in the direction of the current flow, and κn = 2 and κp= 1 [18]. In addition, mobility degradation effects that had taken place in the inversion layer can be written as

where \(E_{\text{n,p}}^{\text{crit}}\) is an adjustable parameter, and \(E_{ \bot }\) is the perpendicular electric field component which originates different scattering mechanisms involving surface-phonons, surface-roughness, and Coulombic scattering [18].

4 Results and discussion

4.1 I–V–T characteristics in absence of trap effects

A first set of simulations was addressed to clarify the dependence of BVDS on thickness (Wdrift) and doping (Ndrift) of the device epitaxial layer. In particular, with the MOSFET in off-state (VG = 0 and grounded source) VDS was gradually increased until the drain leakage current density reached a maximum value of 10 mA/cm2. Starting from Wdrift = 10 µm and Ndrift = 1×1016 cm−3, we calculated BVDS close to 900 V. This value corresponds to a critical electric field of 1.9 MV/cm. Then, Wdrift was reduced down to 1.8 µm as summarized in Table 3. It must highlighted that BVDS is strictly dependent on Wdrift which in fact determines the effective distance \(W_{{_{\text{drift}} }}^{\prime }\) between the base junction and the substrate, i.e., Wdrift − XP in Fig. 1.

By decreasing Ndrift from 1×1016 cm−3 to 1×1015 cm−3 we observed a maximum reduction of BVDS on the order of 10%. For example, for Ndrift = 3×1015 cm−3 we obtained BVDS = 150 V for Wdrift = 1.8 µm and BVDS = 850 V for Wdrift = 10 µm as in Ref. [6]. It is worth noting that Ndrift has only a limited impact in determining BVDS for Wdrift ≤ 3 µm.

The 4H-SiC MOSFET in Table 1 is a structure considered free of interface defects and traps (fresh device). The current density curves ID − VDS and ID − VGS calculated at different temperatures for the half-cell in Fig. 1 (active area 7.5 µm2) are shown in Figs. 2 and 3, respectively.

Forward ID − VDS characteristics for the device in Table 1 at T = 300 K, T = 400 K, and T = 500 K

ID − VGS curves for the device in Table 1 at different temperatures

As expected, the drain current decreases harshly when increasing temperature. This effect is determined by the temperature dependence of carrier mobility in the inversion layer and the overall increase of the device on-state resistance.

In more detail, the degradation of the total carrier mobility behavior in the channel region is shown in Fig. 4. Here, the temperature dependence of the threshold voltage is also reported by imposing during the simulations a subthreshold current in the limit of 10 nA. The plot is traced by taking a cut-line of the device structure for VGS = 15 V and VDS = 1 V.

The decrease of Vth and µch with temperature is due to the increase of the 4H-SiC intrinsic carrier concentration. These variations determine different values of the device transconductance which results 25 s at T = 300 K and decreases to about 10 s at T = 500 K in the considered range of VGS.

From Fig. 3, the drain current density for VGS = 15 V and VDS = 1 V at T = 300 K is 7.11 μA/μm2 (ID = 53.32 μA). The corresponding MOSFET RON is therefore calculated as close to 140 kΩ μm2. The RON behavior as a function of the temperature is shown in Fig. 5. Here, the RON increase with temperature is mainly due to the decrease of carrier mobility in the inversion layer as well as in the drift region [37]. In other words, the increased temperature limits the current components in these two regions.

4.2 Analysis of trap effects at the SiO2/4H-SiC interface

4.2.1 Tail traps

Introducing in the model a constant value of deep traps in the mid-gap, i.e., \(D_{{t,{\text{M}}}}^{0} = 2. 3\times 1 0^{ 1 1} \,\,{\text{cm}}^{ - 2} \,\,{\text{eV}}^{ - 1}\) [33], Fig. 6 depicts the device ID − VGS characteristics in semi-logarithmic scale calculated for a different band tail trap density at T = 300 K, T = 400 K, and T = 500 K. In particular, in Eq. (4) we have assumed the band edge intercept density in the range from 1012 cm−2 eV−1 to 1014 cm−2 eV−1 [33, 38]. In addition, it is important to note that the traps with energetic states close the valence band can be neglected once the contribution \(D_{{t,{\text{TC}}}}^{0} \exp^{{[(E - E_{\text{C}} )/U_{\text{C}} ]}}\) has been considered. In this study, in fact, when the device is forward biased, even in weak inversion condition, the Fermi level increasingly moves in the upper half of the bandgap.

From Fig. 6, similarly to the fresh device, Vth tends to decrease as the temperature increases. For VGS > Vth, the saturated value of ID is almost the same until the tail trap density is in the limit of 1013 cm−2 eV−1. Then, for example for \(D_{{t,{\text{TC}}}}^{0}\) = 1014 cm−2 eV−1, the device current capabilities are meaningfully penalized at any VDS bias level.

When a positive VGS is applied, the acceptor defect states are able to trap a great number of electrons from the inversion layer, thus making them immobile and excluding them from carrier transport mechanisms. In addition, at each temperature, these filled traps cause Coulomb scattering phenomena of mobile charges that determine in turn a reduced drain current and a positive shift of the threshold voltage. The more the temperature increases, the more the number of filled traps decreases; hence Vth decreases as stated above.

The MOSFET RON behaviors as a function of VGS for both a fresh and a defective device are shown in Fig. 7. The RON of a heavily defective device dramatically increases for increasing temperature in particular at low biases (VGS ≤ 12 V) as a consequence of the mobility degradation induced by traps [39]. For VGS> 12 V, however, the increase of mobile carriers leads to an increased screening of traps which supports the MOSFET output current limiting the RON increase especially at low temperatures.

4.2.2 Deep-level traps

The MOSFET ID − VGS characteristics for two different distributions of deep-level traps (not exceeding a peak value of 1012 cm−2 eV−1 [38]) are shown in Fig. 8. A fixed band edge intercept density \(D_{{t,{\text{T}}}}^{0}\) = 1013 cm−2 eV−1 was assumed during the simulations.

In this case, the trap effects mostly occur at the beginning of the ID curves determining, once again, an increase in the device threshold voltage. In other words, since the tail traps contribution has been introduced, the effect of the trapped charge in the deep-level traps on the slope of the ID curves in Fig. 8 is negligible and, in fact, for VGS> 10 V the drain current appears not affected. This result is shown in more detail in Fig. 9 by plotting the RON behaviors as a function of VGS at different temperature (11 ≤ VGS ≤ 15 V).

4.2.3 Oxide-fixed traps

Moving from the developed analysis on the interface-trapped charges which are related to the defect energy levels inside the 4H-SiC bandgap, in order to determine the effective MOSFET current capability, in this section we have involved in the model an oxide-fixed trap effect as shown in Fig. 10. In particular, we have considered a thin film of fixed traps located in the oxide next to the SiO2/4H-SiC interface with a charge density Nfix = 1.3 × 1012 cm−2 [33].

The oxide-fixed traps, which have a density strictly dependent on the 4H-SiC surface oxidation process, became scattering centers that influence the device threshold voltage as shown in Fig. 11. Here, the carrier mobility degradation in the inversion layer is also reported.

From Fig. 11, it is clear that the MOSFET threshold voltage significantly decreases in presence of an explicit oxide-fixed trap density. These centers, in fact, by acting as positive charges produce a band bending at the semiconductor interface even without the application of a positive bias voltage at the gate contact [40, 41]. In other words, the band bending for a p-type MOSFET tends to induce a depletion region (channel region) before VGS is applied. This effect obviously reduces Vth at any operation temperature. In addition, due to the Coulombic scattering [42], the effective carrier mobility in the inversion layer is degraded as well.

The comparison of the defective device in Fig. 10 (\(D_{{t,{\text{T}}}}^{0}\) = 1013 cm−2 eV−1, \(D_{{t,{\text{M}}}}^{0}\) = 1012 cm−2 eV−1, and Nfix = 1.3 × 1012 cm−2) and the fresh one in Fig. 3 in terms of RON at different temperatures is shown in Fig. 12.

Here, the datasheet value RON = 216 kΩ μm2 for a Si-based commercial MOSFET rated for 150 V at VGS = 10 V and T = 300 K is also reported [43]. This value is slightly higher than that calculated for the proposed device at the same bias level, namely RON = 200 kΩ μm2. In presence of an oxide-fixed trap effect, the RON behavior tends to increase over the whole explored VGS range in particular at the higher temperatures that increasingly contribute to limit the drain current.

5 Conclusion

The temperature and carrier-trapping effects on the electrical characteristics of a 4H-SiC MOSFET have been predicted by means of numerical simulations. A combined model of defect energy levels inside the 4H-SiC bandgap (tail and deep-level traps) and oxide-fixed traps has been considered. The trap densities have been assumed referring to literature data. The device exhibits an epilayer thickness of 1.8 µm and a breakdown voltage of 150 V.

Starting from a defect-free structure we have calculated an on-state resistance close to 140 kΩ μm2 (VGS = 10 V, VDS = 1 V, and T = 300 K), which increases up to 200 kΩ μm2 for a defective device. This result is comparable to that of a commercial Si-based MOSFET rated for the same voltage range. The MOSFET threshold voltage and carrier mobility in the channel region decrease as a function of both temperature and trap density. In particular, the oxide-fixed traps have a severe impact on the threshold voltage.

The presented analysis could turn useful to support the design of low breakdown voltage 4H-SiC-based MOSFETs seeing that the pure experimental characterization of the device reliability is very expensive and time consuming.

References

B.J. Baliga, Silicon carbide power devices (World Scientific, Singapore, 2005)

ROHM Model SCT2H12NZ (1700V), http://www.rohm.com/web/eu/products/-/product/SCT2H12NZ. Accessed 10 Jan 2019

CREE Model C3M0280090D (900V), http://www.wolfspeed.com/c3m0280090d. Accessed 10 Jan 2019

ROHM Model SCT3017AL (650V) http://www.rohm.com/web/eu/products/-/product/SCT3017AL. Accessed 10 Jan 2019

F.G. Della Corte, G. De Martino, F. Pezzimenti, G. Adinolfi, G. Graditi, IEEE Trans. Electron Dev 65, 3352–3360 (2018)

G. De Martino, F. Pezzimenti, F. G. Della Corte, G. Adinolfi, G. Graditi, in Proceedings of the IEEE International Conference on Ph. D. Research in Microelectronics and Electronics—PRIME, pp. 221–224 (2017)

O. Khan, W. Xiao, M. Shawky El Moursi, I.E.E.E. Trans, Power Electron. 32, 3278–3284 (2017)

H. Zhou, J. Zhao, Y. Han, I.E.E.E. Trans, Power Electron. 30, 3479–3487 (2015)

G. De Martino, F. Pezzimenti, F. G. Della Corte, in Proceedings of the International Semiconductor Conference—CAS, pp. 147–150 (2018)

Y. Shi, R. Li, Y. Xue, H. Li, I.E.E.E. Trans, Power Electron. 31, 328–339 (2015)

K. Tachiki, T. Ono, T. Kobayashi, H. Tanaka, I.E.E.E. Trans, Electron Dev. 65, 3077–3080 (2018)

D.P. Ettisserry, N. Goldsman, A. Lelis, J. Appl. Phys. 115, 103706 (2014)

J.M. Knaup, P. Deak, T. Frauenheim, A. Gali, Z. Hajnal, W.J. Choyke, Phys. Rev. 72, 115323 (2005)

Y. Tanimoto, A. Saito, K. Matsuura, H. Kikuchihara, H.J. Mattausch, M. Miura-Mattausch, N. Kawamoto, I.E.E.E. Trans, Power Electron. 31, 4509–4516 (2016)

W. Sung, B.J. Baliga, I.E.E.E. Electr, Device L. 37, 1605–1608 (2016)

Y. Mikamura, K. Hiratsuka, T. Tsuno, H. Michikoshi, S. Tanaka, T. Masuda, T. Sekiguchi, I.E.E.E. Trans, Electron Dev. 62, 382–389 (2014)

M. Okamoto, M. Iijima, T. Nagano, K. Fukuda, H. Okumura, Mater. Sci. Forum 717, 781–784 (2012)

Silvaco Int., Atlas user’s manual, Device Simulator Software (2016)

F. Pezzimenti, I.E.E.E. Trans, Electron Dev. 60, 1404–1411 (2013)

F. Bouzid, L. Dehimi, F. Pezzimenti, M. Hadjab, A.H. Larbi, Superlattice. Microst. 122, 57–73 (2018)

Y. Marouf, L. Dehimi, F. Bouzid, F. Pezzimenti, F.G. Della Corte, Optik 163, 22–32 (2018)

F. Bouzid, F. Pezzimenti, L. Dehimi, M.L. Megherbi, F.G. Della Corte, Jpn. J. Appl. Phys. 56, 094301 (2017)

F. Pezzimenti, F. G. Della Corte, in Proceedings of the Mediterranean Electrotechnical Conference—MELECON, pp. 1129–1134 (2010)

F. Bouzid, L. Dehimi, F. Pezzimenti, J. Electron. Mater. 46, 6563–6570 (2017)

M.L. Megherbi, F. Pezzimenti, L. Dehimi, M.A. Saadoune, F.G. Della Corte, IEEE Trans. Electron Dev. 65, 3371–3378 (2018)

K. Zeghdar, L. Dehimi, F. Pezzimenti, S. Rao, F.G. Della Corte, Jpn. J. Appl. Phys. 58, 014002 (2019)

F.G. Della Corte, F. Pezzimenti, S. Bellone, R. Nipoti, Mater. Sci. Forum. 679, 621–624 (2011)

F. Pezzimenti, S. Bellone, F.G. Della Corte, R. Nipoti, Mater. Sci. Forum. 740, 942–945 (2013)

F. Pezzimenti, L. F. Albanese, S. Bellone, F. G. Della Corte, in Proceedings of the IEEE international conference on bipolar/BiCMOS circuits and technology meeting, pp. 214–217 (2009)

M.L. Megherbi, F. Pezzimenti, L. Dehimi, A. Saadoune, F.G. Della Corte, J. Electron. Mater. 47, 1414–1420 (2018)

M. Ruff, H. Mitlehner, R. Helbig, I.E.E.E. Trans, Electron Dev. 41, 1040–1054 (1994)

S. Dhar, S. Haney, L. Cheng, S.R. Ryu, A.K. Agarwal, J. Appl. Phys. 108, 054509 (2010)

S. Potbhare, N. Goldsman, G. Pennington, A. Lelis, J.M. McGarrity, J. Appl. Phys. 100, 044515 (2006)

E.I. Dimitriadis, N. Archontas, D. Girginoudi, N. Georgoulas, Microelectron. Eng. 133, 120–128 (2015)

X. Li, Y. Luo, L. Fursin, J.H. Zhao, M. Pan, P. Alexandrov, M. Weiner, Solid State Electron. 47, 233–239 (2003)

M. Roschke, F. Schwierz, I.E.E.E. Trans, Electron Dev. 48, 1442–1447 (2001)

B.J. Baliga, Fundamentals of power semiconductor devices (Springer, New York, 2008)

F. Devynck, A. Alkauskas, P. Broqvist, A. Pasquarello, Phys. Rev. 84, 235320 (2011)

J. Rozen, A.C. Ahyi, X. Zhu, J.R. Williams, L.C. Feldman, I.E.E.E. Trans, Electron Dev. 58, 3808–3811 (2011)

A. Kerber, E. Cartier, L. Pantisano, R. Degraeve, T. Kauerauf, Y. Kim, A. Hou, G. Groeseneken, H.E. Maes, U. Schwalke, I.E.E.E. Electr, Device L. 24, 87–89 (2003)

S. Zafar, A. Callegari, E. Gusev, M.V. Fischetti, J. Appl. Phys. 93, 9298 (2003)

S. Potbhare, N. Goldsman, G. Pennington, A. Lelis, J.M. McGarrity, J. Appl. Phys. 100, 044516 (2006)

Infineon model IPB072N15N3 G (150V), https://www.infineon.com/cms/en/product/power/mosfet/20v-300v-n-channel-power-mosfet/120v-300v-n-channel-power-mosfet/ipb072n15n3-g/. Accessed 10 Jan 2019

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bencherif, H., Dehimi, L., Pezzimenti, F. et al. Temperature and SiO2/4H-SiC interface trap effects on the electrical characteristics of low breakdown voltage MOSFETs. Appl. Phys. A 125, 294 (2019). https://doi.org/10.1007/s00339-019-2606-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-2606-9