Abstract

This paper presents a dual-wideband, common-gate, cascode low-noise amplifier (LNA) using gain–bandwidth product optimization technique. This approach shrinks the aspect ratio of the cascode MOS device, thereby reducing the equivalent parasitic capacitance of the resonator load to optimize the gain–bandwidth product of the LNA. The input impedance of the proposed LNA is analyzed, and the noise factor is well predicted through analytical equations. Measurement results that show well agreement with post-simulation results demonstrate the feasibility of this technique. In low-band mode, experimental results presented a maximum \(\left| S_{21} \right| \) of 13.4 dB over a \(-\)3-dB bandwidth of 3.1–4.8 GHz with a minimum noise figure of 4.5 dB. In high-band mode, the proposed LNA achieved a maximum \(\left| S_{21} \right| \) of 13.6 dB with a minimum noise figure of 6.2 dB over a \(-\)3-dB bandwidth of 7.3–9.4 GHz. A test chip with a die area of 0.83 mm\(^{2}\) was fabricated using a 0.18 \(\upmu \)m CMOS process. The proposed dual-wideband LNA consumes 9.1 mW, excluding the buffer, from a supply voltage of 1.8 V.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the increasing demands for different types of wireless standards integrated in one mobile terminal, the dual-band low-noise amplifiers have recently gained a lot of interest. During the last few years, many methodologies have been proposed for the design of dual-band LNA [1–4, 6, 7, 9–15, 17–22]. One approach is based on a high-value active inductor with a wide tuning range [7, 15]. This approach achieves a good performance with small chip area, however, at the cost of higher power consumption. The second approach involved the use of a notch filter within a wideband LNA to achieve dual-band performance [3, 10, 14, 21, 22]. Unfortunately, this approach also suffers from high power consumption due to the wideband design with an additional notch filter. Another approach involved the use of switched capacitors and switched circuits to realize the dual-band operation [1, 2, 6, 9, 11, 13, 17–20]. This approach, however, still suffered from the trade-off between power consumption, gain, and the bandwidth that was mainly limited by the parasitic capacitance of devices for both bands. As to the bandwidth enhancement of LNA, double loop feedback topology was proposed to obtain wideband performance [12]. However, it is difficult to apply this technique to dual-wideband LNA because it is hard to optimize the component values for both bands simultaneously.

This study employed a switched inductor with common-gate (CG) cascode topology to facilitate the realization of wideband input matching. However, this approach suffered from two drawbacks. The first drawback was the limited \(-\)3-dB bandwidth in the high frequency range due to the parasitic capacitance of MOS devices. The second drawback was a trade-off between the \(-\)3-dB bandwidth and gain. To overcome these drawbacks, this paper proposes a gain–bandwidth product optimization technique that reduces the parasitic capacitance of the cascode MOS device to optimize the gain–bandwidth product of the dual-wideband LNA in the high frequency band.

The remainder of this paper is organized as follows. Section 2 introduces the proposed gain–bandwidth product optimization technique, as well as input impedance matching and noise analysis of the proposed dual-wideband common-gate cascode CMOS LNA. Section 3 presents the simulation and measurement results demonstrating the feasibility of the proposed technique. Section 4 provides conclusions.

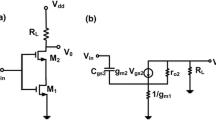

a Typical topology of common-gate cascode amplifier with single tuned load; b Simplified small-signal equivalent circuit of Fig. 1a

2 Principles of Circuit Design

2.1 Gain–Bandwidth Product Optimization Technique

Figure 1 outlines the typical topology of a common-gate cascode amplifier with single tuned load and the simplified small-signal equivalent circuit, where \(C_{d}\), \(R_{d}\), and \(G_{m}\) are the equivalent capacitance and parasitic parallel resistance of the tank load, and the equivalent transconductance of the common-gate cascode amplifier, respectively. Through simple derivation, we easily obtained the dominant resonant frequency (\(f_\mathrm{res}\)), \(-\)3-dB bandwidth (BW), and gain–bandwidth product (GBW), expressed as (1) to (3), respectively [8].

where

Equation (1) clearly shows that the \(L_{d}\)(\(C_{d}\) +\( C_{gd2}\)) product must be reduced when the resonant frequency is increased. Thus, most tuned amplifiers operating in the high frequency band adopt only the inductor as the load and utilize the parasitic capacitance of the inductor to replace \(C_{d}\). However, at higher frequencies, \(C_{d}\) also decreases when the load inductance \(L_{d}\) is decreased. Thus, \(C_{gd2}\) dominates the (\(C_{d}\) + \(C_{gd2}\)) term and becomes the factor limiting the bandwidth in the high frequency band. Reducing resistance \(R_{d}\) would increase the bandwidth; however, this would simultaneously decreases the amplifier gain.

Fortunately, Eq. (3) indicates that the gain–bandwidth product can be improved by decreasing \(C_{gd2}\). This also means that the gain–bandwidth product can be increased under the same power consumption conditions. Thus, this paper proposes a gain–bandwidth product optimization technique to reduce the width of \(M_{2}\), which is equivalent to reducing parasitic capacitance \(C_{gd2}\) in order to improve the gain–bandwidth product and operation bandwidth of common-gate cascode LNA in the high frequency band.

Figure 2 presents the normalized gain–bandwidth product curves versus the ratio of \(W_{M2}\) and \(W_{M1}\), \(\chi \), for \(M_{1}\) of various widths for most common-gate cascode CMOS LNA designs, in which each curve is normalized to the value of its gain–bandwidth product at \(\chi \)=1. The reason for the maximum value in each GBW curve of Fig. 2 can be explained by expressing the gain–bandwidth product as (4) by rewriting the \(G_{m}\) and \(C_{gd2}\) of (3) as functions of \(\chi \).

where \(\mu _{n}C_{ox}\) and \(\lambda \) are the process transconductance parameters and the channel length modulation coefficient of MOSFET devices, respectively. \(W_{M1}\)/L and \(V_{T2}\) are the aspect ratio of \(M_{1}\) and the threshold voltage of \(M_{2}\), respectively. For example, for a given \(W_{M1}\), when \(\chi \) is close to 1, the \(\chi C_{gd1}\) term dominates the sum in the denominator. As \(\chi \) decreases, the rate of decrease of the denominator is faster than the rate of decrease of the numerator. Thus, the gain–bandwidth product increases. However, as \(\chi \) approaches zero, the denominator is dominated by \(C_{d}\) and approaches \(C_{d}\). Meanwhile, the \(\sqrt{2I_{D}L/(\mu _{n}C_{ox}\chi W_{M1})}\) term in the numerator becomes larger, thereby causing the rate of decrease of the numerator to exceed the rate of decrease of the denominator, whereupon the gain–bandwidth product begins decreasing after reaching its maximum value. These results demonstrate the optimum \(\chi \) capable of inducing the maximum gain–bandwidth product. In other words, \(\chi \) can be reduced to the optimum value in Fig. 2, which is equivalent to reducing the \(R_{d}(C_{d}+C_{gd2})\) time constant of the resonator load, thereby expanding the bandwidth and optimizing the gain–bandwidth product of the proposed LNA. In addition, when a larger \( W_{M1}\) is selected, a smaller \(\chi \) is required to ensure that the \(\sqrt{2I_{D}L/(\mu _{n}C_{ox}\chi W_{M1})}\) term dominates the numerator. This explains why the maximum GBW is achieved at smaller \(\chi \) for curves of larger \(W_{M1}\).

Normalized gain–bandwidth product curves of Fig. 1 versus the ratio of \(W_{M2}\) and \(W_{M1}\), \(\chi \), for channels of various width of \(M_{1}\), \(W_{M1}\)

2.2 Input Impedance Matching

Figure 3a presents a schematic diagram of the input impedance matching network and part of the equivalent small-signal circuits of the input impedance matching network of the proposed dual-wideband, common-gate cascode LNA. A source inductor \(L_{S}\) is used to provide the DC path, and a gate-terminating inductor \(L_{G}\) is used to compensate the gain attenuation of the common-gate stage in the high frequency range [16]. For the equivalent small-signal circuits shown in Fig. 3b, the input impedance \(Z_{s}\) can be expressed as:

where

If the operating frequency meets the condition of (5b), by substituting (5b) into (5a), the input impedance \(Z_{s}\) can be simplified as:

For the design cases in this study, impedance \(Z_{s}\) is lower than 50 \(\Omega \) because the transconductance \(g_{m1}\) is designed to be larger than 20 mS to meet the high gain requirement. Therefore, we employed an LC ladder resonator to ensure that the input impedance matches 50 \(\Omega \). The input impedance \(Z_{in}\) is expressed as follows:

Similarly, the values for \(C_{1}\) and \(L_{1}\) can be selected to set the imaginary part of (7) to zero. Thus, the resonant frequency \(\omega _{r}\) can be tuned to be as close as possible to the operating frequency \(\omega _{oi}\) mentioned in (5b). We can then express the resonant frequency \(\omega _{r}\) as follows:

By substituting (8) into (7), the purely resistive input impedance \(Z_{in}\) can be reformulated as

By substituting the design parameters of \(g_{m1}= 40.63\) mS, \(L_{G} = 482\) pH, \(L_{S}= 4.315\) nH, \(L_{1}= 392\) pH, and \(C_{1}\) = 388.5 fF into (9), we obtain the input impedance \(Z_{in}\approx \) 45.6 \(\Omega \), which is close to 50 \(\Omega \). Figure 4 presents the simulated loci of \(S_{11}\) of the proposed LNA with and without series input capacitor \(C_{in}\) for frequencies ranging from 3 to 11 GHz.

2.3 Noise Analysis

Figure 5 outlines the equivalent circuit of common-gate cascode LNA with the input matching network in Fig. 3a for the calculation of noise. It is assumed that the gain of the LNA is large enough when the LNA is operated at a resonant frequency at which the noise contribution from the resonator load can be disregarded. Thus, the noise factor can be expressed as follows:

where \(i_{n,\mathrm{out}}\) represents the total noise current in the short-circuited output path originating from noise current components \(i_{so}\), \(i_{L1o}\), \(i_{Lso}\), \(i_{nd1o}\), and \(i_{nd2o}\), which are produced by the noise generators \(e_{s}\), \(e_{L1}\), \(e_{Ls}\), \(i_{nd1}\), and \(i_{nd2}\), respectively. \(F_{L1} = \overline{ \left| i^{2}_{L1o} \right| }/\overline{ \left| i^{2}_{so} \right| }\), \(F_{Ls}= \overline{ \left| i^{2}_{Lso} \right| }/\overline{ \left| i^{2}_{so} \right| }\), \(F_{M1} = \overline{ \left| i^{2}_{nd1o} \right| }/\overline{ \left| i^{2}_{so} \right| }\), and \(F_{M2} = \overline{ \left| i^{2}_{nd2o} \right| }/\overline{ \left| i^{2}_{so} \right| }\) represent the corresponding noise factor contributions of \(i_{L1o}\), \(i_{Lso}\), \(i_{nd1o}\), and \(i_{nd2o}\) to the LNA, respectively.

Equations (11a)–(11g) present each noise factor in detail, where \(g_{d0}\) is the drain–source conductance at zero \(V_{DS}\), \(\alpha \) is the ratio of \(g_{m}\) to \(g_{d0}\), \(\gamma \) is the coefficient of channel noise, and \(Z_{ss}\) is the equivalent impedance observed in the input impedance network from the channel noise source \(i_{nd1}\).

where

and

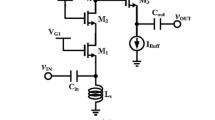

2.4 Proposed Dual-Wideband Common-Gate Cascode LNA

Figure 6 presents a schematic diagram of the proposed dual-wideband common-gate cascode low-noise amplifier. This dual-wideband LNA is operated between 3.1 and 4.8 GHz in low-band mode and 7.3–9.4 GHz in high-band mode using a band selection switch \(M_{SW}\). The equivalent parasitic capacitance of the resonator can be reduced by shrinking the size of \(M_{2}\). Thus, the proposed dual-wideband LNA is capable of achieving multi-GHz \(-\)3-dB bandwidth when operated in the high frequency range using the proposed gain–bandwidth product optimization technique. The aspect ratio of NMOS \(M_{1}\) is fine tuned to \(108.8/0.18\,\upmu \)m to meet the gain and input matching requirements. Meanwhile, the aspect ratio of NMOS \(M_{2}\) is set to \(28.8/0.18\,\upmu \)m. That is equivalent to \(\chi \approx 0.26\), which is close to the expected \(\chi \) ratio presented in Fig. 2 with the maximum gain–bandwidth product and expanded bandwidth in the high frequency band. It is worth mentioning that the current consumption of the proposed common-gate cascode LNA shown in Fig. 6 is dominated by the bias condition of \(M_{1}\). Therefore, shrinking the width of \(M_{2}\) will not increase the current consumption of the proposed dual-wideband common-gate cascode LNA. The circuit designers can maximize the gain–bandwidth product of the proposed common-gate cascode LNA by sizing the \(M_{2}\) transistor and not increasing power consumption.

3 Experimental Results

The proposed dual-wideband common-gate cascode LNA was fabricated in a 0.18 \(\upmu \)m CMOS process. Figure 7 presents a micrograph of the chip, that occupies 0.83 \(\hbox {mm}^{2}\) including pads and bypass capacitors. The testing phase considered on-wafer measurements using ground–signal–ground (GSG) and DC probes. Figure 8 presents the post-layout simulated and measured \(\left| S_{21} \right| \) and \(\left| S_{11} \right| \) of the proposed LNA. The proposed dual-wideband LNA achieved a \(-\)3-dB bandwidth of 3.1–4.8 GHz with a peak gain of 13.4 dB in low-band mode and a \(-\)3-dB bandwidth of 7.3–9.4 GHz with a peak gain of 13.6 dB in high-band mode. Figure 9 presents the calculated, post-simulated, and measured noise figure (NF) of the proposed LNA, where a \(\gamma \) of 2.21 which is a measured average value is adopted for the calculated NF [5]. These results present good agreement between the calculated and simulated NF at resonant frequencies in both the low-band mode (3.95 GHz) and high-band mode (8.35 GHz) to demonstrate the accuracy of (10) and (11a–11g).

Measurement results show that the measured NF in low-band mode was 4.5–5.3 dB between 3.1 and 4.8 GHz. In high-band mode, the measured NF was 6.2–7.9 dB between 7.3 and 9.4 GHz. The discrepancy between the measured and post-layout simulated noise figures was caused by inaccuracies in the noise model. Figure 10a and b presents the measured third-order intermodulation characteristics of the proposed LNA with two tone frequencies of \(3960\,\pm \,264\) MHz (low-band mode) and 8184\(\pm \)264 MHz (high-band mode), respectively. The measured input-referred third-order intercept points (IIP3) were \(-10\) dBm (low-band mode) and \(-12\) dBm (high-band mode), respectively. The measured input-referred 1-dB compression points were \(-24\) dBm (low-band mode) and \(-27\) dBm (high-band mode), respectively. From a 1.8 V supply, the proposed LNA consumes 9.1 mW, excluding the buffer.

Table 1 summarizes the performance of recently published dual-band LNAs. A figure of merit (FoM) factor shown as (12) that represents the achieved gain–bandwidth product, which is normalized to the power consumption and the process technology, is introduced to reveal the value of the proposed gain–bandwidth product optimization technique.

where \(L_{\mathrm{min}}\) represents the minimum channel length of the CMOS process technology that is used in the corresponding paper.

Compared with other published dual-band LNAs, the proposed LNA achieves the best FoM in both bands. Although [13] achieved an ultra-high FoM value in high-band mode, it suffered from very large \(\left| S_{21}\right| \) variation (up to 9.5 dB) due to the low equivalent parallel resistance of the resonator load when the LNA was switched to low-band mode. However, this work maintains nearly the same \(\left| S_{21}\right| \) in both low-band and high-band modes that are attributable to the proposed gain–bandwidth product optimization technique.

4 Conclusion

This paper presents a dual-wideband, common-gate cascode CMOS LNA using gain–bandwidth product optimization technique. The gain–bandwidth product of the LNA was optimized by reducing the equivalent parasitic capacitance of the resonator load. Compared with other previous works, the proposed LNA achieves the best gain–bandwidth product, which is normalized to the power consumption and process technology, in both bands by utilizing the proposed optimization technique. In other words, circuit designers can maximize the gain–bandwidth product of the proposed common-gate cascode LNA without increasing power consumption, thereby demonstrating the feasibility of the proposed gain–bandwidth product optimization technique.

References

N. Cho, J. Bae, H.J. Yoo, A 10.8 mW body channel communication/MICS dual-band transceiver for a unified body sensor network controller. IEEE J. Solid State Circuits 44(12), 3459–3468 (2009)

G.Z. Fatin, Z.D. Koozehkanani, H. Sjöland, A 90 nm CMOS +11 dBm IIP3 4 mW dual-band LNA for cellular handsets. IEEE Microw. Wirel. Compon. Lett. 20(9), 513–515 (2010)

Y. Gao, Y.J. Zheng, B.L. Ooi, 0.18 \(\upmu \)m CMOS dual-band UWB LNA with interference rejection. Electron. Lett. 43(20), 1096–1098 (2007)

H. Hashemi, A. Hajimiri, Concurrent multiband low-noise amplifiers—theory, design, and applications. IEEE Trans. Microw Theory Tech. 50(1), 288–301 (2002)

P. Heydari, Design and analysis of a performance-optimized CMOS UWB distributed LNA. IEEE J. Solid State Circuits 42(9), 1892–1905 (2007)

Z.Y. Huang, C.C. Hung, CMOS dual-band low-noise amplifier for world-wide WiMedia ultra-wideband wireless personal area networks system. in Proceeding of Asia-Pacific Microwave Conference, 2010 pp. 334–337

H.B. Kia, A.K. A’ain, I. Grout, I. Kamisian, A reconfigurable low-noise amplifier using a tunable active inductor for multistandard receivers. Circuits Syst. Signal Process. 32, 979–992 (2013)

T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd edn. (Cambridge University Press, Cambridge, 2004)

Z. Li, R. Quintal, K.O. Kenneth, A dual-band CMOS front-end with two gain modes for wireless LAN applications. IEEE J. Solid State Circuits 39(11), 2069–2073 (2004)

J.Y. Lin, H.K. Chiou, Power-constrained third-order active notch filter applied in IR-LNA for UWB standards. IEEE Trans. Circuits Syst. II: Express Briefs 58(1), 11–15 (2011)

L.H. Lu, H.H. Hsieh, Y.S. Wang, A compact 2.4/5.2-GHz CMOS dual-band low-noise amplifier. IEEE Microw. Wirel. Compon. Lett. 15(10), 685–687 (2005)

M.A. Martins, K. van Hartingsveldt, J.R. Fernandes, M.M. Silva, C.J.M. Verhoeven, Low noise amplifiers with double loop feedback. Circuits Syst. Signal Process. 32, 541–558 (2013)

N.M. Neihart, J. Brown, X. Yu, A dual-band 2.45/6 GHz CMOS LNA utilizing a dual-resonant transformer-based matching network. IEEE Trans. Circuits Syst. I: Regul. Pap. 59(8), 1743–1751 (2012)

B. Park, S. Choi, S. Hong, A low-noise amplifier with tunable interference rejection for 3.1- to 10.6-GHz UWB systems. IEEE Microw. Wirel. Compon. Lett. 20(1), 40–42 (2010)

Md.M. Reja, K. Moez, I. Filanovsky, An area-efficient multistage 3.0- to 8.5-GHz CMOS UWB LNA using tunable active inductors. IEEE Trans. Circuits Syst. II: Express Briefs 57(8), 587–591 (2010)

N. Shiramizu, T. Masuda, M. Tanabe, K. Washio, A 3-10 GHz bandwidth low-noise and low-power amplifier for full-band UWB communications in 0.25-\(\upmu \)m SiGe BiCMOS technology. in IEEE Radio Frequency Integrated Circuits Symposium, 2005, pp. 39–42

H. Song, H. Kim, K. Han, J. Choi, C. Park, B. Kim, A sub-2 dB NF dual-band CMOS LNA for CDMA/WCDMA applications. IEEE Microw. Wirel. Compon. Lett. 18(3), 212–214 (2008)

G.M. Sung, X.J. Zhang, A 2.4-GHz/5.25-GHz CMOS variable gain low noise amplifier using gate voltage adjustment. in IEEE International Midwest Symposium on Circuits and Systems, 2013, pp. 776–779

X. Tang, F. Huang, Y. Zhang, S. Lin, Design of a reconfigurable low noise amplifier for IMT-A and UWB systems. in IEEE MTT-S International Microwave Workshop Series on Millimeter Wave Wireless Technology and Applications, 2012, pp. 1–4

T.K.K. Tsang, M.N. El-Gamal, Dual-band sub-1V CMOS LNA for 802.11a/b WLAN applications. in IEEE International Symposium on Circuits and Systems, I-217-I-220 2003

A. Vallese, A. Bevilacqua, C. Sandner, M. Tiebout, A. Gerosa, A. Neviani, Analysis and design of an integrated notch filter for the rejection of interference in UWB systems. IEEE J. Solid State Circuits 44(2), 331–343 (2009)

K. Xuan, K.F. Tsang, W.C. Lee, S.C. Lee, 0.18 \(\upmu \)m CMOS dual-band low-noise amplifier for ZigBee development. Electron. Lett. 46(1), 85–86 (2010)

Author information

Authors and Affiliations

Corresponding author

Additional information

The authors would like to thank the Chung Yuan Christian University for financial support, and thank National Chip Implementation Center (CIC), Hsin-Chu, Taiwan, for chip fabrication and measurement support.

Rights and permissions

About this article

Cite this article

Chen, CC., Wang, YC. A Dual-Wideband CMOS LNA Using Gain–Bandwidth Product Optimization Technique. Circuits Syst Signal Process 36, 495–510 (2017). https://doi.org/10.1007/s00034-016-0322-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0322-7