Abstract

Among Field-Coupled technologies, NanoMagnet Logic (NML) is one of the most promising. Low dynamic power consumption, total absence of static power, remarkable heat and radiations resistance, in association with the possibility of combining memory and logic in the same device, make this technology the ideal candidate for low power, portable applications. However, the necessity of using an external magnetic field to locally control the circuit represents, currently, the weakest point of this technology. The high power losses in the clock generation system adopted up to now wipes out the most important advantages of this technology.

In this chapter we discuss a clock system based on a piezoelectric actuator that allows electrical control of NanoMagnet Logic circuits. The low power consumption coupled with the fact that electric fields are easier to generate at the nanoscale level makes this clock system a strong candidate as the final and effective clocking mechanism for this technology. Another remarkable advantage of the proposed solution resides in its compatibility with currently available technology.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

1 Introduction on Clocking For NML Logic

Recent years have shown a rapidly rising interest in field-coupled technologies, like Quantum dot Cellular Automata (QCA) [1]. In these devices information is not represented using voltage or current values, but rather with identical cells that can assume different charge configurations [2]. Information propagates therefore through the electrostatic interaction among neighbor cells [3]. Different means can be used to map the QCA theoretical principle on practical application. This can be obtained choosing appropriate materials and structures to implement the basic cells needed in this technology, leading to different types of QCA, like metallic QCA [3], semiconductor QCA [4] or molecular QCA [5–7]. Metallic QCA were the first practical implementation of the QCA principle, but they work only at temperatures near absolute zero. The same thing applies also to semiconductor QCA, which use a complex semiconductor structure as the basic cell. Molecular QCA instead use the charge stored in complex molecules to represent logic values, they can work at room temperature and at very high speed. Another possibility is instead to use rectangularly shaped magnets as the basic cell, as shown in Fig. 1. If magnet sizes are reduced to the nanoscale level, around 50–100 nm, they are forced into the single domain condition and their hysteresis cycle changes as shown in Fig. 1. The consequence is that, at the equilibrium, only two states are possible and therefore they can be used to represent logic values ‘0’ and ‘1’. This particular QCA implementation is then called NanoMagnet Logic (NML) [8–10]. The characteristic of NML logic is that devices work at room temperature and they can be fabricated with currently available technological process. As a consequence very advanced experimental activity is going on with it [11–13]. Since NML circuits are based on magnets, they have some specific advantages over other QCA implementations. They have no static power consumption and potentially a very low dynamic power absorption. They have an high heat and radiation resistance, making them ideal for hard environment applications. Finally, due to their magnetic nature, they combine logic and memory in the same device, opening up completely new possibilities in the development of logic circuits. Their only disadvantage is that they work at relatively low speed, around 50–100 MHz [14].

In NML technology, as it happens in general for QCA, circuits are built placing cells on the same plane. Information propagation and logic computation are caused by magnetic interaction between neighbor cells. For example in Fig. 2(A) a NML wire is shown. Magnets are aligned horizontally and they align antiferromagnetically to reach the minimum energy state. Since every magnet is in the opposite state of its neighbors, an inverter can be simply built making a wire with an odd number of magnets (Fig. 2(B)). The basic logic gate available on this technology is the majority voter, shown in Fig. 2(C). It is a three inputs gate where the value of the central magnet is equal to the majority of the inputs. While this gate coupled with the inverter allows to design any kind of logic function, its asymmetry may cause errors in the signal propagation as shown in [15, 16]. However, it is possible to expand the logic set available implementing two inputs AND/OR gates, that are shown in Fig. 2(D). Changing the shape of the central magnet gives it a preferential state, so that only when both magnets are up or down they are able to influence the central magnet [17].

Unfortunately the magnetic field generated by a magnet is not strong enough to switch its neighbors. As a consequence an external mean, like an external magnetic field, is necessary to help magnets switching [18–20]. Considering for example the simple QCA wire of Fig. 3(A), if only the input magnet is switched from ‘1’ to ‘0’ (Fig. 3) the second magnet will remain in the same state without switching. However an external magnetic field can be applied to force the other magnets in the RESET state (Fig. 3(B)). The RESET state is an unstable state so, when the magnetic field is removed, the first magnets will switch according to the input element, while the other magnets will remain temporary in the RESET state (Fig. 3(C)). Magnets will therefore switch one by one (Fig. 3 from (D) to (E)) with a domino-like effect, therefore propagating the new input value.

As demonstrated in [21, 22] only a limited number of magnets can be cascaded without errors generation during the realignment phase. Consequently, in order to build complex circuits a multiphase clock system must be used. Circuits are divided in small areas, called clock zones, each of them made by a limited number of magnets. At each clock zones a different clock signal is applied. For example in Fig. 4 a 3 phase clock system is depicted. Each clock zone is subjected to one of the three clock signals showed in Fig. 4(A). The clock waveform is always the same, but signals have a phase difference of \(120\,^{\circ }\). The circuit state evolution is showed in Fig. 4(B). When magnets belonging to a clock zone are in the SWITCH state, that means the magnetic field is slowly removed, magnets on the clock zone on their left are in the HOLD phase (no magnetic field applied) and act like an input. Magnets in the clock zone on their right are in the RESET state, so they have no influence on the signals propagation. Thanks to this mechanism signals propagate correctly in a specific direction.

Clocking mechanism for NML technology. (A) Starting from an initial configuration, (B) the value of the input element change and the other magnets are forced in the RESET state by an external mean, like a magnetic field. (C)–(F) When the magnetic field is removed magnets realign themselves following the input element, propagating therefore the information through the circuit.

3-phase clock system. (A) Clock signal waveforms. 3 clock signals, with a phase difference of \(120\,^{\circ }\), are used to assure a correct signals propagation. (B) Detailed signal propagation through a simple NML wire. When magnets of a clock zone are switching (SWITCH) magnets on their left are in the HOLD state and act as an input, while magnets on their right are in the RESET state so they have no influence.

NML clock systems. (A) Magnetic field clock. A magnetic field is generated by a current flowing through a wire placed under the magnets plane. (B) Out-of-plane NML clock. In this particular implementation of NML, the magnetization of each dots points out-of-plane. In this case the clock is an oscillating magnetic field applied perpendicularly to the plane. No clock zones are present because clock field is applied uniformly to the entire circuit. (C) STT-current clock. Spin-Torque coupling due to a current flowing through the magnets, which in this case are MTJ junctions. (D) Strain based clock. Magnets are forced in the RESET state through a mechanical deformation.

1.1 Comparison of Main Clock Solutions

Clocking is the most important feature of NML circuits, giving them a characteristic pipelined behavior [23–25] that represents a considerable source of problems. The most important of these problems is power consumption. While the intrinsic power consumption of NML circuits is extremely low [18] the losses in the clock generation system can be quite high, wiping out one of the major advantages of NML technology.

Different clock systems have been proposed. The first of this mechanisms is shown in Fig. 5(A). A magnetic field directed along the shorter magnets side is generated by a current flowing through a wire placed under the magnets plane. The wire, made of copper, is buried in a ferrite yoke to obtain a better distribution of the magnetic flux lines. This system works and it has already been theoretically demonstrated [26], however its power consumption is very high. In [11] a current of 545 mA on a wire \(1\,\upmu \mathrm{m}\) wide was necessary to successfully reset magnets. A magnetic field is also used in another NML implementation, called Out-of-Plane NML [27], where magnets are made by Cobalt-Platinum structures and the magnetization lies perpendicularly to the plane. In this case the magnetic field is perpendicular to the plane (Fig. 5(B)). A different approach uses instead STT-coupling with a current flowing through the magnets as clock mechanism (Fig. 5(C)). The basic element in this case is a Magneto-Tunnel Junction (MTJ) and wires are used to contact them and to drive the current [28, 29]. This solution as the remarkable advantage that is based on the Magnetic RAM memories structure, a technology that is already commercially available, moreover the value of clock current required is lower than in the magnetic field approach. Unfortunately all current based clock systems have a relatively high power consumption, mainly due to the Joule losses in the clock wires. A different solution was proposed in [30, 31] and it is shown in Fig. 5(D). Magnets are multilayer structures made by a piezoelectric layer and a magnetic layer, and they can be forced in the RESET state applying a proper electric field to them. The use of an electric field allows an important reduction of the losses in the clock generation system obtaining therefore true low power operations.

2 Electric Control of Magnetic Circuits

It is clear from the analysis presented in Sect. 1.1 that to obtain a true low power system NML circuits must be controlled with an electric field, therefore with a voltage, instead of using currents or magnetic fields. To control the magnetization of a material through a voltage the easiest way is to exploit the magnetoelastic effect. The magnetoelastic effect is a physical property of magnetic materials that bonds the magnetization with a mechanical stress. A mechanical stress of proper intensity and direction can change the magnetization of a magnetic material. The solution presented in [30] and reported in Fig. 5(D) is based on the magnetoelastic effect. When an electric field is applied to the dots the piezoelectric material is strained inducing therefore a mechanical stress on the magnetic layer. However, some problems arise with that solution. The first problem is related to the piezoelectric layer. We have a good experience about the fabrication of piezoelectric films, both for MEMS applications [32] and not [33], and we can say that it is not easy to obtain piezoelectric films of just 40 nm, as proposed in [30]. Moreover the surface of piezoelectric films is normally quite rough. The second problem arises with magnets sizes. In-plane NML circuits rely on the shape anisotropy, which is a properties of magnetic materials. Shape anisotropy depends on magnets shape, particularly one magnets side must be bigger than the other to obtain a stable enough magnetization. Moreover shape anisotropy also influences the energy necessary to force magnets in the reset state. The lower the magnets aspect ratio (the ratio between the longer and the shorter magnet side) is, the lower is the reset energy but also the stability of the magnets when they are in one of the stable states. In [30] magnets are \(99\times 101\,\mathrm{nm}^2\), but with the best currently available fabrication processes it is quite difficult to obtain a resolution of just 1 nm. Moreover, with those sizes the tolerance toward process variations will be very low. The consequence is that, with a so low magnets aspect ratio, any kind of fabrication error or defect would drastically change the magnetic anisotropy. As a result magnets would be unstable, if the aspect ratio is reduced, or it would be impossible to force them in the reset state, if the aspect ratio increases. Finally, in [30] no feasible system to generate and distribute the electric field is proposed. Furthermore, while the power consumption estimated is quite low, it does not take into account the losses in the clock distribution network.

Magnetoelastic clock system for NML logic. (A) Electrodes are placed on top and on the bottom of the piezoelectric layer. The electric field and the piezoelectric substrate are coupled through the \(\mathrm{d}_{31}\) coefficient. Moreover electrodes interfere with the mechanical coupling and the magnets fabrication process. (B) Electrodes are placed on the side of the piezoelectric layer. The electric field and the piezoelectric substrate are coupled through the \(\mathrm{d}_{33}\) coefficient. Electrodes do not interfere with the mechanical coupling and magnets fabrication.

The clock system here described is also based on the magnetoelastic effect, however it is built around our experience with piezoelectric materials. The aim is to provide a clock solution where both the layout of NML circuits and of the clock distribution network are considered. We want to choose a solution that (i) takes into account the limitations of currently available fabrication processes, (ii) that allows to obtain a true low power circuit, considering also the losses in the distribution network. The idea is to take a piezoelectric substrate and to deposit magnets on top of it, as shown in Fig. 6. When an electric field is applied to the piezoelectric layer, it is strained and therefore a mechanical stress is induced on the magnets, forcing them in the RESET state. To generate the electric field it is sufficient to place two electrodes near the piezoelectric substrate and then to apply a voltage across them. They can be placed on top and on the bottom of the substrate (Fig. 6(A)) or at both sides of the substrate (Fig. 6(B)). The first solution was partially experimentally demonstrated in [34], successfully showing the magnetization control with an applied voltage. However, two problems arise when it must be applied to NML circuits. The generated electric field is perpendicular to the plane, while the strain of the piezoelectric layer is directed along the plane. The consequence is that the electric field and the strain are coupled through the \(d_{31}\) coefficient of the piezoelectric material. \(d\) coefficients are physical constants of piezoelectric materials that bond the mechanical stress and the applied voltage, as can be seen from Eqs. 1 and 2, that describe the mathematical theory behind the piezoelectricity.

Equations 1 and 2 are normally called coupled equations in the strain-charge form. They provide the link between the deformation and the electric field. \(S\) is the strain matrix and \(D\) is the electric charge matrix, \(s\) is the compliance (the inverse of the stiffness), \(T\) is the stress matrix, \(d\) is the matrix for the direct piezoelectric effect while \(d^t\) is the matrix for the converse piezoelectric effect, finally \(E\) is the electric field and \(\epsilon \) is the permittivity. The matrix of \(d\) coefficients therefore links the various components of the applied electric field to the resulting strain. The two most important \(d\) coefficients for this kind of applications are the \(d_{31}\) and the \(d_{33}\). When the applied electric field is perpendicular to the strain the \(d_{31}\) coefficient is used, while, when the electric field and the strain lie in the same plane and in the same direction, the \(d_{33}\) coefficient is instead used. \(d_{31}\) coefficient is normally smaller than the \(d_{33}\) coefficient.

The second problem is related to the electrodes placement. One of the electrodes is placed on top of the piezoelectric layer, between the piezoelectric material and the magnets, reducing the mechanical coupling between them. Moreover, considering the fabrication of a complex NML circuit, these electrodes must be contacted with wires to distribute the clock voltage, but this is difficult considering that electrodes are covered by magnets. In the second solution (Figure 6(B)) electrodes are placed at both sides of the piezoelectric layer, so the electric field and the strain lie along the same plane and are coupled through the \(d_{33}\) coefficient, which is higher than the \(d_{31}\) as can be seen from Table 1. The coupling between piezoelectric layer and magnets is stronger and electrodes can be contacted freely because there is no physical interference caused by magnets. We therefore choose this second structure to build our magnetoelastic clock system for NML technology.

Table 1 shows a comparison between some of the piezoelectric material most commonly used. \(d_{31}\) and \(d_{33}\) coefficients bond the mechanical strain with the applied voltage, and as can be clearly seen, \(d_{33}\) is normally higher than \(d_{31}\). \(Ef_{MAX}\) is the maximum electric field that the material can tolerate while \(\epsilon _r\) is the relative dielectric constant. PZT (Lead-Zirconate-Titanate) is one of the most commonly employed material and, as can be seen from Table 1, it has also the best performance. The other materials shown in Table 1 are PVDF, which is a polymer, Zinc Oxide (ZnO) and Barium-Titanate (BT), but they show worst performance than PZT, so in this work we use PZT as our reference choice for the piezoelectric substrate.

2.1 Magnetic Material Choice

While there is little room for different choices of piezoelectric material, the selection of the magnetic material to be used is more complex. The reason behind this fact lies in the limited amount of mechanical stress that can be applied to the magnets. In current-based clock systems there is virtually no limit to the amount of current that can be supplied to the circuit. There is indeed a limit to the value of current that can be used but it is very high, as shown in [11] where a current of 545 mA is used to generate the magnetic field. In this clock system, instead, the maximum stress that can be applied to the magnets is quite limited. The reason is simple: If the mechanical stress is to high there is a mechanical damage on the structure. To evaluate the maximum stress that can be used, two contributions must be considered, the contribution of the piezoelectric substrate and the contribution of the magnets.

Since the piezoelectric material is an insulator, there is a maximum value of electric field that can be applied without breaking it. As a consequence the maximum strain that it is possible to have is given by Eq. 3.

\(Ef_{MAX}\) is the maximum electric field tolerated by the piezoelectric substrate, while \(d = d_{33}\) is the longitudinal piezoelectric coefficient that relates the strain induced with the applied voltage. As can be seen from Table 1, PZT is one of the material that can tolerate the highest values of electric field, bigger than 50 MV/m. However, structural limitations of the piezoelectric materials must be considered, because, also if the applied electric field is lower than the maximum tolerated, the generated strain can be bigger than the maximum strain due to material structural limitations (\(\xi _{MAX\_STRUCT}\)). As a consequence, the maximum strain of the piezoelectric material (\(\xi _{MAX})\)) is the minimum between these two contributions, as shown in Eq. 4.

PZT has a very high tolerance to structural deformations, because \(\xi _{MAX\_STRUCT}\) is equal to \(500\cdot 10^{-6}\) [35], so the lower bound is due to the maximum electric field that can be applied. Once the maximum strain tolerated by the piezoelectric material is evaluated, it can be converted to a stress as shown in Eq. 5:

Multiplying the maximum value of strain (\(\xi _{MAX}\)) for the Young modulus (\(Y_{Magnet}\)) of the magnetic material gives the maximum stress that can be applied to the magnets (\(\sigma _{MAX\_PIEZO}\)). This assumption is valid only if the thickness of the magnetic material is much smaller than the thickness of the piezoelectric substrate, because only if this condition is satisfied the mechanical stress generated by the substrate is completely transferred to the magnets. Table 2 shows the comparison between some magnetic materials, where the Young modulus is in the range of 80–209 GPa.

To complete the analysis the value of maximum stress previously evaluated (\(\sigma _{MAX\_PIEZO}\)) must be compared with the maximum stress that can be tolerated by the magnetic material (\(\sigma _{MAX\_STRUCT}\)). The maximum stress that can be applied to the circuit is therefore the minimum between these two values of stress as shown in Eq. 6.

Between these two values, the lower bound is normally given by the maximum structural stress that can be tolerated by the magnetic material (\(\sigma _{MAX\_STRUCT}\)). As can be seen from Table 2 this value is in the range of 28–540 MPa.

Once that the maximum stress is evaluated, the next step is to understand the minimum stress that must be applied to the magnets to force them in the RESET state. The minimum stress can be evaluated considering two important properties of magnetic materials: Shape and stress anisotropy. The value of shape anisotropy is related to the sizes and aspect ratio of magnets and can be evaluated as shown in Eq. 7.

where \(\mu _0\) is the magnetic permeability, \(N_d\) is the demagnetization factor, \(M_s\) is the magnetization saturation and \(V\) is the volume. Stress anisotropy is instead related to the applied mechanical stress and can be evaluated as shown in Eq. 8.

where \(\lambda _s\) is the magnetostrictive coefficient of the magnetic material, \(\sigma \) is the applied stress and \(V\) is the volume. The minimum stress is therefore the value of stress that generates a stress anisotropy at least equal to the shape anisotropy and can be calculated equaling Eqs. 7 and 8, as shown in Eq. 9.

Once the minimum and maximum stresses that can be applied are know, it it possible to analyze different magnetic materials and to understand which of them is suited for this kind of application. The analysis is performed using Octave, evaluating how the minimum stress changes with magnet sizes. Since in NML circuits magnets are either \(50\times 100\,\mathrm{nm}^2\) or \(60\times 90\,\mathrm{nm}^2\), the shorter magnet side is chosen equal to 50 nm, and the longest magnet side is changed from 50 nm to 100 nm, changing therefore magnets aspect ratio (from 1 to 2). Magnets thickness is chosen equal to 10 nm, to obtain the maximum mechanical coupling between the substrate and the magnets. Minimum and maximum stresses are therefore evaluated for these values of magnet sizes. Figure 7 shows the results of the analysis for two common magnetic materials, Iron and Cobalt.

To assure the magnets stability in presence of thermal noise the value of shape anisotropy must be at least equal to \(30K_bT\), as shown in Eq. 10, generating therefore a lower bound on the value of aspect ratio:

The minimum value of aspect ratio that assures thermal stability is equal to 1.06, that means magnets must be at least \(50\times 53\,\mathrm{nm}^2\). However from Fig. 7 it is possible to see that either Iron (Fig. 7(A)) or Cobalt (Fig. 7(B)) cannot be used for this application. The value of minimum stress is always bigger than the maximum applicable stress.

Things are different if high magnetostrictive materials are considered. Figure 8 shows the analysis results applied to nickel and terfenol. Terfenol is an alloy of Terbium, Disprosium and Iron. As can be seen Nickel shows a sizes range where the minimum stress is effectively lower than the maximum applicable stress. The maximum aspect ratio is 1.28, that is equal to magnets of \(50\times 64\,\mathrm{nm}^2\). Terfenol shows better performance, since the maximum aspect ratio is 1.57 that means magnets of \(50\times 78\,\mathrm{nm}^2\). It appears that Terfenol is the best choice for this application.

2.2 Process Variations

To better understand which of the two proposed materials, Nickel and Terfenol, is the best candidate for this application, the impact of process variations must be evaluated as well. The same analysis done before was repeated considering a random variation on the shorter magnets side, previously considered fixed at 50 nm. Figure 9 shows the results. With a process variation of \(\pm 5\) % nickel still shows a good working range (Fig. 9(A)) but with a variation of \(\pm 10\) % there is just one value of aspect ratio where magnets can be successfully reset (Fig. 9(B)). Clearly with bigger variations, like a \(\pm 20\) % variation, there is no working range. Better results are obtained for terfenol because with a variation of \(\pm 5\) % (Fig. 9(D)) and \(\pm 10\) % (Fig. 9(E)) it still shows a good working range. Also considering a variation of \(\pm 20\) % (Fig. 9(F)) there is still a value of aspect ratio in which magnets can be successfully reset.

The consequences are blatant, Terfenol can tolerate higher process variations than Nickel, making it the best candidate for this application, and it is therefore used as a reference for the results presented in this chapter. The chosen magnet sizes are \(50\times 65\times 10\,\mathrm{nm}^3\), with an height of 65 nm, correspondent to an aspect ratio of 1.3, which is exactly in the middle of terfenol working range. These sizes give therefore the best tolerance to process variations.

2.3 Building Circuits

To design a generic NML circuit the clock zones layout must comply with two important requisites:

-

It should allow signals propagation in every direction.

-

It should take into account the physical constraints of the clock generation network, i.e. the fabrication and physical placement of the wires used to route currents or voltages required to implement the multiphase clock system used.

To comply to these rules the NML circuit design chosen for this particular clock system is based on NAND/NOR gates, since they are universal gates that can implement any kind of logic function. Figure 10 shows the layout of NAND gate. A NOR gate can be simply obtained changing the shape of the central magnet [17].

NAND gate layout. A NAND can be obtained coupling a AND gate [17] with an inverter, which is simply made by an odd number of magnets horizontally aligned.

Every clock zone is made by a mechanical isolated island of piezoelectric material. Magnets are deposited directly on top of the piezoelectric layer to maximize the mechanical coupling. A NAND gate can be built coupling a AND gate [17] with an inverter, which is simply built by an horizontal wire with an odd number of magnets. Helper blocks [36] are used to help the signal propagation in presence of vertical NML wires. Every gate has two inputs and can have up to two outputs as outlined in Fig. 10.

Electrodes placement. Cell is 350 nm width and the piezoelectric layer is 100 nm thick, while the electrodes section is \(50\times 50\,\mathrm{nm}^2\) (A) Electrodes are buried under the piezoelectric layer. (B) The electric field distribution is quite uniform between the electrodes (3–4 MV/m with an applied voltage of 1 V) but is lower near the area correspondent to the electrodes. The strain is proportional to the electric field value. (C) The electric field lines are quite uniform. (D) Electrodes placed on top of the piezoelectric island. (E) The distribution is still uniform but the electric field this time is higher near the two electrodes. (F) Also with this structure the electric field lines have a good uniformity.

Theoretically, the electrodes should be placed at both sides of the piezoelectric island, as shown in Fig. 6(B). However, this makes the fabrication process more complex. A first possible solution is to use electrodes placed at both sides of the piezoelectric island but buried under it (Fig. 11(A)). The fabrication of electrodes under the piezoelectric layer, however, is complex. The processes involved in the fabrication of piezoelectric materials works at very high temperature and they can therefore damage the electrodes, since the PZT is created on top of them. Moreover, if Copper is used to fabricate the electrodes, an interface layer is required to stick together electrodes and PZT. Figure 11(B) shows a simulation of the electric field distribution, obtained through Comsol Multiphysics [37], of the structure with buried electrodes. The structure is 350 nm width, the PZT is 100 nm thick and electrodes are \(50\times 50\,\mathrm{nm}^2\). As can be seen the electric field is quite uniform between the two electrodes (3–4 MV/m with an applied voltage of 1 V) but it is lower near the area correspondent to the electrodes and it it 0 directly above them. The strain of the material depends on the electric field value, so it will be higher in the area between the electrodes and lower above them. Thanks to the mechanical continuity of the island, there will be a strain also where the electric field is 0, because, intuitively, the strain of the central part of the island will induce a strain also near the border of the island. Electrodes are not exactly placed at the island sides, however, as can be seen from Fig. 11(C), the electric field lines distribution is quite good between the two electrodes, with lines almost parallel to the surface.

A second solution is to deposit the electrodes on top of the piezoelectric island, as shown in Fig. 11(D). This solution is technology-friendly, because the PZT is fabricated before the electrodes, so they are not damaged by the high temperature processes involved in the PZT fabrication. Moreover, no interface layer is needed between the electrodes and the substrate. Considering also the global circuit layout, electrodes placed on top of the substrate are easier to contact. Interconnection wires used to connect the electrodes can be fabricated using additional layers, in the same ways as CMOS interconnections. This solution is therefore compatible with CMOS fabrication processes. Magnets are deposited on the islands after the deposition of the electrodes. This solution shows also a better electric field distribution (Fig. 11(E)) than the buried electrodes one. The electric field is still uniform between the electrodes, moreover near the borders its intensity increases. Figure 11(F) shows the electric field lines, similarly to the previous case they are quite uniform, especially near the surface which is the most important part. Since the use of electrodes on top of the island shows a better electric field distribution and is compatible with CMOS fabrication processes, this is the solution adopted hereinafter for this particular clock system.

Two possible sizes for the gates. (A) Gates can be 5 magnets width, simplifying the fabrication processes because the structure is bigger. Performance are however worse because there are more magnets in the critical path. (B) The minimum gate width is equal to 3 magnets to grant a proper signal propagation. Performance are better but higher resolution lithography processes are required.

The electrodes placement is the reason behind the choice of using AND/OR gates as basic logic gates, instead of using majority voters. Majority voters are three input gates (see Fig. 2(C)) where two inputs come from up and down directions and the central one comes from left direction. The use of a majority voter with this clock system is therefore not possible, because at the left of the gate there is one of the electrodes. However AND/OR gates has only two inputs coming from up and down directions, so there is no interference with the electrodes. Moreover they are smaller than a majority voter reducing the circuit area.

The minimum height of the gate is equal to 3 magnets, whilst the width can be equal to 5 (Fig. 12(A)) or 3 magnets (Fig. 12(B)). With 5 magnets the whole structure is bigger, therefore it is simpler to fabricate. Performance are worse because there are more magnets on the critical path and therefore the clock frequency is lower. Furthermore the structure is bigger, so the clock losses are bigger. See Sect. 2.4 for further details on performance. With a width of just 3 magnets performance are improved but fabrication processes with higher resolution are required. Smaller widths cannot be reached because the required resolution cannot be achieved with current technological processes. Bigger values of width are also not possible because bigger structures have far too many magnets in the critical path, generating therefore errors in the signal propagation.

Figure 13 shows a possible layout of a NML circuit based on this clock solution. Every piezoelectric island is equal to a clock zone. Particularly, the layout is made by interleaved lines of clock zones to correctly match the outputs coming from a clock zone with inputs of neighbor clock zones. Due to the presence of electrodes, signals propagation follows the north and south border of every clock zone. A clock zone then can be occupied by a logic gate or simply by a wire. Finally, a proper multiphase clock scheme can be applied to the layout to obtained a correct signals propagation.

The layout here proposed is based on mechanical isolated islands. To obtain islands of PZT starting from a uniform substrate, it can be patterned through lithography, selectively removing part of the piezoelectric material in a specific area [38, 39], as shown in Fig. 14. PZT can be completely removed to obtain perfect isolation, however also removing just a small part of it provides a very good mechanical separation, so that the strain of an island does not produce a strain in neighbor cells. This is an important requisite in every clock system: When magnets of a specific zones are clocked there should be no crosstalk with their neighbor clock zones. Clearly the higher the resolution of the lithography process used is, the smallest the area that can be removed is. Theoretically, a gap of few nanometers (providing to have a process with high enough resolution) is sufficient, since the strain of every island is smaller than 1 nm.

2.4 Performance: Timing and Power Estimation

Recently a dedicated simulator for NML technology, ToPoliNano, was developed [40, 41]. While this tool represents a powerful instrument to automatically generate [42] and simulate NML circuits [43], it does not support low level physical simulations. To evaluate timing performance of NML circuit it is instead possible to use low level physical simulators like OOMMF [44], NMAG [45] or Magpar [46]. These finite element simulators are based on the Landau-Lifshitz-Gilbert (LLG) equation which describes the dynamic behavior of a generic magnetic structure. Among these simulators Magpar allows also the evaluation of an applied stress on the circuit dynamic. As a consequence, to understand the timing behavior of the proposed clock system, a NML wire was simulated with Magpar. Magnet sizes and the value of applied stress are taken from the theoretical analysis described in Sect. 2.1.

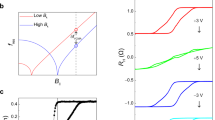

Figure 15 shows the simulation results obtained. The reset time, the times required for a magnet to rotate its magnetization vector from one stable state to the RESET state, is around 1 ns (Fig. 15(A)). The switching time, the time required for a magnet to go from the RESET state to one of the stable states, is slightly smaller but also in this case it is near 1 ns. This numbers can be used to estimate the circuits clock frequency. It can be said that in the best case the clock period must be at least equal to (Eq. 11):

\(T_{RESET}\) is the reset time, \(T_{SWITCH}\) is the switching time and \(N\) represents the number of magnets in the critical path. The critical path is the total number of magnets in a clock zone between an input to the output. In case of a NAND gate with a width of 3 magnets, \(N\) is equal to 5, therefore the correspondent clock frequency is 160 MHz. In case of a NAND gate with a width of 5 magnets, \(N\) is equal to 7, so the clock frequency is 125 MHz. Nonetheless, the evaluation of the real clock frequency is more complex as different factors must be considered. For example, the total switching time is not directly the sum of the switching time of every magnet, because one magnet starts to switch before its neighbor has completed the switching. The clock period is therefore lower and the frequency higher. As a consequence the upper bound for the clock frequency can be estimated in 200 MHz for gates with a width of 3 magnets and 150 MHz for gates with a width of 5 magnets. Anyway this is just an upper bound as the real clock frequency must be evaluated according to the multiphase clock scheme selected, and it is consequently partially independent from the clock technology itself. The clock frequency changes accordingly to the clock scheme selected, for example with a 3 phase clock [47, 48] the frequency will be lower than a 2 phase clock [17]. For this reasons no further details are given on the clock frequency value because out of the scope of this chapter.

Albeit timing is a crucial point, the most important parameter that must be evaluated is the power consumption. Two contributions must be considered: The intrinsic energy consumption required to force magnets in the reset state, and the looses in the clock generation network. The intrinsic energy consumption is equivalent to the height of the energy barrier between stable and reset states. If an adiabatic switching is used, that means a very low rise time for the clock signal, this value of energy consumption is reduced to \(30K_bT\). In case, on the contrary, an abrupt switching is used, that means a rise time for the clock signal as short as possible, this value of energy consumption is equal to the entire energy barrier. With magnetic field-based NML circuits, the value of energy barrier can be very high (thousands of times \(K_bT\) [16]) so there is a big difference between adiabatic and abrupt switching. In this case with magnets of \(50\times 65\times 10\,\mathrm{nm}^3\) the energy barrier is just about \(180K_bT\), so an abrupt switching is used, because it allows to maximize performance.

This can be done because the intrinsic energy consumption is very small compared to the second source of losses, i.e. the energy loss in the clock generation network. The biggest contribution to this term of energy consumption is the energy required to charge the capacitor. Since piezoelectric materials are insulators, every NAND/NOR gate is equivalent to a capacitor (an insulator embraced by two electrodes). The capacitance can be estimated as shown in Eq. 12.

where \(\epsilon _0\) is the absolute dielectric constant, \(\epsilon _r\) is the relative dielectric constant of the piezoelectric material, \(t_{PZT}\) is the thickness of the piezoelectric substrate while \(h_{NAND}\) and \(w_{NAND}\) are the NAND/NOR gate height and width. The voltage that must be applied to every gate can be calculated as in Eq. 13.

where \(\sigma \) is the applied stress, \(Y\) is the Young modulus of the magnetic material and \(d_{33}\) is the coefficient that couples the strain and the applied voltage in the piezoelectric substrate. With this gate sizes and materials, the required voltage is normally in the range of 0.7–1.3 V. The energy required to charge the capacitance is then (Eq. 14):

The bigger it the capacitance, the bigger is the energy consumption. The capacitance depends on the physical size of the NAND/NOR gate, like the height and the width of the island, and in particular it is directly proportional to the piezoelectric layer thickness. Nevertheless, while physical sizes do not depend on the particular piezoelectric material used, this is not true for the relative dielectric constant (\(\epsilon _r\)). The capacitance depends directly on the value of \(\epsilon _r\), so the bigger it is the bigger the energy consumption is. As can be seen from Table 1 the PZT \(\epsilon _r\) is quite high, so if this material is used power consumption is expected to be higher. This is probably the only real flaw of PZT used for this application. Finally, the value of voltage to be applied depends both on the width of the island and on physical properties of magnetic and piezoelectric materials used.

(a) Comparison between energy consumption components for a \(3\times 3\) NAND/NOR with magnet of Terfenol. Energy required to reset the magnets is constant and much lower than energy lost to charge the capacitor. (b) Comparison between NAND/NOR with different sizes and different materials. Nickel has an overall lower energy consumption due to a higher Young modulus.

Since the geometrical characteristics of every island are determined by logic constraints (i.e. the number of magnets in the critical path and the structure of AND/OR gates) and materials are chosen as explained in Sect. 2, the only remaining free parameter is the thickness of the piezoelectric layer. Figure 16 indicates the total energy required to switch a NAND/NOR gate, showing the variation with the PZT thickness. Figure 16(a) highlights the difference between the energy consumption and the clock losses in a \(3\times 3\) NAND/NOR gate with magnets made of Terfenol. The intrinsic energy consumption is constant with different values of PZT thickness, because it depends only on the magnets characteristics. The clock losses increase instead linearly with the PZT thickness and most important, they are much bigger then the intrinsic energy loss (11000 \(K_bT\) against 1400 \(Kb_T\) with a PZT thickness of 40 nm). To be fair also the losses due to Joule effect should be considered, however, since piezoelectric materials are insulators, the value of current is so small that the resulting losses are 7–8 orders of magnitude smaller than the energy required to charge the capacitance, that is the only really important source of energy loss. Moreover, the distance between electrodes is quite big so no relevant tunnel current can be expected.

Figure 16(b) shows instead a comparison between the total energy consumption with gates of different sizes, \(3\times 3\) and \(3\times 5\) (that means an height of 3 magnets and a width of 5 magnets), and considering both terfenol and nickel as magnetic materials. As can be clearly observed gates with a width of 5 magnets have a bigger energy consumption than gates with a width of 3 magnets. This is expected because with a bigger width the capacitance is smaller while the voltage is bigger. From Eq. 14 it is evident that voltage has a bigger impact compared to the capacitance, so reducing the capacitance and increasing the voltage overall increases the energy consumption. What is partially unexpected is that, changing the magnetic material employed changes the total energy consumption. As can be seen from Fig. 16(b), using Nickel leads to a lower energy consumption. This can be explained looking at Eq. 13. Nickel magnets require a bigger stress, nonetheless their Young modulus is also bigger, so overall the required voltage and the energy consumption are lower. While Nickel shows a reduced power consumption, Terfenol remains the privileged choice for its better tolerance to process variations.

PZT thickness is an important parameter that must be chosen carefully considering both energy consumption requirements and technology limitations. With magnets 10 nm thick the minimum thickness for the PZT substrate is 40 nm. The PZT must be much thicker than the magnets to be sure that the mechanical stress is completely transferred from the substrate to the magnets. Increasing the thickness of the piezoelectric layer generally improves the material piezoelectric properties and simplifies the fabrication process at the cost of improved energy consumption.

Finally a comparison between different NML clock solutions and CMOS technology is presented in Table 3, comparing the total energy consumption of a NAND gate. In case of magnetic field clock (I in Table 3) an adiabatic switching is considered, therefore the intrinsic energy consumption of each magnet is assumed equal to 30\(K_bT\). Clock wires are made of copper and have a section of \(400\times 400\,\mathrm{nm}^2\), with a length of 200 nm. The current value used is extrapolated from the experimental data shown in [11] and is assumed equal to 2 mA. With these values the total energy consumption is 62 fJ. For the STT-current clock (II in Table 3) the energy consumption is assumed equal to 1.6 fJ for each magnet [28], for a total of 11 fJ. In case of a pure multiferroic logic (III in Table 3), data shown in [30] assume a power consumption of 0.004 fJ for a NAND gate. With the clock solution here proposed the energy consumption in case of a \(3\times 3\) terfenol NAND gate is equal to 0.052 fJ (IV in Table 3). This value is orders of magnitude better than current-based clock systems. A comparison with a pure multiferroic approach is not possible because the data reported in [30] do not take into account the energy loss in the clock generation network. A comparison among the different clock solutions applied to a complex circuit is shown in [49], where a NML circuit for biosequences analysis [50, 51] is presented. The advantage of this clock solution in terms of power consumption is plain.

An important fact must be highlighted. From a circuital point of view every mechanically isolated island is equivalent to a capacitor. As a consequence it is possible to set up an appropriate RLC resonant circuit to recover the energy used to charge the capacitance, reducing the NAND gate energy consumption from 0.052 fJ to 0.006 fJ (V in Table 3). Due to the presence of a parasitic resistance it is not possible to completely recover the energy, nonetheless it is still possible to obtain a good energy consumption reduction. This is particularly important if higher thickness values must be used for the PZT substrate to improve the piezoelectric properties. With higher thickness values the energy consumption is bigger, but it can be compensated by recovering it with setting up a RLC resonator. Considering instead a CMOS NAND gate (VI in Table 3) data extrapolated from ITRS roadmap indicates an energy consumption of 0.110 fJ for the 21 nm technology node. If adiabatic techniques to recover the dynamic component of the energy consumption are used in conjunction with CMOS, only 0.040 fJ are required to switch a NAND gate (VII in Table 3), mainly due to the presence of leakage currents. In both cases our solution shows a remarkable advantage over state of the art CMOS transistors and other NML clock systems in terms of energy consumption.

3 Experimental Fabrication

We are currently experimentally validate the proposed clock solution. Our aim is the demonstration of the working principle but also the characterization of the structure in terms of power consumption. To enrich the explanation we also present here a brief discussion on piezoelectric and magnetic materials required by this clock system.

3.1 Piezoelectric Materials

Due to the fundamental role played by piezoelectric material in this clock system, here an in-depth analysis of their state-of-the-art is presented. Moreover an insight on the fabrication techniques commonly employed and the problematics related to the dimensions scaling is given.

With the advent of the micro and nanotechnologies the development of MEMS based on piezoelectric materials has gained growing and growing importance in the world of scientific research and a lot of attention is currently devoted to the study of such materials. The possibility of combining piezoelectric sensors and actuators with silicon-based CMOS technology, and to integrate them into smart structures, allowing the implementation of a new class of devices which integrate sensors and operate autonomously, converting mechanical energy into dielectric displacement [52, 53].

Among all functional ceramics, lead zirconate titanate (Pb(Zr1-xTix)O3, PZT) attracted considerable attention thanks to the presence of excellent ferroelectric and piezoelectric properties, becoming one of the most studied materials of the last decade. It consists of a solid solution of lead titanate and lead zirconate, which can be present in different relative quantities. Piezoelectricity and ferroelectricity of PZT are strictly related to the presence of a perovskite crystal structure. The symmetry of the perovskite phase depends on the stoichiometry of PZT, which influences also its electrical, dielectric, piezoelectric and ferroelectric properties. A titanium-rich phase is responsible for the presence of the tetragonal cell while a zirconium-rich composition gives rise to the presence of a rhombohedral phase. It has been shown that there exists a particular value of the ratio Zr/Ti for which the piezoelectric and ferroelectric properties are maximized [53–56].

This condition is known as the morphotrophic phase boundary (MPB). When Zr/Ti is around 53/47 the MPB is present and the dielectric/piezoelectric response of the material and its ferroelectricity are enhanced [57, 58]. Different works show that the piezoelectric constant d33, as well as permittivity and ferroelectricity, can reach their maximum values near the MPB condition [59]. In particular, it is reported that the (100)-oriented rhombohedral phase is expected to have excellent piezoelectric properties [58]. The transition between a centro-symmetrical paraelectric cubic phase and a non-centro-symmetrical ferroelectric tetragonal one is also related to temperature, occurring at a particular value, the so called Curie temperature (TC). For PZT TC is around \(300\,^{\circ }\mathrm{C}\) [60]. Piezoceramic bulk materials for the realization of MEMS/NEMS based technology must be used in the form of thin films. Generally, sputtering and sol-gel are the most diffused techniques for the deposition of PZT thin films. Independently of the deposition technique, the selection of the substrate material is quite deleterious for both electrical and piezoelectric properties of PZT. Generally polycrystalline PZT films can be simply grown using non-epitaxial Si substrates, in order to get the monolithic integration of PZT thin films in the Si-based technology. It is also reported that the epitaxial growth on substrates like MgO or SrTiO3 has to be preferred to enhance the piezoelectric response of the material [59].

However, large residual stress, either compressive or tensile, in the order of some MPa can arise, affecting the physical properties of the material itself [59, 61, 62]. Sufficiently thick and crack-free PZT films have been fabricated and their applications in MEMS devices have been fully demonstrated [63, 64]. Ferroelectric PZT thin films are also widely used in the study and fabrication of nonvolatile ferroelectric random access memories (FeRAM) while the strong piezoelectric response of PZT, in accordance with the presence of high electromechanical coupling coefficients, is exploited in the realization of sensors and actuators, especially for acoustic applications, where large piezoelectric coefficients and electromechanical coupling factors are preferred. Especially in the field of ultrasonic imaging, where transducers operating at frequencies comprised between 20 and 50 MHz are required, PZT films have been recently used and transducers operating at 20 MHz have been demonstrated [65, 66]. Furthermore, good electrical properties, i.e., a high dielectric constant and a strong dependence of the dielectric constant on the DC bias field, in accordance with ferroelectricity, makes PZT a good candidate for the realization of microwave devices applications, like voltage-controlled oscillators, varactors, delay lines and phase shifters [57].

Even though PZT is the most performing piezoceramic, thanks to its high piezoelectric constant, recently lots of efforts have been devoted to the study and development of innovative, non toxic, lead-free piezoelectric materials. Among them zinc oxide (ZnO), barium titanate (BT) and aluminum nitride (AlN) are by far the most studied. Zinc oxide is a lead-free, pyroelectric, piezoelectric, wide band-gap semiconductor (3.37 eV) with a large exciton binding energy (60 meV) at room temperature and a wurtzite hexagonal structure. It can be synthesized both in the form of dense thin films and different kinds of nanostructures (nanowires, nanobelts, nanorods, nanocombs) by physical vapor deposition techniques like sputtering, pulsed laser deposition, atomic layer deposition, chemical vapor deposition, hydrothermal growth and sol-gel techniques. It has been demonstrated that ZnO can be successfully used for the realization of photodetectors, light-emitting diodes, and chemical sensors while the presence of piezoelectricity [67] makes ZnO suitable for the realization of surface acoustic wave resonators, nanogenerators and touch-sensitive piezoelectric sensors. However, as semiconductor ZnO has some advantages and a high electrical resistance, high breakdown voltages and consequently suffers from high electrical losses. Some of these problems, together with its poor piezoelectric properties, can be solved by properly doping ZnO. Aluminum nitride (AlN) can be used in place of ZnO, thanks to its high electrical resistance, high breakdown voltage and low dielectric loss [68–70]. Despite its smaller piezoelectric constant, [67] a lower dielectric permittivity respect to the one of PZT makes AlN competitive in the realization of MEMS devices. Similar to PZT, barium titanate belongs to the class of perovskite-based materials. The presence of a non centro-symmetrical tetragonal crystal structure at room temperature allows it to feature piezoelectricity. BT is a high dielectric material with a piezoelectric coefficient higher than those of ZnO and AlN [71]. As in the previous cases, also BT can be synthesized in different ways, both from physical and chemical vapor deposition methods, and by hydrothermal synthesis. The main problem of BT is the low TC, which is around \(120\,^{\circ }\mathrm{C}\) but can be increased by doping the material. A lot of work has to be done in order to improve ZnO, AlN and BT electromechanical properties to become comparable with the PZT ones. Despite all the recent developments in the synthesis of lead-free, non toxic functional materials, PZT still remains the best choice for the realization of sensors and actuators for the micro and nanotechnologies.

Fabrication of Bulk and Thin Film Electro-Ceramics. Ferroelectricity and piezoelectricity in ceramic materials were discovered in the early 1940s, after the observation of high dielectric constants in ceramic barium titanate capacitors [72]. From then, intensive studies have been done, especially about two compositional systems: barium titanate (BaTiO3 or BTO) and lead zirconate titanate (Pb[ZrxTi1-x]O3 where \(0\times 1\) or PZT) leading to many applications in medical ultrasonic, high deformation actuators, integrated circuits [73–76]. Some applications utilize chemical coprecipitation [77] or hydrothermal [78] techniques; however ferroelectric ceramics are traditionally obtained from powders formulated starting from individual oxides.

In the standard method for the fabrication of piezoelectric bulk ceramics, the key steps are calcination and sintering: during these steps there is a consistent redistribution of atoms in order to minimize the free energy of the system: new phases are created, the number of surfaces decreases and the grain size increases [79]. The fabrication process starts from the preparation of a specific composition in powder from the chosen precursors; then, the desired shape is created, before densification and finishing. The strong research and development activity in fuel cells, sensors, ferroelectric memories and MEMS technologies has stimulated efforts to fabricate electroceramic films of sub-micron thickness range.

The deposition techniques that allow growing thin films of ferroelectric materials can be divided into two main groups: physical vapor deposition (PVD); chemical processes involving chemical vapor deposition (CVD) and chemical solution deposition (CSD). PVD consists simply in removing atoms from a ceramic target and condensing the vapor onto a substrate. Sputtering technique is used for the deposition of ferroelectric thin films (oxides) because it is a relatively simple process, compatible with standard semiconductor processes; it has quite high deposition rates and good thickness uniformity [80]. Along with sputtering, very diffused is pulsed laser deposition (PLD), where short and intense laser pulses evaporate and ablate the surface of the target material. Metallorganic chemical vapor deposition (MOCVD) decomposes the gaseous precursors on a hot substrate to form a film of desired composition. MOCVD is one of the more promising methods for FeRAM applications (Ferroelectric Random Access Memories) because of its high deposition rate, good step coverage and conformal deposition on three-dimensional surfaces, uniformity of film composition and thickness over a large area, and compatibility with the standard semiconductor [80]. Still not so well established is molecular beam epitaxy (MBE). The chemical solution deposition (CSD) or sol-gel technique has been very much studied and employed in the growth of ferroelectric thin films: low cost, uniformity, excellent thickness and compositional control. Conventional method includes, first of all, the preparation of the desired solution, using metal oxide precursors, solvent and chemical additives to stabilize and control the solution. Then, after coating the substrate with the solution, a sequence of thermal steps is necessary to obtain the desired phase. Finally, another chemical method to deposit ferroelectric films on various substrates is the hydrothermal technique, where chemical reactions in aqueous medium are used. Thin films are usually employed in a composite structure [81], where the elastic properties are dominated by the other part of the device: this can be, for example, a silicon cantilever or membrane [32]. The piezoelectric material and the substrate are clamped along one surface and in the in-plane directions the strains are the same. By contrast, in the perpendicular dimension, the film is free to move. As a consequence of this anisotropy all the deformation modes involve more than one piezoelectric coefficient. This is the main difference between bulk and thin film materials. Besides bulk and thin film materials, we would like to point out that a new class of piezoelectrics is being studied in the last years, the so called hybrids, consisting in a polymeric matrix with ceramic micro/nanoparticles embedded in it, allowing to realize flexible sensing skins for smart applications [82].

Scaling Dimensions of Ferroelectrics and PZT. Ferroelectricity originates thanks to the parallel alignment of permanent dipole moments by means of chemical (short-range) and physical (long-range) forces. This cooperative phenomenon arises below a certain phase transition temperature, called the Curie temperature, as a result of the competition between these temperature-dependent interactions. As a consequence a size effect is inevitably involved [83]: a physical dimension reduction of ferroelectric structures leads to a decrease in transition temperature and spontaneous polarization along with the increase in the coercive field. Changes in properties occur when the film thickness approaches the electrode depletion width or the grain size approaches the ferroelectric domain size [84].

The extent to which ferroelectric materials can be implemented in future generations of microelectronic structures is strictly dependent on the influence of size on the material properties. Several studies have investigated the finite size effects in ferroelectric materials focusing on a critical lateral size or film thickness below which ferroelectricity disappears [85]. The critical thickness of a ferroelectric thin film with perpendicular polarization comes close to about 1 nm [86]. At this value, surface reconstructions need to be considered, because they may ultimately prevent the emergence of ferroelectricity [87, 88]. Regarding the minimum lateral dimension of a ferroelectric domain, it is important to underline that for atomic-scale ferroelectric islands the electric field is generally screened by free external charges that obstruct the inter-domains dipolar interactions. Recent advances [89], reveals that this is not an intrinsic behavior of ferroelectric materials, but an effect of the mechanical and electrical boundary conditions resulting from the synthesis methods used.

It seems clear that in many of the existing studies, size effects are controlled by fabrication process rather than intrinsic limits on the stability of the ferroelectric phase. Film thickness, grain size, and lateral size of the ferroelectric material are parameters that can be tuned within a certain range by an appropriate choice of processing condition [84]. Other quantities like the depletion region amplitude at surfaces, electrode-ferroelectric material interfaces, and grain boundaries can be manipulated operating on the chemical synthesis or annealing conditions. As a result, over time, the minimum thickness at which size effects are observed is continuously dropping. The tremendous number of contributions describing the size effects in ferroelectric thin films introduce high scatter in the reported thickness dependence of the high field properties. In particular scaling down PZT-film thickness while retaining good ferroelectricity has been a topic of great interest scientifically and this dimension has dramatically decreased during the past decade [90].

The achievement of size-independent coercive fields in PZT films down to 60 nm in thickness was reported by Bilodeau et al. [91]. The switchable polarization dropped somewhat for films below 100 nm in thickness. Below 60 nm the films were poor electrical insulators. Kim et al. [92] and Oikawa et al. [90] reported the preparation of 70 and 35 nm thick PZT with good ferroelectric properties. Using mean field theory, Li et al. [93] were able to calculate the critical thickness at which perovskite ferroelectric thin films showed a stable polar phase and applied this theory to PbTiO3 thin films. Song and No [94] implemented the same approach to PZT thin films, finding that the critical thickness was approximately 18 nm.

There are also reports that ferroelectricity is stable in films down to much smaller thicknesses. Tybell et al. [95] showed that ferroelectricity can be observed in PZT films as thin as 4 nm [96] and this statement was confirmed through measurements of the piezoelectric properties with an atomic force microscope. Ferroelectricity in nanometer-thick layers [97] has also found evidence for copolymer ferroelectrics. Regarding the lateral dimension, interesting progress has been done in the achievement of nanometric ferroelectric islands obtained, for example, by ion milling or through self-assembled nanostructures [98]. Nevertheless these dimensions are still relatively large compared with the theoretical values discussed above. A promising route could be the study of 1D nanostructure: ferroelectric BaTiO3 nanorods with diameters as small as 5 nm have been achieved [99].

3.2 High Magnetostriction Materials

Magnetostrictive materials are broadly defined as materials that undergo a change in shape due to change in the magnetization state of the material. In principle, all ferromagnetic materials exhibit a change in shape resulting from magnetization change. In most common materials, nickel, iron, and cobalt, the change in length is on the order of 10 parts per million. This type of magnetostriction has been termed Joule magnetostriction after James P. Joules discovery in the 1850s. The relatively small change in shape of these materials limited their use in engineering.

Following the advances in permanent magnet research, novel magnetostrictive compounds containing iron, terbium and dysprosium have become available in commercial quantities. Rare earth- iron giant magnetostrictive material discovered by Clarke [100] feature magnetostrain that are two order of magnitude higher than nickel ((in the range of 500–1000 ppm), as shown in Table 4. However, to exploit such elastic strains a linear behavior vs applied field is required. Application for highly magnetostrictive materials are miniature magnetostrictive actuators and motors [101], magnetostrictive linear actuators [102], sonar, valve actuation and active vibration control.

More recently an emerging class of magnetostrictive materials iron-gallium alloys (Galfenol) [103] has been discovered that exhibit moderate magnetostriction (\(350\times 10^6\)) at low magnetic fields (8 kA/m) along with low magnetic hysteresis and high tensile strength. The magnetostrictive effect can be used to design sensors for force measurement and energy harvesting devices [104].

It is well known that in low-dimensional systems, magnetic properties are strongly influenced by the reduced symmetry at substrate/film interface. Changes in the magnetization direction as a function of temperature, film thickness, or composition in ultrathin ferromagnetic multilayers consisting of few monolayers has attracted much interest. In this context, magnetoelastic properties of polycrystalline films can be strongly influenced by film thickness, and that in ultrathin films, surface anisotropy and surface magnetostriction terms may dominate over the volume terms. In particular, magnetostriction constant is seen to increase with increasing thickness [105]. Growth conditions may affect the magnetic properties of polycrystalline films due to such factors as film stress, in addition to film thickness. The stress may vary during the film growth depending on the growth model [106]. In our case, films are grown by dc sputtering that is usually known to induce quenched-in stress related to thermally activated process.

3.3 Building a Demonstrator

As our lithography process does not reach at the moment the necessary resolution, we are starting with a more simple structure that will allow us to demonstrate this clock mechanism as a proof of concept. The structure of the demonstrator is shown in Fig. 17(A). Two interdigitated electrodes are fabricated on top of a PZT layer. A NML wire, i.e. a simple chain of magnets, is used as test circuit. Magnets are located in the area between two electrodes arms. The aim of this structure is to demonstrate that, when a voltage is applied to contact pads, magnets are forced in the RESET state. Removing the voltage, magnets should align antiferromagnetically, demonstrating therefore the correctness of this clock solution.

(A) Structure of the proposed circuit demonstrator. Two interdigitated electrodes are fabricated on a PZT layer. Magnets are located in the area between two electrodes arms. Contact pads are used to apply the voltage to the structure. (B) Fabrication Process. Fabrication of the PZT through sol-gel techniques. (C) Electrodes fabrication through direct laser writing lithography. (D) Deposition of magnetic material through sputtering and patterning of magnets through EBL or FIB lithography. (E) Optional removal of magnetic material from the electrodes structure.

The fabrication process of the demonstrator is shown in Fig. 17 from (B) to (E). First of all the piezoelectric layer is fabricated (Fig. 17(B)) as previously described elsewhere [32]. Briefly, the PZT solution (from E.C. Dept., Jozef Stefan Institute Ljubljana, Slovenia) is spin coated over a thin lead titanate (PT) layer. The PT layer was previously spin coated on the metal-patterned substrate, dehydrated at \(200\,^{\circ }\mathrm{C}\) and then annealed at \(500\,^{\circ }\mathrm{C}\). This layer acts as seed layer for the crystallization of the PZT. Four PZT layers (about 70 nm each) were deposited as follows: spin coating, dehydration at \(200\,^{\circ }\mathrm{C}\), pyrolization at \(350\,^{\circ }\mathrm{C}\) and finally, the multilayer was annealed at \(600\,^{\circ }\mathrm{C}\). This annealing condition preserved the (110) preferential orientation of PZT. This process can be repeated until the desired thickness is obtained. As a second step the electrodes structure is created on top of the PZT substrate (Fig. 17(C)). A photoresist is deposited on the PZT layer and is successively patterned through direct writing lithography, partially removing the PZT. Metal is then deposited on top of the photoresist and finally the photoresist is removed obtaining the final electrodes structure. A magnetic film is deposited on the existing structure (Fig. 17(D)). Electron Beam Lithography (EBL) or Focused Ion Beam Lithography (FIB) is used to pattern the magnetic material to obtain magnets and to remove the magnetic material in excess to avoid unwanted contacts between electrodes. The magnetic material is normally a conductor so, also if it covers the electrodes, there will be an electric contact. However, magnetic materials are normally bad electrical conductors, so to improve the structure an optional step (Fig. 17(E)) can be used in order to remove the magnetic materials directly above the electrodes. Clearly the area where magnets are located must be properly masked in the process.

First experimental results. (A) Interdigitated electrodes structure. Arms are interleaved so that between each couple of them there is a strain in the PZT layer. (B) Detail of the electrodes structure. Sizes are in the range of micrometers because the resolution limit of our lithography process is 2um. (C) SEM image of a PZT layer. Its grain structure is clearly visible. (D) SEM image of a FeTb film. The surface is pretty rough.

Due to technical limitations we have not obtained the complete structure yet, however in Fig. 18 we can illustrate some preliminary results. Figure 18(A) shows a scanning electron microscope (SEM) image of the electrodes structure. It is possible to observe the contact pads and the electrodes. Arms of the two electrodes are alternatively interleaved, in this way there will be a strain between each couple of arms. The maximum resolution that we can currently obtain with our lithography process is \(2\,\upmu \mathrm{m}\), so, as it is possible to note from Fig 18(B), electrodes sizes are in the micrometer range. These sizes are much bigger than the desired ones, however, they are enough if the purpose is the demonstration of the effective magnets reset and switching. Figure 18(C) shows instead a SEM image of a typical PZT substrate [33]. It is possible to observe its typical grain structure, with grain sizes in the range of a hundred nanometers. The average roughness is around 3 nm. Figure 18(D) shows instead a film of Iron-Terbium. Iron-Terbium is a material similar to Terfenol with high magnetostriction that we are studying since our studies in [107]. Its surface is pretty rough for the moment and the thickness is quite high: 500 nm. Our efforts are now concentrated on the creation of thinner films with a lower roughness and its deposition on the PZT layer. In the meantime we are using Nickel as magnetic material for our experiments. Normally, an interface layer is used between the PZT and the magnets [34]. This approach reduces the mechanical coupling so we are trying to avoid this choice, depositing the magnetic layer directly on top of the PZT.

Magnets Fabrication. To fabricate magnets we firstly experimented Electron Beam Lithography (EBL). However we were not able to obtain magnets with the required resolution with this technique, due to the small dimensions to achieve and to the vicinity of the desired structures. In the case of small and close packed features, the proximity effect represents one of the hardest limits to overcome. The reason lies probably in this reason, in the relative low acceleration voltage of our FEI Dualbeam Quanta 3D (30 kV) and the high insulating nature of the PZT substrate, which generates many interferences with the electron beam. We therefore switched to Focus Ion Beam (FIB) lithography, obtaining far better results, some of them are shown in 19. Figure 19(A) shows a simple couple of magnets. The smallest obtainable gap among magnets is around 30–50 nm, but the minimum magnet size is around \(65\times 135\,\mathrm{nm}^2\), as shown in Fig. 19(A). Maintaining the magnets sizes between 100 nm and 200 nm the FIB lithography is not critical and at the same time is sufficient for the construction of the demonstrator. Both our theoretical analysis and the results presented in [34] indicate in fact that this clock system can work also with sizes of few hundred of nanometers, but with poorer performance because magnets will be no more single domain entities.

Figure 19(B) shows an example of NML wire, the smallest side is around 86 nm. Unfortunately when we tried to measure this structures with a Magnetic Force Microscope (MFM) we got no magnetic response. We suspect that this is due to multiple reasons, mainly the instrument resolution which is not enough and the influence of the ion beam annealing. The ion bombardment of FIB lithography generates a great amount of heat in an area of about 30 nm (considering an acceleration voltage of 30 kV) around its impact point. The generated heat could be above the Curie temperature so degrading the properties of the magnetic layer, leading to a weak response during the MFM measurements. We are trying to solve this problems in two ways, reducing the FIB current and consequently the damage of the magnetic layer and trying to introduce an intermediate layer between the PZT and the magnetic films. The introduction of an intermediate layer should reduce the interference with the electron beam improving therefore the resolution of the EBL process.

4 Conclusions

The clock solution here proposed represents an important breakthrough for NanoMagnet Logic. It achieves two important results:

-

It allows to develop a true low power system, considering also the losses in the clock generation network.

-

It can be fabricated with current technological processes because it is designed around the constraints arisen by the fabrication processes themselves.

However, some problems require further investigations. From the technological point of view issues related to the patterning of magnetic materials (for the magnets fabrication) on a piezoelectric substrate must be solved. That means to understand and to solve problems of the currently employed lithographic techniques for magnetic layer patterning. Secondly, it is important to understand how the physical properties of piezoelectric materials scale with dimensions. Probably a suitable compromise between performance and piezoelectric layer thickness must be found.

Moreover, some important questions arise, and they must be investigated both from a theoretical and experimental point of view. Are there any other sources of energy loss that are not considered here (like unwanted leakage currents)? Are there problems of crosstalk between neighbor clock zones? It is know that piezoelectric devices can work at frequency equal to tens of MHz, but what is the real maximum frequency that can be achieved? Since this system is based on mechanical deformations, do the vibrations caused by the environment influence it? Which is the expected reliability of this system?

We are trying to understand these problematics and to solve the related problems. Our goal is to destroy one of the most important barrier for the successful development of this technology, the clock power consumption, in order to finally get the first full-magnetic devices.

References

Lent, C., Tougaw, P., Porod, W., Bernstein, G.: Quantum cellular automata. Nanotechnology 4, 49–57 (1993)

Tougaw, P., Lent, C., Porod, W.: Bistable saturation in coupled quantum-dot cells. J. Appl. Phys. 74, 3558–3566 (1993)

Kummamuru, R., Orlov, A., Ramasubramaniam, R., Lent, C., Bernstein, G., Snider, G.: Operation of a Quantum-dot Cellular Automata (QCA) shift register and analysis of errors. IEEE Trans. Electron Devices 50, 1906 (2003)

Smith, C.G., Gardelis, S., Rushforth, A.W., Crook, R., Cooper, J., Ritchie, D.A., Linfield, E.H., Jin, Y., Pepper, M.: Realization of quantum-dot cellular automata using semiconductor quantum dots. Superlattices Microstruct. 34, 195–203 (2003)

Pulimeno, A., Graziano, M., Piccinini, G.: Molecule interaction for QCA computation. IEEE International Conference on Nanotechnology, pp. 1–5 (2012)

Pulimeno, A., Graziano, M., Demarchi, D., Piccinini, G.: Towards a molecular QCA wire: simulation of write-in and read-out systems. Solid State Electron. 77, 101–107 (2012)

Pulimeno, A., Graziano, M., Saginario, A., Cauda, V., Demarchi, D., Piccinini, G.: Bis-ferrocene molecular QCA wire: ab-initio simulations of fabrication driven fault tolerance. IEEE Trans. Nanotechnol. 12(4), 498–507 (2013)

Porod, W.: Magnetic Logic Devices Based on Field-Coupled Nanomagnets. Nano & Giga (2007)

Imre, A.: Experimental study of nanomagnets for quantum-dot cellular automata(MQCA)logic applications. Ph.D. thesis, University of Notre Dame, Notre Dame, Indiana, December 2005

Graziano, M., Vacca, M., Zamboni, M.: Magnetic QCA design: modeling, simulation and circuits. Cellular Automata - Innovative Modelling for Science and Engineering, InTech, (2011) http://www.intechopen.com/articles/show/title/magnetic-qca-design-modeling-s

Niemier, M., et al.: Nanomagnet logic: progress toward system-level integration. J. Phys. Condens. Matter 23, 34 (2011)

Karunaratne, D., Bhanja, S.: Study of single layer and multilayer nano-magnetic logic architectures. J. Appl. Phys. 111, 07A928–07A928-3 (2012)

Varga, E., Csaba, G., Bernstein, G., Porod, W.: Implementation of a nanomagnetic full adder circuit. In: 2011 11th IEEE International Conference on Nanotechnology, August 2011