Abstract

Image Processing algorithms implemented in hardware have emerged as the most viable solution for improving the performance of image processing systems. The introduction of reconfigurable devices and high level hardware programming languages has further accelerated the design of image processing in FPGA.

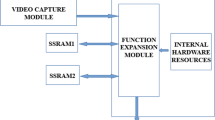

This paper briefly presents the design of Sobel edge detector system on FPGA. The design is developed in System Generator and integrated as a dedicated hardware peripheral to the Microblaze 32 bit soft RISC processor with the EDK embedded system. The input comes from a live video acquired from a CMOS camera and the detected edges are displayed on a DVI display screen.

Chapter PDF

Similar content being viewed by others

Keywords

References

Crookes, D.: Design and implementation of a high level programming environment for FPGA-based image processing. IEE Proceedings on Vision, Image, and Signal Processing 147(4), 377 (2000)

Rao, D.V., Patil, S., Babu, N.A., Muthukuma, V.: Implementation and Evaluation of Image Processing Algorithms on Reconfigurable Architecture using C-based Hardware Descriptive Languages. International Journal of Theoretical and Applied Computer Sciences 1(1), 9–34 (2006)

Neoh, H., Hazanchuk, A.: Adaptive Edge Detection for Real-Time Video Processing using FPGAs. Global Signal Processing (2004)

Spartan-3A DSP FPGA Video Starter Kit user Guide, www.xilinx.com

Xilinx Inc. Embedded System Tools Reference Manual, www.xilinx.com

Xilinx System Generator user Guide, www.xilinx.com

MicroBlaze soft processor, www.xilinx.com

Senal, H.G.: Gradient Estimation Using Wide Support Operators. IEEE Transaction on Image Processing 18(4) (April 2009)

Mallet, J.: Updated Starter Kit Speeds Video Development. Xell Journal (67), 18–21 (2009)

Hutchings, B., Villasenor, J.: The Flexibility of Configurable Computing. IEEE Signal Processing Magazine 15, 67–84 (1998)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Said, Y., Saidani, T., Smach, F., Atri, M., Snoussi, H. (2012). Embedded Real-Time Video Processing System on FPGA. In: Elmoataz, A., Mammass, D., Lezoray, O., Nouboud, F., Aboutajdine, D. (eds) Image and Signal Processing. ICISP 2012. Lecture Notes in Computer Science, vol 7340. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-31254-0_10

Download citation

DOI: https://doi.org/10.1007/978-3-642-31254-0_10

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-31253-3

Online ISBN: 978-3-642-31254-0

eBook Packages: Computer ScienceComputer Science (R0)