Abstract

Poor quality is one of the prime problems in the electrical system. In recent times, high power demand and good quality of power are major concerns in an electrical system. In this paper, a conventional multilevel inverter topology is proposed and to design the LC filter and LCL filter that attenuate the ripple in the output waveform of the proposed MLI topology. The proposed topology used symmetrical configuration, i.e., the dc-link voltage is the same for each H-bridge cell. The performance of MLI is calculated by THD parameter, and the results of the proposed topology with LC, LCL circuit, and normal circuit are compared along with PD, POD and APOD-PWM techniques, followed by over and under modulation index.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

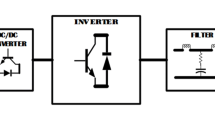

A multilevel inverter is the most popular power converter device used for high power and high voltage applications [1]. The application based on renewable energy is more popular nowadays and power quality is a big challenge. The multilevel inverter is used in renewable power applications as its input is connected to the renewable energy source and its output to the grid. All the converters are nonlinear devices, so they create harmonics, and these harmonics degrade the quality of output power. To eliminate this problem the filter circuit is used at the load side. The selection of the filter is also a big challenge to attenuate particular harmonics. In this paper, two passive filter circuits, LC circuit and LCL circuit, are used, and the performance of these two filter circuits on a seven-level cascade H-Bridge PWM inverter was compared. The performance is measured in terms of total harmonic distortion factor.

2 Proposed Topology

The proposed topology is a conventional cascade H-Bridge seven-level inverter. It has an isolated DC voltage supply for each cell. In a seven-level topology, three H-bridge cells require and three separate DC voltage sources [2] are needed. If the DC voltage source has equal magnitude the configuration is known as symmetric configuration, and if these DC voltage sources have unequal magnitude then the configuration is known as asymmetric configuration. Table 1 shows the switches sequence to obtain voltage levels of the proposed topology. For +3 V level switch sequence 1, 3, 5, 7, 9, 11 is ON and the remaining switches are off. For +2 V level switch sequence 1, 3, 5, 7, 9 and 10 is ON. For +1 V level switch sequence 1, 3, 5, 6, 9 and 10 is ON. For +1 V level switch sequence 1, 3, 5, 6, 9, 10 is ON. For 0 V level switch sequence 1, 2, 5, 6, 9, 10 is ON. For −1 V level switch sequence 2, 4, 7, 8, 11, 12 is ON. For −2 V level switch sequence 2, 4, 6, 8, 11, 12 is ON. For −3 V level switch sequence 2, 4, 6, 8, 10, 12 is ON. Switch configuration is chosen in such a way that stress on the switch remains low. So here use the redundancy method to select the switch to achieve the particular voltage level.

The proposed topology is suitable for high voltage and high power applications [3]. The advantage of the proposed topology is that it does not require any clamping diode and capacitor, so the required component in the proposed topology is less than the other two-diode clamped and flying capacitor topology [4, 5] (Fig. 1).

3 PWM Techniques in the Proposed Topology

The objective of PWM is to control inverter output and reduce the harmonics in the output waveform [6]. In this technique the pulses are generated according to output voltage level and this is done by comparing two waveforms. In this one waveform is a reference waveform of fundamental frequency and the other is a carrier waveform of high frequency [7], [8]. The frequency of carrier waveform is very high compared to reference waveform [9]. In this paper for the proposed topology the level-shifted PWM technique is used as given below. The proposed topology is a seven-level topology, so here the reference signal is a sinusoidal waveform of 50 Hz frequency and the number of carrier waveforms is 6 and each has 2 kHz frequency.

3.1 PDPWM

All carrier waveforms have the same magnitude and same frequency and have zero-phase shifting to adjacent waveform [10]. Figure 2 shows the configuration of PDPWM.

3.2 PODPWM

All the carrier waveforms have the same magnitude and same frequency but the positive carrier and negative carrier groups have 180° phase shift. Figure 3 shows the PODPWM configuration.

3.3 APODPWM

All carrier waveforms have equal magnitude and frequency but adjacent carriers have 180° phase shift to each other. Figure 4 shows the APODPWM configuration.

4 Passive Filter Circuit

In this paper, to improve the quality of voltage at the load side passive filter circuit is used. Passive filter circuits are of different types as single L with load, which gives less distorted output current to load. The combination of L and C has a different combination which provides the attenuation to harmonics [11]. In this paper two configurations of passive filter circuit are used, one is LCL filter circuit and the second is LC filter circuit. The LC circuit is a low pass filter circuit and it is able to attenuate the lower order harmonics in the output waveform. It is a second-order filter circuit giving −40 dB/decade attenuation and LCL circuit as high-pass filter circuit and a third-order filter circuit that gives −60 dB/decade attenuation. The elements L and C are considered lumped. The arrangement of the LC and LCL filter circuits is shown in Figs. 5 and 6.

5 Simulation Result

The simulation result for the proposed topology is derived from MATLAB Simulink 2010b software. The parameters used to simulate the results are DC input voltage is 10 V, reference waveform frequency is 50 Hz, carrier waveform frequency is 2 kHz, loads are resistive in nature and have the value of 10 Ω; filter circuit has L = 10 mH, C = 1 microfarad, L1 = 10 mH and L2 = 0.5 mH. The result simulated with over, under and unity modulation index with respect to level-shifted PWM techniques for LC, LCL filter circuit and with a normal circuit of the proposed topology (Figs. 7, 8, 9, 10, 11 and 12).

6 Conclusion

The comparative study of total harmonic distortion analysis for the proposed topology with passive filter and normal circuit is presented in this paper. With the use of a filter circuit, the output waveform has less harmonic component, which improves the quality of power. Table 2 shows the simulation result and made a comparison between the normal circuit, LC filter circuit and LCL filter circuit. Figures 13, 14 and 15 show the comparison graph for over, unity and under modulation index, which shows the % total harmonic distortion value in the proposed topology with passive filter circuit and normal circuit followed by level-shifted PWM techniques. The LCL filter sometimes causes steady-state and transient problems due to resonance, hence the LC filter is widely used as it attenuates lower order harmonics which is more important in inverter application. The result obtained with the filter circuit is within the IEEE THD limit. This shows the usefulness of the filter circuit in the proposed topology.

References

Rodriguez J, Jih-Sheng L (2002) Fang Zheng, “Multilevel inverters: a survey of topologies, controls, and applications.” IEEE Trans Ind Electron 49:724–738

Samsami H, Taheri A, Samanbakhsh R (2017) New bidirectional multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. In IET power electronics

Sarat Kumar Sahoo, A. Ramulu, Jyoti Prakash and Deeksha, “Performance Analysis and Simulation of five level and seven level single phase multilevel inverters” in third International conference on Sustainable energy and intelligent system (SEISCON 2012), VCTW, Tamilnadu, India, on 27–29 Dec, 2012

Najafi E, Yatim AHM, Samosir AS (2008) A new topology-reversing voltage (RV) for multi-level inverters. In 2nd International conference on power and energy (PECon 08), pp 604–608, December 2008 Malaysia

Agrawal N, Tomar SS, Bansal P (2017)A multilevel inverter topology using reverse-connected voltage sources. In 2017 International Conference on Energy, Communication, Data Analytics and Soft Computing (ICECDS), Chennai, 2017, pp 1290–1295. https://doi.org/10.1109/ICECDS.2017.8389652

Agrawal N, Goswami S, Bagaria R, Muthele A (2021) A comparative brief study on level-shifted pulse width modulation and hybrid pulse width modulation switching techniques for 7-Level CHB single-phase inverter. In Advances in smart grid and renewable energy. ETAEERE 2020. Lecture Notes in Electrical Engineering, vol 691. Springer, Singapore. https://doi.org/10.1007/978-981-15-7511-2_14

Tomar SS, Agrawal N, Bansal P (2017) Various modulation techniques in symmetrical multilevel inverters. In 2017 international conference on energy, communication, data analytics and soft computing (ICECDS), Chennai, India, pp 1322–1327. https://doi.org/10.1109/ICECDS.2017.8389658

Vijayarajan P, Shunmugalatha A, Sait HH (2016) Development of modified carrier based PWM scheme for single phase H-bridge Inverter fed isolated wind–PV systems. Sol Energy 126:208–219 Mar

Agrawal N, Bansal P, Umale N (2020) THD Analysis of New Multilevel Inverter Topology with Different Modulation Techniques. In International conference on intelligent computing and smart communication 2019. Algorithms for Intelligent Systems. Springer, Singapore. https://doi.org/10.1007/978-981-15-0633-8_117

Jani Rushiraj G, Kapil PN (2016) Analysis of different modulation techniques for multilevel inverter. In IEEE international conference on power electronics, intelligent control and Energy System (ICPEICES 2016)

Agrawal N. Performance analysis of cascade H-Bridge multilevel inverter topology with filter circuit and without filter circuit. Design and Optimization of Sensors and Antennas for Wearable Devices: Emerging Research and Opportunities, pp 87–101.https://doi.org/10.4018/978-1-5225-9683-7.ch008

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Agrawal, N. et al. (2022). Study of Filters for Improving the Output of Cascaded Seven-Level Inverter. In: Mallick, P.K., Bhoi, A.K., González-Briones, A., Pattnaik, P.K. (eds) Electronic Systems and Intelligent Computing. Lecture Notes in Electrical Engineering, vol 860. Springer, Singapore. https://doi.org/10.1007/978-981-16-9488-2_16

Download citation

DOI: https://doi.org/10.1007/978-981-16-9488-2_16

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-9487-5

Online ISBN: 978-981-16-9488-2

eBook Packages: EngineeringEngineering (R0)