Abstract

The computation of the reversible logic circuit is gaining enough interest in the field of low-power applications and also the quantum circuit computation. In the rapid progress of synthesis design, the testing of a reversible circuit emerges area in the field of testing. In this paper, we consider the problem of testing in the reversible circuit, and in particular, generating efficient test sets for single-input stuck-at faults and bridging faults. Numerous fault models of reversible circuit have been proposed to reduce the possible faults in the circuit, many of the proposed fault models common to traditional logic. The paper proposes that for detecting all the possible input bridging faults, \((\lceil n/2 \rceil )\) numbers of test vector are required and adding only one more test vector \(((\lceil n/2 \rceil )+1)\) with an existing test set of input bridging faults can be sufficient enough for detecting another fault model, which is considered here as an input stuck-at faults. Finally, we provide our experimental results based on different reversible benchmark circuits and compared with an existing method to show that the generated test set is covered by both the fault models.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

The reversible circuit technologies are more promising future alternative as compared to conventional circuit technologies in the scenario of high-performance computation. Rolf Landauer [1], 1961, showed that whenever using a logically irreversible operation, it dissipates energy into the environment. The reversible logic operations are those operations which can reuse a fraction of the signal energy that theoretically can approach near to 100%. Therefore, the reversible logic circuit is the most popular technology to achieve this performance. The properties of the reversible circuit are simpler than a conventional circuit. The basic properties of reversible circuits are (a) number of inputs are equal to the number of outputs, (b) only bijection operation is allowed, and (c) no fanout and feedback connection is allowed.

Due to the reversibility property, the efficient test pattern generation of a reversible circuit is relatively simpler than the traditional logic circuit. The other facet of the reversible circuit is that it has produced unique output vector from each corresponding input vector and vice versa, which gives high controllability and observability [2]. A test set is a collection of the input test vectors which are applied to a reversible circuit to detect and observe that the faults are occurred in the circuit. The test set is called as complete test set if it is capable of detecting all the faults in a given circuit. The relation between different fault models of the reversible circuit has been discussed in [3]. This paper has drawn parallels between the bridging and stuck-at faults for generating the test patterns. The test vectors that set the two lines by the opposite logic values “01” and “10” are used to detect the two lines of bridging faults at the same level [4]. In other way, for detecting the stuck-at faults at any level, the lines at every level are set by 0 and 1. Generated complete test set for individual fault model is already in the literature but “generated test patterns for one particular fault model is derived such that it is capable of detecting another fault model” is our key concern. Based on this concept, we have generated the test patterns for the input bridging faults and further reconstructed the test vectors for the input stuck-at faults which are obtained from bridging fault model.

The rest of the paper is organized as follows: Sect. 2 provides some basic background on reversible logic circuits and an overview of stuck-at and bridging fault model in the reversible circuit. Sect. 3 describes our proposed method for generating the test set for detecting input bridging and stuck-at faults. The experimental result and conclusion are provided by Sect. 4 and Sect. 5, respectively.

2 Background

2.1 Reversible Logic Circuits

A reversible logic circuit is used to implement the reversible computation and it is formalized in terms of gate-level circuits. The reversible circuit structures are cascade structure [5]. All the operation of the reversible circuit has to be performed in a reverse form. The reversible circuit allows only bijective operations [2] and maintained the bijective operation; the circuit does not include any concept of fan-out and feedback connection [6]. In reversible circuit design, several gates have proposed over the past decades. They are the controlled NOT (CNOT) proposed by Feynman [7], Toffoli [8], Fredkin and Toffoli [9], etc. In this paper, we are using only NCT library that contains NOT, CNOT, Toffoli gate, and GT library containing generalized (n-bit) Toffoli gate. This NCT library was introduced by Toffoli [8] in 1980.

2.2 Fault Models in Reversible Circuit

A fault model has described the different levels of abstraction of physical faults in a system. These levels of abstraction can be defined as behavioral, functional, structural, and geometric [4]. A fault model is a mathematical model which represents various faults possibilities and it helps to generate the tests for detecting and reducing all the possible faults in a given circuit [3]. Numerous fault models have been introduced in the reversible circuit. In this work, we have considered stuck-at fault and bridging fault model in the reversible circuit.

-

1.

Bridging Faults in a Reversible Circuit: The bridging faults occur when two signals are connected together but they should not be. If two or more lines involved in bridging faults, then logical effects of this faults are categorized by wired-OR or wired-AND bridging faults [4]. The single-input bridging faults occur, if two input lines are operated by the opposite logic values [10]. Sarkar and Chakrabarti [11] proved that if any test set is complete for the single-input bridging faults, then that particular test is also completed for detecting the multiple-input bridging faults. The authors also showed that the generated test sets are capable of detecting all the possible single- and multiple-input bridging faults if generated test sets are eligible for detecting all the single-input stuck-at faults in a given reversible circuit.

-

2.

Stuck-at Faults in a Reversible Circuit: The stuck-at faults occur in a circuit when one of its inputs and outputs to be fixed at either logic value 0 (stuck-at-0) or logic value 1 (stuck-at-1) without considering the input value. This is a very common fault model used for irreversible circuits. If the stuck-at fault is involved only for one line in the circuit, then it is called as the single stuck-at fault (SSF), and if stuck-at fault is involved more than one line, then it is called as multiple stuck-at faults (MSF). Patel et al. [2] stated that any test set is complete for detecting the stuck-at faults, if and only if each line at every level can be set to both 0 and 1 by the test sets. The paper [2] also showed that the test set is complete for all single stuck-at faults, and then it also becomes complete test set for all multiple stuck-at faults.

3 Proposed Method

We have divided into two modules in our method. The first module described the test pattern generation of single-input bridging faults. After generating the test patterns, we have derived these patterns for further use of single-input stuck-at faults. Also, we have introduced fault description list (FDL) in our work. The detailed discussion has been given below.

3.1 Fault Description List

Fault description list contains all the possible faults which are generated by the test vectors based on the position of the binary bit sequence present in that test vector. Using the fault description table, we have checked that which test vector is covered by a maximum number of faults and combined the minimum number of test vectors such that it covers all the possible faults in the given reversible circuit.

The construction of ATPG and fault description list (FDL) flow is shown in Fig. 1. In Fig. 1, step (a) extracts all the possible single-input bridging and stuck-at faults in the given reversible circuit. Step (b) generated all the possible test pattern from our proposed method (ATPG). All the faults are stored in the fault list which is generated by test pattern mentioned in step (c). In step (d), each individual test pattern of corresponding faults adds to the test set. Now, we have checked that fault list is covered all the faults, if not then take another combination of test patterns and continue the same process. If some selected test set is able to cover all the faults, then that test set is the final one for detecting all the faults; it has mentioned in step (e) and also this test set is minimized form because the combination of test vectors is growing in increasing order.

3.2 Test Set Generation Algorithm for Single-Input Bridging Fault

In this section, we have arranged our proposed method into two algorithms. Algorithm 1 has explained initially how to extract all the test vectors (TV) based on the bridging faults property. To obtain the binary bit sequences, we are starting from n = 3, where n is the number of input lines of the reversible circuit. In Algorithm 2, the FDL has ensured that which test vector(s) is capable of detecting all single-input bridging faults \((l_1,l_2), (l_1,l_3) \ldots (l_i,l_j)\), where \(i<j\le n\) and \( (l_i,l_j)\in F_{B_i}\) in the given circuit. Finally, select the minimized fault detecting test set \(T_B\) of N number of input lines in a reversible circuit.

Lemma 1

Detecting single- and multiple-input bridging faults in a given n-input reversible circuit, the \((\lceil n/2 \rceil )\) number of test vectors are sufficient.

Proof

Here, each of the input lines can be set to both opposite logic values 0 and 1. The test vector \(TV_i\)=(\(\langle b_{0i} \ b_{1i} \ b_{2i} \ \ldots \ b_{(n-1)i} \rangle \)), where \(1\le i\le \lceil n/2 \rceil \), \(b_{(n-1)i}\) is the \((n-1)\)th bit of ith test vector and \(b_{(n-1)i} \in \{0,1\}\). As explained in Algorithm 1, the test set T=\(\{TV_1, TV_2, TV_3\}\) is the test set for n = 3-input lines (initially) in the given reversible circuit, where no duplicate and complement test vectors are present. The total single-input bridging faults are C(n, 2) = 3 in the three-input reversible circuit. In the binary bit position for three-input lines, any one of the test vectors is capable of detecting the number of faults C(n, 2) / 2 or more than C(n, 2) / 2 of the total faults but only one test vector is unable to detect all the faults. Because at least one logic value for each test vector is similar to the other logic value, to maintain the opposite logic value for each test vector, the test set \(T_B\) has exactly produced \(\lceil n/2\rceil \) test vectors. Therefore, according to Algorithm 2, we formed the test set \(T_B\) = {\(TV_1\), \(TV_2\)} that is capable of detecting all the faults in the given three-input reversible circuit. If we go for (n + 1), i.e., four-input lines in the reversible circuit, then adding extra input line is created new faults \((l_1,l_4), (l_2,l_4), (l_3,l_4)\). For detecting new faults, we are adding 0 or 1 to the least significant bit (LSB). We have only checked the new form of faults because existing faults are automatically covered by the existing test vector (for n = 3). Hence, \(\lceil n/2\rceil \) test vectors are required to detect all the single-input bridging faults.

3.3 Test Set Generation Algorithm for Single-Input Stuck-at Fault

In this section, we have introduced our algorithm for detecting single-input stuck-at faults. Algorithm 3 extracted the test set \(T_B\) which is derived from the single-input bridging fault model and generated the final test set \(T_S\) for detecting the single-input stuck-at faults.

Lemma 2

Detecting all the single- and multiple-input stuck-at faults in a given n-input reversible circuit, the \((\lceil n/2 \rceil ) + 1\) number of test vectors are sufficient enough.

Proof

In Lemma 1, it has proved that test set \(T_B\) = {\(TV_1\), \(TV_2\)} is capable of detecting all the single-input bridging faults in three-input reversible circuit. Any combination of test vectors (excluding complement of test vector), at least one-bit position, is occurred with same logic value. Due to this fact, it is unable to cover either one (or more) stuck-at-0 or stuck-at-1 fault(s). If we are introducing new test vector which is the complement of any test vector (e.g., \(TV_1\) or \(TV_2\)), then that bit position of complement test vectors must occur at least one opposite logic value. Therefore, extra one more test vector is needed for detecting the single-input stuck-at faults in our proposed method, i.e., the test has required exactly \((\lceil n/2 \rceil )+1\) number of test vectors.

Example 1

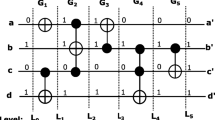

Consider the reversible benchmark circuit ham3 consisting of three-input and three-output lines as shown in Fig. 2a. The number of single-input bridging faults is \(C(3,2) = 3\). Algorithm 1 generated the minimized test vectors in \(T = \{001, 010, 011\}\). Then, using Algorithm 2, the final minimized test set \(T_B = \{001, 010\}\) with the help of FDL, which is the complete test set in a ham3 benchmark circuit for detecting the input bridging faults. In this circuit, the total numbers of single-input stuck-at faults are \(3\times 2 = 6\). It has observed that the test set \(T_B\) is not capable of capturing all the single-input stuck-at faults. Hence, we apply Algorithm 3 and generated the complete test set \(T_S = \{001, 010, 110\}\), where “110” is the complement form of “001”. The test set \(T_S\) covered all the possible single-input faults in ham3 benchmark circuit.

Example 2

In this example, we are considering  reversible benchmark circuit consisting of four-input and four-output lines as shown in Fig. 2b. The number of input bridging faults is \(C(4,2) = 6\). The Step 9 in Algorithm 2 generated the minimized test set \(T_B = \{0011, 0101\}\) with the help of FDL, which is the complete test set for detecting the single-input bridging faults in a

reversible benchmark circuit consisting of four-input and four-output lines as shown in Fig. 2b. The number of input bridging faults is \(C(4,2) = 6\). The Step 9 in Algorithm 2 generated the minimized test set \(T_B = \{0011, 0101\}\) with the help of FDL, which is the complete test set for detecting the single-input bridging faults in a  benchmark circuit. Now if we consider the single-input stuck-at faults of this circuit, then a total number of single-input stuck-at faults occur \(4\times 2 = 8\). Similarly, the test set \(T_B\) is not capable to detect all the input stuck-at faults. Therefore, Algorithm 3 is generated the test set \(T_S = \{0011, 0101, 1100\}\), where “1100” is the complement form of “0011”. The test set \(T_S\) is the complete test set for detecting single-input stuck-at faults in

benchmark circuit. Now if we consider the single-input stuck-at faults of this circuit, then a total number of single-input stuck-at faults occur \(4\times 2 = 8\). Similarly, the test set \(T_B\) is not capable to detect all the input stuck-at faults. Therefore, Algorithm 3 is generated the test set \(T_S = \{0011, 0101, 1100\}\), where “1100” is the complement form of “0011”. The test set \(T_S\) is the complete test set for detecting single-input stuck-at faults in  benchmark circuit.

benchmark circuit.

4 Experimental Results

The proposed algorithms are generating the mixing test vectors applied to various reversible benchmark circuits [12] with NCT and GT models. The test sets are generated by our proposed method that is compared with the existing method [11] which is shown in Table 1. It has observed that the proposed method gives good performance in both the fault models and also covered 100% faults.

5 Conclusion

This paper observed that there is a close relation between stuck-at and bridging faults in the reversible circuit. This paper concludes that \((\lceil n/2 \rceil )\) test vectors are generated at first for detecting the input bridging faults and reconstructed the test vectors from the bridging fault model such that adding only one test vector is sufficient to detect input stuck-at faults in the n-input reversible circuit. There will be a possibility to design a technique such that similar type of test vectors can be detected which may be some other fault models. This may lead to the future work.

References

Landauer R (1961) Irreversibility and heat generation in the computing process. IBM J Res Dev 5(8):183–191

Patel KN, Hayes JP, Markov IL (2004) Fault testing for reversible circuits. IEEE Trans Comput Aided Design Integ Circuits Syst 23(8):1220–1230

Rice J (2013) An overview of fault models and testing approaches for reversible logic. In: 2013 IEEE pacific rim conference on communications, computers and signal processing (PACRIM). IEEE, pp 125–130

Jha NK, Gupta S (2003) Testing of digital systems. Cambridge University Press

Maslov D (2003) Reversible logic synthesis. PhD Dissertation, University of New Brunswick

Nielson MA, Chuang IL (2000) Quantum computation and quantum information. Monograph Collection (Matt-Pseudo)

Feynman RP (1986) Quantum mechanical computers. Found Phys 16(6):507–531

Toffoli T (1980) Reversible computing. Springer

Fredkin E, Toffoli T (2002) Conservative logic. Springer

Rahaman H, Kole DK, Das DK, Bhattacharya BB (2007) Optimum test set for bridging fault detection in reversible circuits. In: 16th Asian test symposium, ATS07. IEEE, pp 125–128

Sarkar P, Chakrabarti S (2008) Universal test set for bridging fault detection in reversible circuit. In: 3rd international design and test workshop, IDT 2008. IEEE, pp 51–56

Maslov D, Dueck G, Scott N (2005) Reversible logic synthesis benchmarks page

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Handique, M., Ahmed, J. (2018). Mixing Test Set Generation for Bridging and Stuck-at Faults in Reversible Circuit. In: Bhattacharyya, S., Gandhi, T., Sharma, K., Dutta, P. (eds) Advanced Computational and Communication Paradigms. Lecture Notes in Electrical Engineering, vol 475. Springer, Singapore. https://doi.org/10.1007/978-981-10-8240-5_11

Download citation

DOI: https://doi.org/10.1007/978-981-10-8240-5_11

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-8239-9

Online ISBN: 978-981-10-8240-5

eBook Packages: EngineeringEngineering (R0)

benchmark circuit

benchmark circuit