Abstract

In this paper, a high-performance domino logic style with reduced delay and less delay variability under process parameter variations is presented. An improved control methodology with delayed enabling of the keeper circuit using the clock signal is proposed. This makes the keeper to be idle during the start of the evaluation phase and reduces the contention. It also helps in increasing the speed performance of the circuit. Furthermore, the reduced loop gain due to the modified keeper circuit lessens the delay variations. The proposed keeper control circuits demonstrate delay reduction of 46% compared to the conventional domino logic circuit. The statistical variations of the process parameters using Monte Carlo analysis demonstrate the reduced delay variations to the tune of 48% for 100 runs. The circuits are simulated using Cadence Virtuoso® employing 180 nm technology node libraries.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

- Contention current

- Domino logic

- Keeper transistor

- Leakage current

- Low power dynamic circuits

- Process variations

- Robustness

- Reliability

1 Introduction

In high-performance applications, the domino logic circuits are widely used owing to its compactness and increased operating speed [1]. However, the leakage current and the high sensitivity to the input noise degrade the performance. To counteract this, the keeper circuit is incorporated in the dynamic node in order to replenish and retain the nodal charge. An increase in the keeper size replenishes the charge easily, and it can retain the logic state for a longer time, which in turn offers robustness for the circuit. However, when the pull-down network (PDN) happens to discharge depending on the input conditions being TRUE, the upsized keeper transistor tries to retain the charge inadvertently, leading to an increased contention current. It can result in deterioration of the speed performance also [2]. Hence, it is imperative to use an appropriate keeper control mechanism and suitable keeper size to offer high speed, low power operating capability and less leakage current.

In wide fan-in applications using domino logic circuits, the presence of numerous leakage current paths leads to easy discharge of the dynamic node charge and results in false evaluation. This embarks on the need for suitable leakage control mechanisms to improve the robustness of the logic. Furthermore, the drain current of the transistor is affected due to the variation in the process parameters, such as the oxide thickness (t ox) and resulting gate capacitance. This results in a corresponding impact on the power and delay variability of the circuit. The loop gain due to the feedback loop, configured by the dynamic node, the inverter and the keeper circuitry also increases the delay variability in addition to the process parameter variations [3]. The necessity for leakage reduction mechanism, robustness and the tolerance to process variations has resulted in devising various keeper control mechanisms by the researchers [4,5,6,7,8].

This paper proposes a keeper control mechanism based on the delayed enabling of the dual keeper transistor circuit during the evaluation phase. This facilitates easy discharge of the dynamic node, when required depending on the input conditions, and the contention is reduced. Section 2 elaborates the conventional domino logic styles, and Sect. 3 details the proposed delayed enabling of the keeper control. The simulations carried out towards the comparative power measurements, delay computations and Monte Carlo simulations for validating the proposed structure are detailed in Sect. 4, and Sect. 5 concludes.

2 Domino Logic Circuit Style

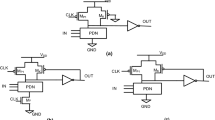

The conventional domino logic style comprises of the following: (1) A single PMOS transistor acting as the pre-charge device (M pre) which also acts as the pull-up network (PUN) and (2) The evaluation NMOS footer transistor, along with the pull-down network (PDN) consisting of NMOS devices connected as per the required logic function. This structure makes the domino logic a high-performance circuit style with less area and lower power consumption [1], primarily due to the reduction in the number of devices employed. While the conventional CMOS circuit requires 2N devices, where N is the number of logic parameters involved, the corresponding dynamic implementation requires only N + 2 devices. The dynamic logic is felt more advantageous due to the additional fact that N number of PMOS devices which consume more silicon area on the chip is replaced by only one PMOS device acting as the pre-charge device, with the smaller N + 1 number of NMOS devices in the pull-down structure. The domino logic when connected with an NMOS transistor in series acting as a footer is referred tothe footed structure and when connected without an NMOS footer transistor in series is referred to the footer-less structure. The two structures are shown in Figs. 1 and 2, respectively. This particular feature can create a difference in the delay and the leakage current parameters of the two types of circuits [4].

During the pre-charge phase, when the clock signal is LOW, the pre-charge PMOS transistor (M pre) conducts making the dynamic node to attain logic HIGH or to the voltage V dd of the power supply. During the evaluation phase, when the clock signal is HIGH, the PDN either retains or discharges the charge of the dynamic node, depending on the input logic conditions. Any possible deterioration of the charge at the dynamic node during the evaluate phase gets replenished constantly using the keeper circuit consisting of a PMOS transistor connected to the inverted dynamic output node as shown in Figs. 1 and 2.

Increasing the size of the keeper transistor, M k can enable retention of the output nodal charge for a longer time [2]. However, contention current may arise when the PDN tends to discharge in response to the input conditions, and even when the keeper transistor tries to retain the charge at the dynamic node. This leads to inadvertent delay and reduced operating speed of the circuit. Hence, various keeper control mechanisms had been put forth by researchers for reducing the delay [6,7,8,9,10]. Some of the widely discussed proposals are (1) Momentary delayed enabling of the keeper transistor [5]; (2) abrupt control of the keeper transistor [6,7,8]; (3) keeper control based on precomputation; and (4) optimal sizing of the keeper transistor [10, 11]. In addition to the focus on the charge retained at the dynamic output node, various strategies have also been presented in order to effectively control the leakage current [4].

All these various types of keeper control mechanisms offer the solution at the cost of an additional circuit overhead even while causing more power consumption due to the overhead. In high-speed domino logic [12], delayed enabling of the keeper circuit is deployed with an additional NMOS transistor and delayed clock control for the keeper circuit. This facilitates easy discharge of the PDN (if required) and increases the speed performance. The proposed style is an enhanced version of the high-speed domino logic style and is also based on the same principle of delayed enabling of the keeper circuit. In less fan-in circuits, power overhead is incurred due to the incorporated keeper control circuitry. However, in wide fan-in circuits, the power overhead is got rid as the leakage power is minimized and hence results in reduced power consumption. This justifies the necessity of additional keeper circuitry in wide fan-in circuits.

3 Proposed Domino Logic Circuit with Reduced Contention

The proposed domino logic circuit shown in Fig. 3 consists of the conventional keeper transistor split into two PMOS keeper transistors (M k1 and M k2) connected in series, in addition to the conventional pre-charge transistor and the PDN with the footer transistor. The M k1 keeper transistor is controlled by the delayed inverted clock signal. The M k2 keeper transistor is controlled by the output signal as in the case of the conventional domino logic style.

During the pre-charge phase, when the clock signal is LOW, the pre-charge transistor (M pre) is in the conducting mode, and the dynamic node is charged to HIGH logic voltage level. When the clock signal is HIGH, evaluation occurs, and the keeper transistor M k1 is initially disabled due to the delayed enabling of the keeper transistor (M k1) using the delayed inverted clock signal. This facilitates the PDN to facilitate the discharging at a faster pace, when required as determined by the input combinations. After the delay as set by the inverter, the device M k1 is enabled, and then, the charge retention of the dynamic node is determined by the M k2 keeper transistor.

The momentary delay in enabling the keeper circuit reduces the contention problem between the PDN and the keeper circuit. During the evaluation phase, if the PDN inputs are HIGH, the dynamic node discharges easily during the initial part of the delayed keeper enabling time. This enhances the operating speed of the circuit.

Furthermore, as shown in the circuit of Fig. 3, having two transistors of reduced size in effect lowers the trans-conductance (g m) of the pull-up network, and hence, the closed loop gain of the keeper (M k2)—inverter circuit is also lowered [3]. This reduces the delay variability characteristics of the circuit. Furthermore, the two keeper transistor in the stack arrangement reduces the leakage current occurring in the keeper control circuit.

Comparison of the proposed structure with the conventional domino logic circuit demonstrates the fact that the proposed keeper control circuitry incurs an additional overhead of an inverter and one PMOS keeper transistor. However, the two keeper transistor sizes could be sized to half of the conventional keeper transistor with efficient laying out of the chip. This can render a solution to the problem of the area overhead due to the proposed dual keeper transistor topology.

4 Simulation and Analysis

The simulation of the proposed clock delayed dual keeper circuit is carried out for various wide fan-in gates. The industry standard Cadence® EDA tools employing 180 nm technology library have been used for simulations. A 64-bit input OR gate designed using the proposed delayed dual keeper circuit demonstrates reduced delay values of 352.4 ps compared with the conventional domino logic circuit and high-speed domino which incurs a delay of 411.98 and 405.3 ps, respectively, as marked in Table 1.

Analysing the power consumption characteristics, it can be found that for the gates with less fan-in and simple circuits, a slighter increase in the power consumption is measured for the proposed keeper domino circuits, which is mainly due to the additional keeper circuit. However, for wider fan-in gates, the total power consumption of the proposed circuit is less compared to that of a conventional domino logic circuit and the high-speed domino circuit. It is due to the extra keeper control circuit consuming very less power compared to that of the total power consumption. Figure 4 depicts the comparative analysis of the delay of various test circuits using different types of domino logic.

The leakage current values of the circuit during various phases of operation differ depending on the static leakage current of the OFF transistors. The leakage current is analysed for the three different states, namely (1) clock high input low (CHIL), (2) clock low input low (CLIL) and (3) clock high input high (CHIH). The simulation results tabulated in Table 2 signify that the CLIL state is an idle state for efficient leakage reduction at normal temperature.

The process variations and the feedback loop of the domino circuit can lead to increased delay variability conditions. The proposed circuit is simulated and validated for 100 runs using Monte Carlo simulations. The mean delay (µ) and the standard deviation (σ) of the proposed clock delayed dual keeper circuit are low which makes the delay variability (σ/µ) also to be low compared to that of the conventional domino logic style as depicted in Table 3. The reduced delay variability (σ/µ) of the proposed delayed dual keeper circuit implies less delay variability under PVT (Process, Voltage and Temperature) variations.

5 Conclusion

The delayed enabling of the keeper circuit in the proposed domino logic circuit style using clock and the dual keeper circuitry facilitates efficient and contention-less discharge of the PDN. This enhances the speed of the domino logic circuit. It is observed that for a 64-bit input OR gate, it is around 352.54 ps. Additionally, the delay variability of 9.8% realized by the proposed method demonstrates the fact that this proposed structure of domino logic is more robust. It is also observed that the clock low input low (CLIL) state is the optimal state for leakage reduction under idle conditions at room temperature. These analyses substantiate the claims that the proposed clocked delayed dual keeper circuit can perform the logic evaluation at higher speed with greater robustness.

References

Chatterjee B et al (2004) Leakage control techniques for designing robust, low power wide-OR domino logic for sub-130 nm CMOS technologies. In: Proceedings of 5th international symposium on quality electronic design, pp 415–420

Krambeck RH, Lee Charles M, Law H-FS (1982) High-speed compact circuits with CMOS. IEEE J Solid State Circuits 17(3):614–619

Palumbo G, Pennisi M, Alioto M (2012) A simple circuit approach to reduce delay variations. IEEE Trans Circuits Syst I Regul Pap 59(10):2292–2300

Moradi F et al (2013) Domino logic design for high performance and leakage-tolerant application. Integr VLSI J 46(3):247–254

Anis MH, Allam MW, Elmasry MI (2002) Energy-efficient noise tolerant dynamic styles for scaled-down CMOS and MTCMOS technologies. IEEE Trans Very Large Scale Integr VLSI Syst 10:71–78

Sharroush SM et al (2008) Speeding-up wide-fan in domino logic using a controlled strong PMOS keeper. In: International conference on computer and communication engineering, pp 633–637

Alvandpour A, Krishnamurthy R, Sourrty K, Borkar SY (2002) A sub-130-nm conditional-keeper technique. IEEE J Solid State Circuits 37:633–638

Lih Y, Tzartzanis N, Walker WW (2007) A leakage current replica keeper for dynamic circuits. IEEE J Solid State Circuits 42(1):48–55

Huang CH et al (2011) Adaptive pseudo dual keeper for wide fan-in dynamic circuits. IEEE Trans Circuits Syst II Express Briefs 58(10):672–676

Dadgour H, Banerjee K (2010) A novel variation-tolerant keeper architecture for high-performance low-power wide fan-in dynamic OR gates. IEEE Trans Very Large Scale Integr (VLSI) Syst 18(11):1567–1577

Wang J et al (2011) Leakage current, active power, and delay analysis of dynamic dual Vt CMOS circuits under P–V–T fluctuations. Microelectron Reliab 51:1498–1502

Anis MH, Allam MW, Elmasry MI (2002) Energy-efficient noise tolerant dynamic styles for scaled-down CMOS and MTCMOS technologies. IEEE Trans Very Large Scale Integr (VLSI) Syst 10:71–78

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Anita Angeline, A., Kanchana Bhaaskaran, V.S. (2018). High Performance Domino Logic Circuit Design by Contention Reduction. In: Li, J., Sankar, A., Beulet, P. (eds) VLSI Design: Circuits, Systems and Applications . Lecture Notes in Electrical Engineering, vol 469. Springer, Singapore. https://doi.org/10.1007/978-981-10-7251-2_18

Download citation

DOI: https://doi.org/10.1007/978-981-10-7251-2_18

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7250-5

Online ISBN: 978-981-10-7251-2

eBook Packages: EngineeringEngineering (R0)