Abstract

MOSFETs models have been critical components for evaluation of devices design and technology. These models face the challenge of being scalable to match the available semiconductor technologies. For the 45 nm MOSFET production, dielectric and metal gates were integrated. With new high dielectric materials and thinner oxide layers, new physics effects emerged that were not considered or integrated into the early models used in circuit simulators. Here an analytical model for 45 nm MOSFETs is presented. The model includes Short Channel Effects (Channel Length Modulation, the threshold voltage variation and carriers velocity saturation). The Drain-Source current and voltage equations derived from the model are implemented as a circuit device in SPICE 3F5. A comparison between the experimental data provided by the manufacturer and the simulation results obtained with the developed model integrating the technological and electrical parameters published by Intel®, demonstrates good agreement between both sets of data.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

Keywords

10.1 Introduction

The semiconductor industry has continuously increased the density of transistors on a chip, successfully reducing their physical dimensions. This trend, predicted by Moore’s Law [1], has imposed challenges on device modeling, which is an essential tool to simulate the operation of Integrated Circuit (IC) prior to the fabrication process. One of the main challenges of device modeling is to describe the behavior of nanometer scaled Metal Oxide Semiconductor Field Effect Transistors (MOSFETs).

Table 10.1 summarizes the state of the art of compact models developed for SPICE:

The behaviour of a MOSFET in an electrical circuit has been studied using circuit simulators. The Simulation Program with Integrated Circuits Emphasis SPICE, is an example of them.

From the table it can be observed that:

-

There is a high complexity involved on recently developed compact models

-

Models have been strongly focused on Silicon dioxide

The complexity arises from the top-down approach focusing on the application rather than on the electrical transport properties on the device. The models above studied, do have a challenge to include others dielectric materials beyond \( SiO_2 \). An example of high dielectric materials is the hafnium dioxide \( HfO_{2} \). This chapter describes a methodology proposed to build a compact model based on the transport properties at nanoscale, aiming to integrate the outputs of analytical equations into ABM blocks to simulate the output of a basic circuit topology (half-wave rectifier).

10.2 Field Effect Transistors State of the Art

Emergent novel structures of Field Effect Transistors (FET) were investigated prior developing the model, both in research (R) and production (P) stages. Table 10.1 summarize the structures reported by the ITRS in 2009. The Table 10.2 intends to review three key parameters: gate length and description and the structures power dissipation.

Intel®’s 45 nm High-k MOSFET is selected as the focused of the model given the barriers to keep the high number of transistors on a single chip: dissipated power and sacrificing device performance (thin SiO_2 layers affect the transistors leakage current and speed) [10]. The target model aims to integrate and understand the short channel effects and to keep the compatibility with one of the most widely used IC simulation language: SPICE.

It can also be observed that the devices in production involve new materials different form the conventional CMOS devices materials. Among the available High-κ dielectric materials (such as ZnO 2 ) Hafnium dioxide is considered to be a promise for replacing the silicon dioxide due to the high dielectric constant, good thermal stability in direct contact with silicon substrates and low leakage current [6].

10.3 Intel®’s High-k MOSFET Electrical and Physical Parameters

Table 10.3 describes in detail the geometrical and electrical properties of the device, as reported by the manufacturer [11, 14].

Where LG is the Gate length, \( Tox \) is the oxide layer thickness \( I_{TH} \) is the average leakage current, \( x_{dD} \) and \( x_{ds} \) are the depth of the depletion region associated with the Drain and Source respectively, ρ is the electrical conductivity of the \( HfO_{2} \) at 1100 °C, \( V_{GS}\) is the gate-source voltage, \( I_{D} \) is the Drain current, \( V_{TH} \) is the threshold voltage, \( \varepsilon_{r}\) is the relative permittivity of \( HfO_{ 2} \) and \( V_{DS} \) is the Drain-Source voltage.

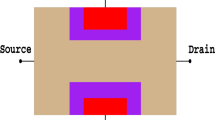

From the data at Table 10.2, it is possible to recognize that for the 45 nm gate length High-κ MOSFET, the oxide thickness \( T_{ox} \) has reach the size of a few atomic layers. This device also is considered to be a short channel device, because its gate length (L g ) is in the same order of magnitude as \( x_{dD} \) and \( x_{ds} \), which sets up a scenario where the electrical field along the y axis (see Fig. 10.1) is about 105 V/cm for N-channel High-κ MOSFET at \( V_{DS} \; = \; 5V \) with \( L_{g} = 100 {\text{nm}} \) [14], and where phenomena like carrier tunneling, Drain-Induced Barrier Lowering (DIBL), Channel Length Modulation (CLM), among others known as Short Channel Effects (SCE), are most likely to occur. SCE have not been fully implemented on modern MOSFET compact models mainly due to top-down approaches that make difficult to reach a particle-size level of detail in device analysis and authors considered the development of a model that accurately could describe the carrier transport in the presence of such phenomena.

10.4 A Model for Carrier Quantization

The model is based on the coupled Poisson-Schrodinger equations in order to describe the electron transport along the channel. The proposed procedure starts from Poisson equation describing 2-D potential distribution \( \phi ( {\text{x,y)}} \) along the channel.

Where q is the electron charge, \( \varepsilon_{{HFO_{2} }} \) is the electrical permittivity of Hafnium dioxide, \( {\text{N}}_{\text{A}} (x) \) is the density of acceptors along the channel and \( n({\text{x, y}}) \) is the electron concentration along the channel.

In the scenario in which the charge is quantized, the continuous conduction band is now divided into two sub-bands. The wave function of each sub-band is given by the Schrödinger equation:

Where \( \hbar \) is the reduced Planck constant, \( \psi_{i} (x,y) \) is the carrier wavefunction on the ith subband, m is the electron mass and the eigenvalue \( E_{i} \) is the energy level associated with wavefunction \( \psi_{i} \) [15]. Carrier’s confinement is higher in the direction perpendicular to the Gate [16], so the one-dimensional Schrödinger equation can be used to assess the problem. Assuming a MOS structure with uniform potential distribution along the direction perpendicular to the Gate, the component in y axis can be removed from Poisson’s equation, and the problem is reduced to coupled one-dimensional equations of Schrödinger-Poisson:

Where \( Q_{inv} ,_{i} \) denotes the inversion charge on the ith subband. Reaching an analytical solution for this pair of equations is not an easy task; however, numerical simulations provide some insights into reaching this solution.

Figure 10.1 shows the results of simulating the carriers population per sub-band, using the parameters of Intel®’s High-κ MOSFET. \( N_{d} = 1^{18} {\text{cm}}^{3} \), \( T_{ox} = 1\;{\text{nm}} \) and κ = 22.

From Fig. 10.2, as we move on the voltage range between 0V<\( {\text{V}}_{\text{gs}} \)<3V, it is possible to see that between 45 and 85 % of the carriers are located in the lower sub-band \( E_{1,1} \), so only the lowest level of energy can be considered to approach to the analytical solution. With that approximation, the pair of Eqs. (10.3) and (10.4) for each valley or group of sub-bands associated with the crystal structure of the interface Si-\( Hfo_{2} \) are reduced to:

Numeric simulation of carrier populations per sub-band, simulation conducted using SCHRED [18] with parameters \( T_{ox} \) = 1 nm, T = 300°K and \( N_{d} \) = \( 10^{ - 18} {\text{cm}}^{ - 3} \)

Sub-bands wavefunctions, simulation conduced on SCHRED [20]

Where i denotes each one of the two valleys where the lowest energy level will be calculated.

Using calculus of variations, wave functions are assumed to have a shape similar to \( \psi_{1,1} \) and \( \psi_{1,2} \) , thereby ensuring a good level of accuracy for the calculated energy levels [19]. The next step is to integrate the simplified Poisson equation from bulk to surface and also, in order to find the lowest expression of energy, expected value of the Hamiltonian of the wave function \( \psi_{1,1} \) is calculated obtaining the following expression:

A simulation of the sub-bands wave functions (shown in Fig. 10.3), provides elements to reach an analytical solution for Eq. (10.7)

Simulation of Fig. 10.2 shows that the peak of carrier density is a few nanometers (no more than 5 nm) below the channel surface, which leads to approximate:

Then, this approximation is applied and the result is factorized, based on the parameter of proportionality γ. According to the variations method, \( \alpha_{1} \) and \( \alpha_{2} \) should minimize the energy level, i.e:,

Calculating the derivatives, we obtain the expressions for \( \alpha_{1} \) and \( \alpha_{2} \) then the mean value of γ is obtained. Finally, replacing the values obtained and the approximations described above, leads to the expressions for \( E_{1,1} \) and \( E_{1,2} \):

Verification of model accuracy is performed by comparing its results with SCHRED simulation of energy levels for sub-bands \( E_{1,1} \) and \( E_{1,2} \) as shown in Fig. (10.4).

Accuracy of the quantization model obtained, allows us to approach to a short channel I-V model that takes into account the quantization of charge that occurs at this scale, and enables some approximations for that model.

10.5 I-V Short Channel Model

The fact that, in short channel devices, there is no complete control of the channel charge is an indicator that \( E_{y} \) is not negligible compared with \( E_{x} \) and the effects associated with this behavior should be incorporated in a compact model. In terms of \( I_{d} \), the most significant effect to be included is velocity saturation, that may result in reduced effective drain saturation current. One of the empirical relations in use to model the dependence of carrier velocity \( V_{d} \) with respect to \( E_{x} \) was adopted for this step [19]:

Where \( E_{c} \) is defined as the intersection of the \( v_{d} = \mu V_{GS} E_{x} \) line and an imaginary horizontal asymptote, as can be seen on Fig. 10.5 (Figs. 10.5, 10.6, 10.7).

Magnitude of carrier velocity in the inversion layer versus magnitude of the longitudinal component of the electric field [17]

Transient analysis using Orcad PSICE™ 9.1 for three signals labeled. 1 Output voltage of native N-MOS MOSFET with High-k transistor physical and electrical parameters running under BSIM 4.4 model, 2 output of ABM blocks running model expressions obtained with this methodology, 3 input voltage signal with amplitude of 5 V and 60 Hz frequency. This results shows higher accuracy of simulations of a common circuit configuration compared with performance of state-of-the-art compact models, like BSIM 4.4

The first step is to find an expression for \( I_{d} \) in non-saturation regime \( I_{dsn} \) \( E_{x} \) is expressed as the differentials of the potential between the polarization of the inversion layer and the end of the piece. The result of integrating these differences along the channel is presented in Eq. 10.12.

Where W is the channel width and \( C_{ox} \) is the oxide capacitance. For the expression in the saturation region, it is necessary to include the effect of Channel Length Modulation (CLM) [18] finding the value of \( V_{ds} \) at which saturation occurs, so the expression of \( I_{ds} \) in presence of velocity saturation is given by:

10.6 Compact I-V Short Channel Model

Finally, to obtain a unified expression of \( I_{d} \) in presence of velocity saturation, it becomes necessary to incorporate the smoothing equation of \( V_{ds} \):

Thus, \( V_{deff} \) is used to replace \( V_{ds} \) in the \( I_{ds} \) expression, as well as the early effective voltage \( V_{Aeff} \) to incorporate CLM in the unified expression, that is then obtained:

With

\( I_{deff} = \left( {1 + \frac{{V_{DS} - V_{deff} }}{{V_{Aeff} }}} \right)I_{ds0} \) and \( V_{Aeff} = \frac{{E_{SAT} L_{eff} (E_{SAT} L_{eff} + V_{DS} )}}{{\xi v_{deff} }} \)

10.7 Comparison of Model Equations with Intel® Data

With the physical and electrical parameters given in Table 10.2 and those obtained by the Arizona State University Predictive Technology Model for 45 nm technology node [20], we compare the results using the IV model expressions obtained from the curve provided by the manufacturer (see Fig. (10.6)) [21].

The results show a correlation coefficient R² equal to 98 % and an average error of 0.33 %, indicating a relatively strong relationship between the data obtained by the model and those reported by the manufacturer. This level of accuracy, allows us to get to the next stage, which is the model equations testing in SPICE.

10.8 Testing the Model Expressions in a SPICE Circuit Simulation

To ensure the portability of the model for any SPICE-based simulator, obtained model expressions were represented by using Analog Behavioral Modeling blocks, included in Orcad© PSPICE 9.1. Those blocks have a maximum of three inputs and one output of voltage or current. They use mathematical relationships to model a circuit segment. When connected in cascade, and at netlist generation stage, the simulator concatenates the blocks to make the entire expression. Equations are entered in the model and tested in a configuration of half-wave rectifier-inverter, compared with an N-channel MOSFET in the same configuration, whose electrical and physical parameters have been replaced by the ones of Intel’s High-k MOSFET to verify the performance of BSIM4 model at sub-50 nm scale and the operation of the model obtained in a circuital implementation. Simulation (Fig. (10.7) )shows the degradation in the description of the MOSFET behavior in sub-threshold regime by BSIM4 model and a good performance of the equations obtained for the model.

10.9 Conclusions and Recommendations for Future Work

A compact model for High-κ 45 nm MOSFET was described including the short channel effects present at nanoscales. The methodology has consolidated in SCORM-compatible learning material (Sharable Content Object Reference Model), which is available at https://nanohub.org/resources/10024.

Future work could include additional effects such as temperature dependence and body effects. The model could be simplified to have as few parameters as possible, avoiding a great number of ABM blocks.

References

Moore G (1965) Cramming more components onto integrated circuits. Electronics 38(8):114–117

University of California, Irvine, Department of Electrical Engineering and Computer Science, HSPICE User’s Manual, 2007

Vladimirescu A, Lius S (1980) Simulation of MOS using SPICE2. Electronics Research Laboratory, University of California, Berkeley

Mississippi State University (2005) MOSFET devices and their SPICE models. Department of Electrical and Computer Engineering

Ytterdal T, Cheng Y, Fjeldly T (2003) Device modeling for analog and RF CMOS circuit design, Wiley online library

Ávila A, Espejo D (2011) A SPICE-compatible model for intel®’s high-k 45 nm MOSFET. Lecture notes in engineering and computer science: proceedings of the world congress on engineering and computer science 2011, WCECS 2011, San Francisco, USA, pp 762–765, 19–21 October

Inaba S, Okano K, Izumida T, Kaneko A, Kawasaki A, Yagishita A, Kanemura T, Ishida T, Aoki N, Ishimaru K, Suguro K, Eguchi K, Tsunashima Y, Toyoshima Y, Ishiuchi H (2006) FinFET: the prospective multi-gate device for future SoC applications. In: Proceedings of the 36th European solid-state device research conference

Song J, Choi W, Park J, Lee J, Park B (2006) Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans Nanotechnol 5(3):186–191

Auth C, Capellani J, Dalis A, Ghani T, Mistry K (2009) 45 nm high-k + metal gate strain-enhanced transistors. Intel Press

Intel™ Press (2008) A 45 nm logic technology with high-k + metal gate transistors, strained silicon, 9 cu interconnect layers, 193 nm dry patterning, and 100 % Pb-free packaging

Hergenrother JM et al (2000) The vertical replacement-gate (VRG) MOSFET: a high performance vertical MOSFET with lithography-independent critical dimensions IEEE Electron Devices Meeting

Kavalieros J, Doyle B, Datta S, Dewey G, Doczy M, Jin B, Lionberger D, Metz M, Rachmady W, Radosavljevic M, Shah U, Zelick N, Chau R (2006) Tri-gate transistor architecture with high-k gate dielectrics, metal gates and strain engineering. Symposium on VLSI technology digest of technical papers

Doyle BS, Datta S, Doczy M (2003) High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett 24(4):263–265

Bohr M, Chau R, Ghani T, Mistry K (2007) The high-k solution. IEEE Spectr 44(10):23–29

Ming L (2007) Semi-empirical device model for nanoscale MOSFET. PhD thesis, Universiti Teknologi Malaysia

Wang L (2006) Quantum mechanical effects on MOSFET scaling limit. PhD thesis, School of Electrical and Computer Engineering, Georgia Institute of Technology

Hareland SA, Manassian M, Shih WK, Jallepalli S, Wang H, Chindalore GL, Tasch A, Maziar CM (1998) Computationally efficient models for quantization effects in MOS electron and hole accumulation layers. IEEE Trans Electron Devices 45(7):1487–1493

Vasileska D, Ahmed S, Mannino M, Matsudaira A, Klimeck G, Lundstrom M SCHRED, available on http://nanohub.org/resources/schred

Ren Z (2001) Nanoscale MOSFETs: physics, simulation and design. PhD thesis, Purdue University

University of California, Berkeley, Arizona State University, Berkeley Predictive Technology Model, available on http://ptm.asu.edu/modelcard/LP/45nm_LP.pm, retrieved on 26/04/10

Mistry K, Allen C, Auth C (2007) A 45 nm logic technology with High-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning and 100 % free Pb packaging, IEDM

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer Science+Business Media Dordrecht

About this chapter

Cite this chapter

Rodriguez, D.E.E., Bernal, A.G.Á. (2013). Development of a Bottom-up Compact Model for Intel®’s High-K 45 nm MOSFET. In: Kim, H., Ao, SI., Rieger, B. (eds) IAENG Transactions on Engineering Technologies. Lecture Notes in Electrical Engineering, vol 170. Springer, Dordrecht. https://doi.org/10.1007/978-94-007-4786-9_10

Download citation

DOI: https://doi.org/10.1007/978-94-007-4786-9_10

Published:

Publisher Name: Springer, Dordrecht

Print ISBN: 978-94-007-4785-2

Online ISBN: 978-94-007-4786-9

eBook Packages: EngineeringEngineering (R0)