Abstract

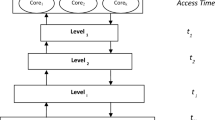

The one-level data cache [1], which is optimized for bandwidth, eliminates the overhead to maintain containment and coherence. And it is suitable for future large-scale SMT processor. Although the design has good scalability, large-scale SMT architecture exacerbates the stress on cache, especially for the bank-interleaved data cache referred to in paper [1]. This paper proposes a dynamic partitioning method of scalable cache for large-scale SMT architectures. We extend the scheme proposed in [2] to multi-banking cache. Since memory reference characteristics of threads can change very quickly, our method collects the miss-rate characteristics of simultaneously executing threads at runtime, and partitions the cache among the executing threads. The partitioning scheme has been evaluated using a modified SMT simulator modeling the one-level data cache. The results show a relative improvement in the IPC of up to 18.94% over those generated by the non-partitioned cache using standard least recently used replacement policy.

Access provided by Autonomous University of Puebla. Download to read the full chapter text

Chapter PDF

Similar content being viewed by others

Keywords

References

Mudawar, M.F.: Scalable cache memory design for large-scale SMT architectures. In: Proceedings of the 3rd Workshop on Memory Performance Issues: In Conjunction with the 31st International Symposium on Computer Architecture, June 20, pp. 65–71 (2004)

Suh, G.E., et al.: Dynamic partitioning of shared cache memory. Journal of Supercomputing 28(1) (2004)

Tullsen, D.M., Eggers, S.J., Levy, H.M.: Simultaneous Multithreading: Maximizing On-Chip Parallelism. In: Proceedings of the 22nd Annual International Symposium on Computer Architecture, Santa Margherita Ligure, Italy (June 1995)

Eggers, S.J., Emer, J.S., Levy, H.M., Lo, J.L., Stamm, R.L., Tullsen, D.M.: Simultaneous Multithreading: A Platform for Next-generation Processors. IEEE Micro, 12–18 (September/October 1997)

Marr, D.T., Binns, F., Hill, D.L., et al.: Hyper-Threading Technology Architecture and Microarchitecture. Intel Technology Journal 6(1), 4–15 (2002)

Preston, R., et al.: Design of an 8-wide superscalar risc microprocessor with simultaneous multithreading. In: IEEE International Solid-State Circuits Conference, p. 344 (2002)

Henning, J.L.: SPEC CPU2000: Measuring CPU performance in the new millennium. IEEE Computer (July 2000)

Chiou, D.T.: Extending the reach of microprocessors: Column and curious caching. Ph.D. Thesis, Massachusetts Institute of Technology (1999)

Chiou, D., Rudolph, L., Devadas, S., et al.: Dynamic Cache Partitioning via Columnization. CSG Memo 430. MIT

Stone, H.S., Turek, J., Wolf, J.L.: Optimal partitioning of cache memory. IEEE Transactions on Computers 41(9) (1992)

Wilson, K.M., Olukotun, K., Rosenblum, M.: Increasing Cache Port Efficiency for Dynamic Superscalar Microprocessors. In: Proc. 23rd Ann. Int’l Symp. Computer Architecture, pp. 147–157 (May 1996)

Gonçalves, R., Ayguadé, E., Valero, M., Navaux, P.: A Simulator for SMT Architectures: Evaluating Instruction Cache Topologies. In: 12th Symposium on Computer Architecture and High Performance Computing, pp. 279–286 (October 2000)

Austin, T., Larson, E.: SimpleScalar: An infrastructure for computer system modeling. IEEE Computer 35(2), 59–67 (2002)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Jun-Min, W., Xiao-Dong, Z., Xiu-Feng, S., Ying-Qi, J., Xiao-Yu, Z. (2013). Dynamic Partitioning of Scalable Cache Memory for SMT Architectures. In: Zhang, Y., Li, K., Xiao, Z. (eds) High Performance Computing. HPC 2012. Communications in Computer and Information Science, vol 207. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-41591-3_2

Download citation

DOI: https://doi.org/10.1007/978-3-642-41591-3_2

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-41590-6

Online ISBN: 978-3-642-41591-3

eBook Packages: Computer ScienceComputer Science (R0)