Abstract

This chapter covers selected issues related to lanthanides (or lanthanoids) used in oxide gate dielectrics. In general, lanthanides offer key material property advantages for gate dielectric applications. These include high dielectric constants, stable amorphous silicate (or ternary) phases, thermodynamic stability with Si, interface properties allowing threshold voltage tuning, and crystalline properties making possible epitaxial growth on Si and other semiconductors. Although not as heavily researched as Hf-based materials, lanthanide materials continue to hold promise for device scaling on Si, and as dielectrics on other high-mobility semiconductors.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

9.1 Introduction to Lanthanide Dielectrics

Lanthanides (or lanthanoids, or rare-earths) have atomic properties making them key components for materials designed for a wide range of material properties. For example, lanthanides are key components for enhancing magnetic, optical, catalytic, and electrical properties of many materials. The dielectric properties of their respective oxides make them of interest as candidates for high dielectric constant (high-k) gate dielectrics. For example, initial interest was generated by binary compounds such as lanthanum oxide or lanthana (La2O3) and ternary compounds such as lanthanum aluminate (LaAlO3) and lanthanum scandate (LaScO3) found to have dielectric constants (k) in the range of 25–30, and sufficiently large band gaps for use as dielectrics on silicon, in the 5.0–6.0 eV range [1–3]. Additionally, from a thermodynamic viewpoint, it appears that lanthanide oxides are chemically stable in contact with Si [2]. Additional reasons fueling interest in these materials as metal–oxide–semiconductor field-effect transistor (MOSFET) gate dielectrics include the following: (1) many of these lanthanide oxide materials have not been comprehensively studied in bulk form, certainly not the many potential ternary alloy options; (2) the properties of metastable amorphous thin films of these binary or ternary alloys were in many cases unknown; and (3) the fact that some properties are ‘tunable’ as one moves across the series due to f-orbital filling levels opens possibilities for desirable properties to be obtained.

This interest in lanthanides in the arena of high-κ gate dielectrics has continued to strengthen as it has been shown that lanthanide materials: can provide MOSFET threshold voltage (VT) control to achieve band-edge values for n-channel devices [4]; and are promising as dielectrics on alternate channel materials such as GaAs or other III–V compounds [5], as lanthanides are chemically similar to group III elements in some respects.

As is the case for all materials and applications, a host of factors must be considered when selecting particular materials for a given application. Although the lanthanides are similar in many respects (all have electronegativity values of ~1.1, most have +3 valence), and have some properties which vary smoothly across the series (such as ionic radius), they differ in various ways. For example, for stable dielectric properties which are insensitive to electric field or temperature or oxidation environment, it is typically essential to have cation elements having a single stable oxidation state. This would favor the use of La, Nd, Gd, Dy, Ho, Er, and Lu which have stable +3 oxidation states (disregarding the radioactive Pm) over the other lanthanide elements which have some tendency towards mixed +3 and +2 oxidation states. Furthermore, La, Gd, and Lu might be grouped due to their similarity in electron configuration, with 5d16s2 available bonding electrons and their f-orbital being empty, full, or half-filled; however, other properties differ along this group such as ionic radius (decreasing), and melting point (increasing). Thus, we will discuss only some key lanthanide elements primarily from those listed above with a single oxidation state, with the hope of covering key materials having properties of interest as gate dielectrics.

9.2 Lanthanide Materials Properties

Most of the known properties of lanthanide dielectrics derive from studies on bulk crystalline materials, to be briefly summarized here, with some information related to thin films included as appropriate. Discussed here are some prerequisite dielectric properties for use as a gate dielectric; detailed issues specific to particular thin film gate stacks will be discussed later.

9.2.1 Physical/Structural Properties

As covered in reviews by Adachi and Imanaka [6] and others [7, 8], all the lanthaniods oxidize readily, typically forming +3 valence sesqiuoxide (Ln2O3) lanthanide compounds, with melting points ranging from 2,200 to 2,500 °C. The f-orbital electrons do not participate directly in chemical bonding, but do facilitate valence changes to +2 or +4 that occur in some elements such as Ce, Pr, or Tb. F-orbital electrons also affect other properties, such as magnetic or optical properties, not discussed here.

In the presence of water vapor, many of these oxides will form lanthanide hydroxides, with the hydroxide tendency decreasing with increased lanthanide atomic number, in general [6]. For example, La2O3 readily forms hydroxides [9], while for Dy2O3 or Ho2O3, hydroxide formation is minimal [7]. Carbonates will also form, but these are more limited to the outer surfaces. Hydroxide and carbonate formation will generally result in a lower density material, with lower dielectric constant (k), and higher loss and leakage. Thus in situ capping of these binary dielectrics is critical, and partly explains the desire to move towards ternary compounds such as silicates and aluminates, which are very stable with respect to atmospheric exposure [9, 10].

The binary lanthanide sesquioxides can exist in 5 crystal structure variations, as shown in the Fig. 9.1 phase-relationship diagram adapted from Adachi and Imanaka [6]. For temperatures of interest here (up to ~1,000 °C) typically either a hexagonal (termed ‘A’ form) or a cubic (termed ‘C’ form) phase are observed. Table 9.1 summarizes key materials and dielectric properties of select lanthanides. Below ~400 °C the cubic phase has been generally believed to be the stable phase for all lanthanides [6], but the hexagonal ‘A’ phase persists in practice for La through Nd (for example, Zhao et al. [11] and Schroeder et al. [12]). Marsela and Fiorentini [13]. have shown by structure calculations that the hexagonal phase of La2O3 has 0.2 eV lower energy per formula unit than the cubic bixbyite phase, and thus expected to be the equilibrium phase. It appears that the cubic bixbyite phase is only observed for La2O3 if impurities or appropriate nucleation sites are present to stabilize this structure, as occurs for some thin films formed by decomposition of molecular precursors [14]. In the hexagonal ‘A’ phase (La2O3 through Nd2O3), the cations have a coordination number of 7. The cubic ‘C’ phase is the bixbyite structure, in which cations are 6-fold coordinated in a matrix which can be described as having ordered vacant sites on the oxygen sub-lattice.

Phase relationship diagram of binary lanthanide sesquioxides (adapted from Adachi [6])

Ternary compounds are typically found in perovskite-like orthorhombic (pseudo-cubic) crystal structures (such as LaAlO3) or pyrochlore phases (La2Hf2O7). Lanthanide silicates may exist in a variety of crystalline phases, but typically in either Ln2SiO5 or Ln2Si2O7 compositions [15, 16].

For use as a gate dielectric, the tendency has been to focus on amorphous dielectrics (following on the success of SiO2 and SiOxNy), and to attempt to frustrate dielectric crystallization, as defects within grains or at the grain-boundaries have been linked with reliability degradation [17]. For standard (gate first) silicon-based transistor application, specific materials-related properties of interest are: (1) the amorphous phase stability temperature; and (2) the interface properties of lanthanides in contact with silicon or silicon dioxide.

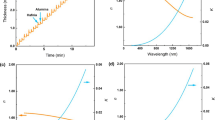

From a thermodynamic viewpoint, the lanthanide oxides appear to be very stable oxides, with very large (negative) enthalpy of formation [6]. From available data, these oxides appear to be stable in contact with Si [2]. However, in the presence of excess oxygen, the interface will oxidize to SiO2, and the mixing of silica and lanthanide oxides to form silicates is energetically favorable, as Liang et al. [16], Marsela and Fiorentini [13] discuss. The mixing of silica and lanthanide oxides to form a silicate lowers the overall free energy compared to having separate oxide layers, although reaction temperatures will depend on diffusion coefficients and other kinetic considerations. A comparison of amorphous La and Hf silicate crystallization temperatures and dielectric constants [1] are shown in Fig. 9.2. The higher temperature amorphous phase stability favors amorphous lanthanum silicate over Hf silicates. Additionally, the crystallization of HfSiOx dielectric corresponds with a decomposition reaction (phase separation) [18] resulting in low-k SiO2 formation, while the lanthanide-silicates maintain a silicate phase without phase-separation [18]. Lanthanide silicates are also more stable with respect to atmospheric exposure [9] than the binary oxides, and the silicate reaction can be used to minimize the low-k silica interface layer thickness in the stack [19]. Thus the silicate is in many respects advantageous compared to the binary lanthanide. For a gate-last approach, with limited process temperatures and less restriction on the amorphous phase stability or interface reactivity, dielectrics with higher k than the silicates may be utilized.

Comparison of La and Hf silicate crystallization T and dielectric constant with silica content (adapted from Kingon et al. [1])

9.2.2 Electrical/Dielectric Properties

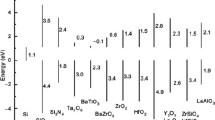

In their crystalline forms, binary lanthanides have band gaps and dielectric constants making them attractive choices as gate dielectrics; select values are listed in Table 9.1 (some data is that of amorphous films, when crystalline reference data is not readily available). La2O3 has possibly the largest dielectric constant (~23–28), with the expected dielectric constants in the ~12–15 range for most of the binary oxides [20]. However, some reports for Gd2O3 [21], CeO2 [22] and Pr2O3 [23] describe dielectric constants in the 20–30 range or higher, presumably due to effects of crystal structure and orientation, requiring further validation. Scarel et al. [24] reports that hexagonal La2O3 has a k of 27, whereas the cubic phase gives a value of 17. This may be the key explaining why many different values of k are reported, especially for the lanthanides composed of La, Ce, Pr, and Nd, which can exist in either hexagonal or cubic structures, in various orientations. Indeed, the higher atomic number lanthanides of the cubic bixbyite phase (and bixbyite Sc2O3 and Y2O3) almost universally have k from 10 to 15, indicating that crystal structure may be more influential than lanthanide atomic number for k determination.

As one moves across the lanthanide binary oxide series, the band-gap has a maximum value of about 5.5–6.0 eV for La2O3, Gd2O3, and Lu2O3, corresponding to empty, half-filled, or a full f-orbital. Thus, due to dielectric constant and band-gap, La-based materials have been most heavily researched, although due to its hygroscopic nature some researchers have focused on other lanthanides such as Gd or Lu which are more moisture resistant, or related Sc and Y compounds having similar band gaps [25, 26] although lower k values.

Although somewhat more complex when considering film growth and composition control, ternary compounds typically offer higher temperature amorphous phase stability [1], as shown in Fig. 9.2 for silica alloying of La2O3 and HfO2. This has been believed to be the key for maintaining smooth interfaces and low leakage after source/drain activation anneals. Silicates also offer dielectrics with wider band gap, but lower dielectric constant, shown in Fig. 9.2 comparing La and Hf silicate dielectric constants as the SiO2 content is increased. As shown in Fig. 9.2, these amorphous dielectrics (processed below the crystallization temperature), show dielectric constant scaling nearly following a simple component mixing rule considering density effects, between the silica and lanthanide end points [1]. Mixing binary lanthanides with other lanthanides or group III or IV binary oxides, besides Si, typically also increases the amorphous phase stability, while producing slightly higher dielectric constants, with little change in the band gap. Examples include lanthanide scandates [27], hafnates [28], aluminates [29–31], and mixed lanthanides such as LaLuO3 [32, 33]. Additionally, for epitaxial dielectric growth, alloying can often reduce lattice mismatch with the substrate. For all these reasons, ternary compounds offer more ultimate promise than binary lanthanide oxides. The dielectric properties of La2O3 based ternary compounds—LaYO and LaAlO—have been briefly analyzed in Sect. 10.4.

9.3 Thin-Film Deposition and Processing

Commonly used growth techniques for lanthanide films include sputtering, thermal or e-beam evaporation (physical vapor deposition (PVD) techniques), and more recently chemical vapor deposition (CVD) techniques such as atomic layer deposition (ALD). A comprehensive listing of the growth techniques used by various researchers for lanthanide materials can be found elsewhere [34]. The gate dielectric, on silicon substrates, is deposited on either hydrogen terminated (hydrofluoric acid treated, or HF-last) oxide-free Si (001), or an ‘engineered’ SiO2 or SiOxNy surface layer for interface defect minimization and channel mobility optimization. Thin film growth techniques typically must not damage either of these surfaces, so sputtering techniques are less preferable to other options. A key issue in general for lanthanides is the hygroscopic nature of the materials, especially La through Nd. This means that special precaution against atmospheric (water vapor and carbon dioxide) exposure is a critical issue for all deposition techniques. Additionally, magnetic properties of many of the lanthanide metals can affect the deposition process if using metallic sources. Some features specific to each deposition approach are discussed below. The basics of the deposition techniques for gate dielectrics have been described also in Chap. 4: atomic layer deposition (Sect. 4.2.2); precursors (Sect. 4.2.3); and physical vapor deposition (Sect. 4.2.4).

9.3.1 Physical Vapor Deposition

Utilizing physical vapor deposition (PVD) techniques, lanthanide-based gate dielectrics films have been reported using sputtering [11], pulsed-laser ablation deposition (PLD) [35], e-beam evaporation [36, 37], or thermal evaporation from effusion cells in molecular beam epitaxy (MBE) systems [10, 31]. Details are rarely given in the research reports, but materials must be carefully handled. Source materials should be purchased sealed in an inert gas ambient. As the lanthanide metals are very reactive with oxygen and water vapor, metal powders will quickly form oxides and hydroxides, and thus larger pieces of elemental materials should be used for e-beam or effusion cell evaporation source charges. For e-beam evaporation of La, Al2O3 crucibles appear to be satisfactory [38], while we have found W crucibles effective for effusion cells. Although La melts at ~920 °C, a vapor pressure of 10−4 torr is not reached until 1,368 °C; practically we find that an effusion cell temperature of ~1,700 °C is necessary for La evaporation. The other lanthanides tend to evaporate more easily (typically 200–400 °C lower [38]), while oxides of any of the lanthanides typically require evaporation temperatures of 1,400–1,600 °C, with O loss occurring during heating. For effusion cell evaporation or sputtering of elemental lanthanides, reactive evaporation in oxygen ambient is sufficient to deposit oxide films. Growing the elemental lanthanide and subsequently oxidizing is an option, but rapid interface reactions can produce silicides and roughened interfaces [39]. During e-beam evaporation, it may be problematic to operate in high enough oxygen pressures, since the electron emission decreases with oxygen increases. For PLD or sputtering, elemental or oxide target materials may be used (although oxide targets require RF sputtering due to the insulating target). Again, even oxide targets convert to hydroxide very easily, and care must be taken to minimize atmospheric exposure.

9.3.2 Chemical Vapor Deposition and Atomic Layer Deposition

The advent of atomic layer deposition (ALD) has brought the general technique of chemical vapor deposition to the realm of monolayer growth control, and thus is of key importance for the growth of nm-scale gate dielectrics. This is an emerging field in relation to lanthanide oxide growth, and new or recently formulated precursor chemicals have made possible successful implementation of ALD for these compounds. Ultimately ALD is expected to be the technique of choice for virtually all high-κ dielectrics, although lack of suitable precursors has resulted in more exotic dielectric materials being studied initially by PVD techniques, with appropriate ALD precursor materials closely following.

A variety of precursors for lanthanides have been utilized by various groups [34]. Aspinall et al. [40] report that complexes of the early (lower atomic number) lanthanides with the donor-functionalized alkoxide ligand mmp (Ln (mmp)3 complexes; mmp referring to methoxy-methylpropanol) are excellent precursors for metal–organic CVD or ALD; while Paivasaari et al. [14]. utilize volatile β-diketonate type chelates Ln (thd)3. Others report the use of various Ln-cyclopentadienyl complexes (Ln (Cp)3) [41, 42], which result in uniform deposition at low rates, and may be advantageous due to their low melting temperatures [41].

Ozone is often used as an oxidant (instead of H2O or O2) to reduce C content and hydroxide formation [14, 41–43]. Complex chemistries are at play, and understanding the chemistries of the ALD process remains an area of extensive research, beyond the extent of this chapter. However, using an O3 oxidant, these Ln-based ALD precursors can be utilized to give high-quality low EOT (0.68 nm) device properties for La-capped HfO2 dielectrics [41].

9.4 Lanthanide-Based Dielectric Gate Stacks

9.4.1 Lanthanum Oxides and Silicates

Extensive research has been performed on La-based oxides and silicates, as it was recognized [1] that these had the most promising values of dielectric constant, band gap, and amorphous phase stability. Key to the successful application of high-κ materials is the ability to fabricate the transistor gate with capacitance values equivalent to sub-nm SiO2 oxide thickness. When utilizing high-κ dielectrics, gate capacitance properties are compared by referencing to the dielectric properties of ideal SiO2 dielectric, thus determining a capacitor’s ‘equivalent silica oxide thickness’ (EOT). Making use of the silicate reaction provides a route towards aggressive sub-nm EOT scaling [19] by thinning the SiO2 interface layer (IL). La-based dielectrics have resulted in some of the lowest EOT gate stacks reported (0.5–0.75 nm) when processed under moderate temperatures [19, 36, 39, 41]. Discussed below are properties of La2O3 and lanthanum silicate (LaSiOx) gate stacks deposited by reactive evaporation of La in an O2 ambient, typically on a thin SiO2 oxide on Si.

9.4.1.1 Gate Stack Electrical Properties

One approach to obtain low EOT devices is to deposit a thin lanthanide oxide on a silica chemical oxide, and anneal to allow interface SiO2 consumption by the silicate phase formation. Capacitance versus gate voltage, and gate leakage data are shown in Fig. 9.3a, b for metal insulator semiconductor (MIS) capacitors with e-beam evaporated 60 nm Ta electrodes, capped with 60 nm W and reactive-ion etched (RIE) [19]. The data are shown for a bilayer dielectric of 1.6 nm La2O3 deposited on a ~0.8 nm SiO2 chemical oxide on Si, measured at 1 MHz, with a 50 mV signal. As the gate stack undergoes a post-metallization anneal (PMA), the stack EOT decreases from an initial value of 1.57–0.69 nm after 20 s at 400 °C in N2 [19]. Also, the gate leakage correspondingly decreases, as in Fig. 9.3b. As corroborated by the cross-sectional transmission electron microscope (TEM) image, the EOT lowering corresponds to dielectric thinning, caused by a combination of silicate formation, densification, and some oxygen gettering of the SiO2 layer. Note the flatband voltage decrease as the silicate reaction proceeds, which may explain the flatband voltage shifts observed by Kuriyama et al. [44] for post-deposition anneal (PDA) of La2O3 on HF-last Si.

Figure 9.4a, b shows high-angle annular dark-field (HAADF) images and La electron energy loss spectra (EELS) peak intensity of the gate stack before (a) and after (b) the 400 °C 20 s PMA. The initial SiO2 interface layer (dark in Fig. 9.4a HAADF) is seen to disappear after the anneal (Fig. 9.4b), corroborated by the La EELs signal uniformity after annealing. The lanthanum silicate bonding is determined by X-ray photoelectron spectroscopy (XPS) analysis [10] of La 3d and O1 s peaks in films with no metal capping; O gettering by the gate metal is a possible secondary EOT reduction mechanism, in conjunction with the silicate formation. The key aspect is that this silicate reaction can be a route to achieve low (sub nm) EOT, by minimizing SiO2 IL thickness, ideal for the gate-last fabrication processes.

HAADF images and corresponding EELS La M 4,5 -edge intensity (increasing to the right), with position indicated as distance from the Si interface (taken as zero). The figures show La2O3/SiO2 bilayer gate stacks (a) as-deposited, and (b) after 20 s RTA in N2. SiO-2 interlayer is consumed by gate stack anneal

Under only low temperature processing [without forming gas (H2 in N2) anneal (FGA)], although low EOT can be obtained, high fixed charge level and high interface trap density (Dit) are observed as shown in Fig. 9.5. In Fig. 9.5a frequency dispersion comparing 100 kHz, 1 MHz, and an ‘ideal’ HF curve are shown, revealing a sharp capacitance (C) ‘hump’ indicative of a localized trap state. Figure 9.5b shows the 1 MHz, 50 mV C–V and conductance versus voltage (G–V) signals, showing that the C ‘hump’ correlates with the conductance peak as expected. Comparing the frequency dispersion of low temperature processed LaSiOx (1.4 nm EOT) on p- and n-type Si, we note a much greater frequency dispersion on n-type Si than on p-type Si, and determine that electron trapping is much more prevalent than hole trapping [45]. The lanthanum silicate reaction process is believed to result in this high interface defect density, under low temperature processing. This is expected to be due in part to the low temperature (forming an imperfectly bonded silicate), and partly due to the silicate reaction virtually eliminating the SiO2 at the Si interface, and new La–O–Si interface bonding taking its place at (or very near to) the Si interface. In general, interface bonding constraints due to differing valence and O coordination number will tend to increase trap densities when introducing lanthanide oxides (or silicates) on Si or SiO2/Si [46].

Typical gate-first processing requires that the complete gate stack undergo a high temperature anneal. Results for PMA of gate stacks which have received a prior 400 °C in situ silicate reaction anneal (to form silicate before gate metal deposition) are shown in Fig. 9.6. For capacitors with W-capped TaN electrodes, PMA anneals up to 1,000 °C for 5 s (simulating the source/drain anneal) result in a gradual increase in EOT, from 0.6 to 1.0 nm, as shown in the Fig. 9.6a C–V curves (1 MHz, 50 mV signal). In this case, starting with a silicate, further anneals grow an additional SiO2-rich interface region [19] if excess O is available, often coming from the gate metals such as W [47]. This lowers the interface state density and the total stack charge, as revealed by the C ‘hump’ and VFB shifting. Modeling these C–V curves and their frequency dependence [45] allows Dit distributions and total fixed charge densities to be extracted. After the 1,000 °C RTA, the net effective charge is reduced by 5 × 1012 cm−2 (VFB shift), and the peak interface trap density (as shown in Fig. 9.6b) decreases from 3 × 1013 to 6 × 1011 cm−2 eV−1 without FGA. C–V data fits indicate device effective work function (\( \phi \) m,eff) values in the range of 3.6–4.0 eV. This makes these stacks of interest for n-channel (nMOSFET) devices; as will be discussed in Sect. 9.5.

After a high-temperature PMA of 1,000 °C for 10 s in N2, a subsequent 450 °C 30 min FGA reduces both the total charge states reflected in a VFB shift, and the interface states reflected in the lower C ‘hump’, as shown in Fig. 9.7a. However, typically FGA temperatures above 450 °C are required to significantly lower total interface state density (Nit) levels, as shown in Fig. 9.7b [45]. Because aggressive gate stack annealing typically results in some interface SiO2 growth, Dit characteristics with increasing anneal temperature should approach that of SiO2/Si [48]. So although high temperature processing can clearly result in low interface trap levels, obtaining low trap densities while maintaining sub-nm EOT remains a key process challenge, as excess O is hard to eliminate.

High temperature processing also significantly improves reliability under gate voltage stress (negative (or positive) bias temperature instability, NBTI (PBTI)) stresses. Figure 9.8a, b shows the room temperature flat-band voltage (VFB) shift of sub-nm EOT TaN/LaSiOx/n-Si MOS devices as a function of stack RTA temperature, comparing −2 V and +2 V gate bias [49]. It is clear from Fig. 9.8a that lower T processing results in increasing amounts of VFB shift, consistent with the increased defect densities as shown in Figs. 9.6, and 9.7. Also, the VFB shifts are clearly recoverable as shown in Fig. 9.8b, although some net +VFB shift occurs revealing faster e- trapping (PBTI) than detrapping (NBTI). This reveals that PBTI stress is a more urgent problem than NBTI especially for electron-channel devices, due to large amounts of pre-existing electron traps [50].

Table 9.2 summarizes La2O3 and LaSiOx dielectric properties, comparing MIM to MIS devices, and various processing temperatures. While TaN MIM capacitors are useful to demonstrate potential dielectric constants, MIS devices typically will contain more Si than expected (due to additional O and subsequent silicate reaction), and thus lower k values for LaSiOx. This reveals the difficult processing balance in which low temperature processing promotes aggressive EOT scaling (0.5–0.7 nm) while moderately high temperature processing is required to minimize Dit levels. Aggressively pursuing means to eliminate excess O in the gate electrode is critical for the gate first processes.

9.4.1.2 Gate Stack Materials Characterization

To better understand the obtained electrical properties, it is of importance to study the materials properties of these gate stacks. Critical for aggressive EOT scaling of typical gate-first processing of gate stacks are: (1) amorphous phase stability of the dielectric to source/drain activation anneal temperatures; (2) no cation diffusion into the Si channel; and (3) minimizing the low-k SiO2 growth at the dielectric-Si interface. These have been investigated for LaSiOx gate stacks using cross-sectional TEM, back side secondary ion mass spectrometry (SIMS), and medium-energy ion-scattering (MEIS).

As shown in Fig. 9.9, cross-sectional TEM clearly shows that the LaSiOx dielectric remains amorphous after a 1,000 °C 10 s RTA in N2 [51]. This is a key to keeping smoother interfaces and low gate leakage. There is no indication of phase separation with lanthanum silicate as there is with Hf or Zr silicates [18], another key advantage of lanthanide silicates in general. Using back-side SIMS analysis, it is clear that La does not diffuse into the Si [51], and thus the stack shows good thermal stability. Although the stack is chemically stable, an EOT increase is typical with annealing, as Fig. 9.6 shows. MEIS analysis of LaSiOx/Si without metal capping shows clearly that there is dielectric thickening after a 1,000 °C 10 s RTA, as Fig. 9.10 reveals [49]. As these were uncapped, presumably O from the anneal chamber diffuses to the Si interface, silica forms, which subsequently reacts to form silicate. Thus annealing ultimately lowers the La content, thus lowering the dielectric constant as well. Annealing at high temperature also creates a dielectric which is stable against hydroxide formation. Figure 9.11 shows the O1s XPS spectra of uncapped LaSiOx before and after 1,000 °C 10 s RTA, from stacks corresponding to the MEIS data of Fig. 9.10. Fits to the spectra clearly show that with ~1 day of air exposure, the 400 °C formed silicate reacts to form some hydroxide (20 % of O as hydroxide), while after the 1,000 °C RTA only about 3 % of O is bonded as hydroxide. Thus a dense silicate is very stable against hydroxide formation [10].

If excess O is properly eliminated from the gate electrode, there appear to be no fundamental reasons why these materials cannot be implemented into scaled MOSFETs, although the obtained VFB (effective work function <4 eV) indicates that nMOSFET devices will be more practical, while pMOSFET devices will require stack modifications.

9.4.2 Aluminates and Scandates

The addition of a second +3 valence cation to a simple binary lanthanide oxide has important implications. Typically this will: (1) result in higher-temperature stability for an amorphous film compared to the binary oxide; (2) render the lanthanide more stable against hydroxide formation; and (3) result in crystalline structures more suitable to epitaxial growth on Si (001). Lanthanide aluminates (e.g. LaAlO3) and scandates (e.g. LaScO3, GdScO3) have perovskite-like orthorhombic structures when crystallized. These materials have received attention especially as epitaxial oxide candidates (to be discussed in Sect. 9.6), since they have cubic lattices allowing some matching with Si, and the crystalline structures lead to large k values (of about 24–27 as reported by Heeg et al. [52], while LaScO3 may have a k as high as 33 even for amorphous films [53]) and large conduction band offsets (of ~2.0 eV [54]) with respect to Si. In comparison to silicates described previously, the dielectric constants of these ternaries without Si will be greater, while the amorphous phase stability limit is typically lower.

Considering LaAlO3, amorphous films have been observed to have a k of only 16 [31], lower than the crystalline value of 24. However, upon PMA at above 900 °C simulating a source/drain activation anneal, films crystallize and partially decompose, allowing both Al and La to diffuse into the Si substrate [55]. Amorphous mixtures of La2O3–Al2O3 have an increased tendency to separate, rather than crystallize into the perovskite phase, especially in the presence of SiO2, in which case Al2O3 separation occurs, and lanthanide silicate forms [56]. The amorphous phase stability can be increased to at least 1,000 °C by depositing a LaAlON film [57], in which case the phase stability rivals that of LaSiOx, and the k should be higher. Cation diffusion into Si appears to correspond with the crystallization event, such that no La or Al diffusion into Si is observed for amorphous LaAlON. This is reasonable, in that this amorphous-crystalline structural change to the equilibrium phase acts as an indicator of increased diffusivity. Thus amorphous LaAlON maintains promise as an alternative dielectric, while amorphous LaAlO3 would appear restricted to gate-last processing routes.

9.4.3 Hafnates and Zirconates

Key improvements in the properties of dielectrics such as HfO2 can be achieved by alloying with lanthanides, such as increasing the amorphous phase stability [58], and lowering of defect levels [59]. Due to the maturity of the use of HfO2 dielectric, Ln-modified Hf-based dielectrics have been implemented in scaled MOSFET devices, thus better characterized than other lanthanide binary or ternary compounds.

When alloying lanthanides with Hf or Zr oxides, the resulting compound retains a high dielectric constant, in contrast to the silicates. The +3 valence Ln cation addition to the +4 Hf or Zr results in a mixed cation coordination alloy, which helps to frustrate crystallization. If formed, the crystalline phase is a very stable pyrochlore-type phase, such as the La2Hf2O7 composition. In addition, the Ln present plays the important role of converting (at least some of) the SiO2 interface layer to a higher-k Ln-silicate, to further lower EOT beyond that possible with HfO2 alone [60].

Another key improvement obtained by alloying HfO2 with lanthanides (expected to apply to zirconia as well) is the attainment of nMOSFET band-edge effective work function [4, 61–63]. Effects of Ln addition on VT, a critical issue with regard to MOSFET device properties, will be discussed in Sect. 9.5.

It has been observed that HfSiON-based MOSFETs (EOT ~0.9 nm) with a lanthanide addition improves the PBTI device reliability [63–65]. Using a La2O3 capping layer results in a ~3 × reliability improvement under PBTI stress compared to a control HfSiOx dielectric without lanthanide, shown in Fig. 9.12a, and listed in Table 9.3. Additionally, there is little mobility degradation upon adding La, indicated in Fig. 9.12b and Table 9.3. The PBTI reliability enhancement may be linked with the ability of the Ln addition to enhance the amorphous phase stability, thus limiting defects associated with crystalline dielectrics [17]. Maximizing device mobility is another complex issue relating to the entire gate stack including the metal gate electrode, but it is clear that the Ln addition can result in very little mobility degradation.

9.4.4 Multi-Component Dielectrics Summary

In comparison to binary lanthanides or other binary oxides such as HfO2, dielectrics with at least one additional cation (ternaries) offer several potential advantages for use as a gate dielectric. These include: (1) a higher-temperature amorphous phase-stability; (2) a potential for limiting IL SiO2 formation; (3) an ability to control device VT; and (4) a means of reducing VT shift during PBTI stress. A comparison of capacitor data of various ternary dielectrics from various groups is shown in Fig. 9.13 (while LaHfSiON represents MOSFET data). These ternary dielectrics all result in much lower-leakage gate stacks in comparison with SiO2, while maintaining the additional benefits described above. As the search for higher k is expected to move towards epitaxial oxide growth, multi-component systems allow the ability to tune the lattice parameter for enhancing epitaxial lattice match.

The particular choice of which dielectric is the best as a gate dielectric has to consider the many aspects of device properties such as EOT, VT, mobility, ease of processing, etc.; and the choice may differ for n versus p MOSFET, or for gate-first versus gate-last processing.

9.5 Threshold Voltage Control

Although VT control will be covered in a separate chapter, key issues related to VT control using Ln elements in the dielectric layer is mentioned briefly here. (Sects. 2.3 and 2.8.1—covers the theoretical basis for flat-band and threshold voltages and the complications in the case of the high-k gate stacks. The threshold voltage anomaly and the role of the interface dipoles in it have been analyzed in Chap. 6. Work function considerations and threshold voltage tuning by interface dipoles and oxygen vacancies has been outlined in Chap. 5.) Initial attempts to control VT were based primarily on finding appropriate electrode alloy work functions. More recently it has been understood that any region of the gate stack may be influential in controlling device VT, especially the regions near the Si interface. It is worth noting, although not covered here, that Ln elements alloyed in the metal gate can influence the device work function [66], but here we focus on Ln (or similar) elements within the dielectric layer.

9.5.1 nMOSFET VT Control Strategies

Early work with capacitors showed that lanthanide dielectrics resulted in very low effective work function devices (originally perceived to be problematic, as it was expected to degrade channel mobility), while for Hf-based dielectrics mid-gap work functions were prevalent. This was taken advantage of in a simple way by Alshareef et al. [4]. by applying a thin lanthana cap layer to a Hf-based dielectric to obtain nMOSFET band-edge VT devices. It was shown that with a 0.5 or 1.0 nm La2O3 cap, a VT reduction of more than 0.4 eV was obtained, with very little mobility loss (achieving 92 % of the SiO2 universal mobility). Split C–V measurements of nMOSFETs are shown in Fig. 9.14a, revealing the VT lowering by a La2O3 capping of the HfSiO dielectric. Backside SIMS analysis (Fig. 9.14b) reveals that after a spike anneal processing, the final device has the La reaching the bottom of the HfO2 layer, although initially deposited as a cap layer [4].

MOSFET split CV (left) showing the VT lowering with La2O3 capping. After spike anneal processing, the La reaches the bottom of the HfO2 layer, shown by backside SIMS (right). From Alshareef et al. [4]

The VT lowering has been correlated to the presence of Ln cations at the SiO2 top interface (as is corroborated by depositing lanthana directly on SiO2 [49]), and is adequately described by an interface dipole model [67] which considers electronegativity and ionic radii of the various cation components in the dielectrics, and their influence at the SiO2/high-κ interface. It has been shown that VT lowering occurs with various Ln elements as well as other group II or III cations mixed with HfO2 [62, 67].

Other critical aspects of the VT control are expected to relate to the silicate-like bonding at the interface, which determines bond density and directionality at the interface, and thus contributes to determining the net dipole moment beyond the issues of ionic radius and electronegativity. Without considering effects of local interface chemistry, a simple addition of a series of interfaces would not be expected to result in the significant net dipole effect as is seen in practice. Kita and Toriumi [68] present a model describing how the O density difference in the dielectrics at the SiO2 interface may be the root origin of the interface dipole. Although there remains debate concerning specifics, there is wide consensus [62, 67, 69] that the VT control relates to effects predominantly at the bottom high-k interface with SiO2, and is not simply a top-electrode work function change.

9.5.2 pMOSFET VT Control Strategies

As any high-temperature treatment typically results in the Ln element diffusing to the SiO2 IL, typical gate first processing will produce nMOSFET VT values. To obtain pMOSFET VT with a Ln element present, the Ln would need to remain at the top interface, necessitating gate-last processing and additional dielectric layering schemes [70]. However, the use of elements such as Al [68] would be more suitable, and Ln elements are typically not pursued for pMOSFET applications.

9.6 Epitaxial Lanthanide High-κ Gate Dielectrics

As device scaling continues to push EOT to the values required for the 22 nm device node and beyond, dielectric constants in the range of 25 and higher will be required. This drives research efforts into epitaxial dielectrics compatible with the semiconductor channel material, as epitaxial dielectrics should have virtually no low-k interface layer, and crystalline oxides have higher k than their amorphous counterparts. This is another area where lanthanide-based dielectrics appear to again be advantageous, based on lattice structure and chemical compatibility. Issues related to epitaxial growth of lanthanide oxides on semiconductors is covered in detail in Chap. 11, in particular that of Gd2O3 on Si.

9.7 Lanthanide Dielectrics on High-Mobility Semiconductors

Scaling beyond the limits of Si devices has many researchers looking into the use of high-mobility semiconductors for the device channel, in device structures which allow higher drive current to be realized. Candidates of present interest include Ge, GaAs and related III–V materials such as InGaAs. Whether the high mobility channel is formed from an epitaxial layer on Si, or an alternative semiconductor bulk substrate, the dielectric must be chemically compatible with the channel. Lanthanides are expected to be suitable dielectrics on GaAs based on the work of Passlack [5], and should result in acceptably high band-offsets [71] to minimize the gate leakage.

In order to realize higher device currents, the key challenge for MOSFETs on alternative semiconductors has been to achieve a low defect-level interface with the gate dielectric. On GaAs, extensive research has been performed on the use of Gd2O3 dielectric by Passlack [5]. They have shown the ability to obtain a low leakage dielectric and reduce interface states to acceptable levels, through an optimized process to obtain GaGdOx (k ~ 20) on a ~1 nm Ga2O3 interface layer. Eliminating As oxides while precisely controlling Ga interface oxides appear to be key factors for obtaining good MOS behavior. Additionally, many groups are investigating the use of sulphur-passivation treatments [72, 73] or deposited interface layers [74] in attempts to lower Dit on III–V semiconductors.

As HfO2 directly on GaAs appears to result in unacceptably high interface state densities [74], there is an impetus to look at various interface treatments, and other dielectrics, such as LaSiOx [75, 76]. Shown in Fig. 9.15a–b is an XPS comparison of 3 nm LaSiOx films on p-type GaAs (001) subjected to three different surface treatments (native oxide, HCl dip, or HCl dip and S-passivation) [75]. It can be seen that, under the restriction of a 400 °C process temperature limit, interface As-oxides are reduced after dielectric deposition, and the presence of Ga-oxide depends on the GaAs surface treatment. The S-treated interface, composed of minimal Ga-O (and/or Ga-S) bonding with no As-O, is conducive to low interface state densities [5, 72, 77]. MOS capacitor C–V characteristics as show in Fig. 9.16 indicate that the S-treatment results in the thinnest dielectric, with small hysteresis and lowest VFB [75]. It has also been shown that LaSiOx on GaAs results in good values of band gap (6.5 eV) and conduction band offset of 2.7 eV [76], and thus lanthanide dielectrics appear to show promise for practical application to III–V semiconductors. These effects of surface treatments and processing on the interface oxides is similar to that observed during ALD deposition of HfO2 on GaAs, termed ‘self-cleaning’ [78].

MOS C–V characteristics of LaSiOx/GaAs corresponding to the XPS spectra in Fig. 15

However, as is the case for all dielectrics on III–V semiconductors, much more work needs to be done to eliminate or control defect levels near band edges, as well as deep levels, which result in channels with low carrier concentration, and low mobility. This can be done to a large extent by utilizing semiconductors such as InxGa1-xAs, but the interface with the dielectric must be optimized simultaneously, while maintaining a high dielectric constant stack. Passivation of Ge, GaAs, and InGaAs surfaces has been covered in detail in Chap. 12.

9.8 Processing, Scaling, and Integration Issues

While lanthanide-based oxides are thermodynamically very stable oxides, as mentioned the binary oxides have tendencies towards hydroxide and carbonate formation. Consideration of the oxide integrity must be taken into account when considering wet process methods. However, ternary lanthanides or silicates do not suffer from these limitations; and gate stacks typically have some interface mixing which renders the hydroxide formation issue moot if the dielectric is extremely thin.

Relatively successful small gate length MOSFET processing of lanthanide-containing dielectrics has been demonstrated by both SEMATECH [4] and IMEC [79]. Wet etching of Ln-based oxides in weak HCl solutions gives good selectivity w/r to HfO2 etching [79]. However, Ln-based oxide caps on HfO2 for nMOSFET VT tuning must be etched off in regions requiring pMOSFET VT. When etched, it is observed that some Ln element remains in HfO2 due to Ln intermixing [80]. Thus the ability to attain the pMOS WF will be affected. To get around this, some HfO2 etch and re-deposition may be required, thus complicating the processing. Although processing must be optimized, there appears to be no inherent limitation to the use of Ln-based dielectrics or electrode materials. Indications are that, to obtain the lowest possible EOT gate stacks, and low effective work function for nMOSFETs, Ln materials will indeed be required in the gate stack for future technology nodes.

9.9 Summary of Lanthanide Materials and Properties

Lanthanide materials will continue to gain interest as device features shrink, requiring higher-k dielectrics with thinner interface layers, and possibly alternative channel materials. To date lanthanides have proven key components in dielectrics providing for: (1) sub-nm EOT gate stacks due to high dielectric constant and SiO2 interface reduction, while maintaining good MOSFET mobility; (2) nMOSFET VT control and PBTI reduction of Hf-based dielectrics; and (3) obtaining low leakage, low DIT dielectrics on GaAs. Application areas which remain open for further study for lanthanide dielectrics include epitaxial oxide integration on Si or SiGe, and oxides on alternative high-mobility (III–V based) substrates for high speed applications, as well as use as a gate dielectric or passivation layer for high power FETs (for example, on SiC or GaN).

References

A.I. Kingon, J.-P. Maria, S.K. Streiffer, Alternative dielectrics to silicon dioxide for memory and logic devices. Nature 406, 1032 (2000)

D.G. Schlom, J.H. Haeni, A thermodynamic approach to selecting alternative gate dielectrics. MRS Bull. 27(3), 198 (2002)

J. Robertson, Electronic structure and band offsets of high-dielectric-constant gate oxides. MRS Bull. 27(3), 217 (2002)

H.N. Alshareef, H.R. Harris, H.C. Wen, C.S. Park, C. Huffman, K. Choi, H.F. Luan, P. Majhi, B.H. Lee, R. Jammy, D.J. Lichtenwalner, J.S. Jur, A.I. Kingon, Thermally stable N-metal gate MOSFETs using La-incorporated HfSiO dielectric, IEEE Symp. on VLSI Technology (2006), pp. 7–8

M. Passlack, Methodology for development of High-κ stacked gate dielectrics on III-V semiconductors, materials fundamentals of gate dielectrics, ed. by A.A. Demkov, A. Navrotsky (Springer, 2005), pp. 403–467

G.-Y. Adachi, N. Imanaka, The binary rare earth oxides. Chem. Rev. 98, 1479–1514 (1998)

S. Bernal, G. Blanco, J.J. Calvino, J.A. Perez Omil, J.M. Pintado, Some major aspects of the chemical behavior of rare earth oxides: An overview. J. Alloy. Compd. 408–412, 496–502 (2006)

G. Scarel, A. Svane, M. Fanciulli, Scientific and technological issues related to rare earth oxides: An Introduction, eds. by M. Fanciulli, G. Scarel. Rare earth oxide thin films, topics applied Physics (Heidelberg, 2007), 106:1–14

T. Gougousi, G.N. Parsons, Postdeposition reactivity of sputter-deposited high-dielectric-constant films with ambient H2O and carbon-containing species. J. Appl. Phys. 95(3), 1391 (2004)

D.J. Lichtenwalner, J.S. Jur, S. Novak, V. Misra, A.I. Kingon, Reliability and Stability Issues for Lanthanum Silicate as a High-K Dielectric. ECS Trans. 3(3), 245 (2006)

Y. Zhao, M. Toyama, K. Kita, K. Kyuno, A. Toriumi, Moisture-absorption-induced permittivity deterioration and surface roughness enhancement of lanthanum oxide films on silicon. Appl. Phys. Lett. 88, 072904 (2006)

T. Schroeder, T.-L. Lee, L. Libralesso, I. Joumard, J. Zegenhagen, P. Zaumseil, C. Wenger, G. Lupina, G. Lippert, J. Dabrowski, H.-J. Müssig, Structure and strain relaxation mechanisms of ultrathin epitaxial Pr2O3 films on Si (111). J. Appl. Phys. 97, 074906 (2005)

L. Marsella, V. Fiorentini, Structure and stability of rare-earth and transition-metal oxides. Phys. Rev. B 69, 172103 (2004)

J. Paivasaari, M. Putkonen, L. Niinisto, A comparative study on lanthanide oxide thin films grown by atomic layer deposition. Thin Solid Films 472, 275–281 (2005)

I.A. Bondar, Rare-earth silicates. Ceram. Int. 8(3), 83 (1982)

J–.J. Liang, A. Navrotsky, T. Ludwig, H.J. Seifert, F. Aldinger, Enthalpy of formation of rare-earth silicates Y2SiO5 and Yb2SiO5 and N-containing silicate Y10(SiO4) 6N2. J. Mater. Res. 14(4), 1181–1185 (1999)

P.D. Kirsch, M.A. Quevedo-Lopez, S.A. Krishnan, B.H. Lee, G. Pant, M.J. Kim, R.M. Wallace, B.E. Gnade, Mobility and charge trapping comparison for crystalline and amorphous HfON and HfSiON gate dielectrics. Appl. Phys. Lett. 89, 242909 (2006)

J.-P. Maria, D. Wickaksana, J. Parrette, A.I. Kingon, Crystallization in SiO2–metal oxide alloys. J. Mater. Res. 17, 1571 (2002)

D.J. Lichtenwalner, J.S. Jur, A.I. Kingon, M.P. Agustin, Y. Yang, S. Stemmer, L.V. Goncharova, T. Gustafsson, E. Garfunkel, Lanthanum silicate gate dielectric stacks with sub-nanometer EOT utilizing an interfacial silica consumption reaction. J. Appl. Phys. 98(2), 4314 (2005)

D Xue, K Betzler, H Hesse, Dielectric constants of binary rare-earth compounds, J. Phys.: Condens. Matter 12, 3113–3118 (2000)

H.J. Osten, M. Czernohorsky, E. Bugiel, D. Kuehne, A. Fissel, Interface engineering during epitaxial growth of high-K lanthanide oxides on silicon. Mater. Res. Soc. Symp. Proc. 917, E10–04 (2006)

L. Tye, N.A. El-Masry, T. Chikyow, P. McLarty, S.M. Bedair, Electrical characteristics of epitaxial CeO2 on Si (111). Appl. Phys. Lett. 65, 3081 (1994)

A. Fissel, H.J. Osten, E. Bugiel, Towards understanding epitaxial growth of alternative high-K dielectrics on Si (001): Application to praseodymium oxide. J. Vac. Sci. Technol., B 21, 1765 (2003)

G. Scarel, A. Debernardi, D. Tsoutsou, S. Spiga, S.C. Capelli, L. Lamagna, S.N. Volkos, M. Alia, M. Fanciulli, Vibrational and electrical properties of hexagonal La2O3 films. Appl. Phys. Lett. 91, 102901 (2007)

A.M. Herrero, B.P. Gila, C.R. Abernathy, S.J. Pearton, V. Craciun, K. Siebein, F. Ren, Epitaxial growth of Sc2O3 films on GaN. Appl. Phys. Lett. 89, 092117 (2006)

S.Y. Chiam, W.K. Chim, C. Pi, A.C.H. Huan, S.J. Wang, J.S. Pan, S. Turner, J. Zhang, Band alignment of yttrium oxide on various relaxed and strained semiconductor substrates. Appl. Phys. Lett. 103, 083702 (2008)

M. Wagner, T. Heeg, J. Schubert, C. Zhao, O. Richard, M. Caymax, V.V. Afanas’ev, S. Mantl, Preparation and characterization of rare earth scandates as alternative gate oxide materials. Solid-State Electron. 50, 58–62 (2006)

Y.F. Loo, S. Taylor, R.T. Murray, A.C. Jones, P.R. Chalker, Structural and electrical characterization of amorphous lanthanum hafnium oxide thin films. J. Appl. Phys. 99, 103704 (2006)

R. Schwab, R. Sporl, P. Severloh, R. Heidinger, J. Halbritter, Temperature and orientation dependent dielectric measurements of LaAlO3-substrates, Appl. Supercond. 1/2. 61 (1997)

S.G. Lim, S. Kriventsov, T.N. Jackson, J.H. Haeni, D.G. Schlom, A.M. Balbashov, R. Uecker, P. Reiche, J.L. Freeouf, G. Lucovsky, Dielectric functions and optical bandgaps of high-K dielectrics for metal-oxide-semiconductor field-effect transistors by far ultraviolet spectroscopic ellipsometry. J. Appl. Phys. 91, 4500 (2002)

L.F. Edge, D.G. Schlom, P. Sivasubramani, R.M. Wallace, B. Holländer, J. Schubert, Electrical characterization of amorphous lanthanum aluminate thin films grown by molecular-beam deposition on silicon. Appl. Phys. Lett. 88, 112907 (2006)

J.M.J. Lopes, M. Roeckerath, T. Heeg, E. Rije, J. Schubert, S. Mantl, V.V. Afanas’ev, S. Shamuilia, A. Stesmans, Y. Jia, D.G. Schlom, Amorphous lanthanum lutetium oxide thin films as an alternative high-K gate dielectric. Appl. Phys. Lett. 89, 222902 (2006)

K.L. Ovanesyan, A.G. Petrosyan, G.O. Shirinyan, C. Pedrini, L. Zhang, Single crystal growth and characterization of LaLuO3. Opt. Mater. 10, 291–295 (1998)

M. Leskelä, K. Kukli, M. Ritala, Rare-earth oxide thin films for gate dielectrics in microelectronics. J. Alloys Compd. 418, 27–34 (2006)

M.F. Vignolo, S. Duhalde, M. Bormioli, G. Quintana, M. Cervera, J. Tocho, Structural and electrical properties of lanthanum oxide thin films deposited by laser ablation. Appl. Surface Sci. 197–198, 522–526 (2002)

Y.H. Wu, M.Y. Yang, A. Chin, Senior Member, IEEE, W.J. Chen, C.M. Kwei, Electrical characteristics of high quality La2O3 gate dielectric with equivalent oxide thickness of 5 Å, IEEE Electron Dev. Lett., 21(7), 341 (2000)

M. Copel, E. Cartier, F.M. Ross, Formation of a stratified lanthanum silicate dielectric by reaction with Si (001). Appl. Phys. Lett. 78(11), 1607 (2001)

E. Graper, (2009), Thin Film Evaporation Guide. http://www.tfi-telemark.com/telemrk/cat_evapguide.htm. Accessed Jan 4 2009

H. Watanabe, N. Ikarashi, F. Ito, La–silicate gate dielectrics fabricated by solid phase reaction between La metal and SiO2 underlayers. Appl. Phys. Lett. 83(17), 3546–3549 (2003)

H.C. Aspinall, J.F. Bickley, J.M. Gaskell, A.C. Jones, G. Labat, P.R. Chalker, P.A. Williams, Precursors for MOCVD and ALD of rare earth oxides-complexes of the early lanthanides with a donor-functionalized alkoxide ligand. Inorg. Chem. 46(15), 5852–5860 (2007)

S. Kamiyama, T. Miura, E. Kurosawa, M. Kitajima, M. Ootuka, T. Aoyama, Y. Nara, Band edge gate first HfSiON/metal gate n-MOSFETs using ALD-La2O3 cap layers scalable to EOT = 0.68 nm for hp 32 nm bulk devices with high performance and reliability, IEEE Inter. Electron Devices Meeting (IEDM). 539–542 (2007)

S. Schamm, P.E. Coulon, S. Miao, S.N. Volkos, L.H. Lu, L. Lamagna, C. Wiemer, D. Tsoutsou, G. Scarel, M. Fanciulli, Chemical/Structural nanocharacterization and electrical properties of ALD-grown La2O3/Si interfaces for advanced gate stacks. J. Electrochem. Soc. 156, H1 (2009)

J. Niinisto, N. Petrova, M. Putkonen, L. Niinisto, K. Arstila, T. Sajavaar, Gadolinium oxide thin films by atomic layer deposition. J. Cryst. Growth 285, 191–200 (2005)

A. Kuriyama, S.-I. Ohmi, K. Tsutsui, H. Iwai, Effect of post-metallization annealing on electrical characteristics of La2O3 gate thin films. Jpn. J. Appl. Phys. 44(2), 1045–1051 (2005)

N. Inoue, D.J. Lichtenwalner, J.S. Jur, A.I. Kingon, Analysis of interface states in LaSixOy metal–insulator–semiconductor structures, Jpn. J. Appl. Phys. 46(10A), 6480–6488 (2007)

G. Lucovsky, J.-P. Maria, J.C. Phillips, Interfacial strain-induced self-organization in semiconductor dielectric gate stacks. II. Strain-relief at internal dielectric interfaces between SiO2 and alternative gate dielectrics. J. Vac. Sci. Technol. B22, 2097 (2004)

J.S. Jur, D.J. Lichtenwalner, A.I. Kingon, Processing impact on electrical properties of lanthanum silicate thin films. Mater. Res. Soc. Sym. Proc. 917, E10–03 (2006)

P.K. Hurley, K. Cherkaoui, S. McDonnell, G. Hughes, A.W. Groenland, Characterisation and passivation of interface defects in (100)-Si/SiO2/HfO2/TiN gate stacks. Microelectronics Reliab. 47, 1195–1201 (2007)

D.J. Lichtenwalner, J.S. Jur, N. Inoue, A.I. Kingon, Overview of materials processing and properties of lanthanum-based high-κ dielectrics. ECS Trans. 11(4), 319 (2007)

T.P. Ma, X.W. Wang, L. Song, H. Bu, Charge trapping—a major reliability challenge for High-κ gate dielectrics. ECS Trans. 1(5), 733 (2006)

J.S. Jur, D.J. Lichtenwalner, A.I. Kingon, High temperature stability of lanthanum silicate dielectric on Si (001). Appl. Phys. Lett. 90, 102908 (2007)

T. Heeg, J. Schubert, C. Buchal, E. Cicerrella, J.L. Freeouf, W. Tian, Y. Jia, D.G. Schlom, Growth and properties of epitaxial rare-earth scandate thin films. Appl. Phys. A 83, 103–106 (2006)

J.M.J. Lopes, U. Littmark, M. Roeckerath, S.T. Lenk, J. Schubert, S. Mantl, A. Besmehn, Effects of annealing on the electrical and interfacial properties of amorphous lanthanum scandate high-κ films prepared by molecular beam deposition. J. Appl. Phys. 101, 104109 (2007)

V.V. Afanas’ev, A. Stesmans, C. Zhao, M.Caymax, T. Heeg, J. Schubert, et al., Band alignment between (100) Si and complex rare earth/transition metal oxides, Appl. Phys. Lett. 85(24) (2004)

P. Sivasubramani, J. Kim, B.E. Gnade, R.M. Wallace, L.F. Edge, D.G. Schlom, H.S. Craft, J.-P. Maria, Outdiffusion of La and Al from amorphous LaAlO3 in direct contact with Si (100). Appl. Phys. Lett. 86, 201901 (2005)

B. Lee, D.J. Lichtenwalner, M. Agustin, R. Arghavani, X. Tang, S. Gandikota, V. Ku, V. Misra, Investigation of VT shift mechanisms of High-K dielectrics caused by lanthanum capping for NMOS and tantalum capping for PMOS devices. ECS Trans. 13(1), 123 (2008)

P. Sivasubramani, J. Kim, M.J. Kim, B.E. Gnade, R.M. Wallace, Effect of nitrogen incorporation on the thermal stability of sputter deposited lanthanum aluminate dielectrics on Si (100). Appl. Phys. Lett. 89, 152903 (2006)

T. Wang, J.G. Ekerdt, Atomic layer deposition of lanthanum stabilized amorphous hafnium oxide thin films. Chem. Mater. 21, 3096–3101 (2009)

Z.M. Rittersma, J.C. Hooker, G. Vellianitis, J.-P. Locquet, C. Marchiori, M. Sousa, J. Fompeyrine, L. Pantisano, W. Deweerd, T. Schram, M. Rosmeulen, S. De Gendt, A. Dimoulas, Characterization of field-effect transistors with La2Hf2O7 and HfO2 gate dielectric layers deposited by molecular-beam epitaxy. J. Appl. Phys. 99, 024508 (2006)

K. Choi, H. Jagannathan, C. Choi, L. Edge, T. Ando, M. Frank, P. Jamison, M. Wang, E. Cartier, S. Zafar, J. Bruley, A. Kerber, B. Linder, A. Callegari, Q. Yang, S. Brown, J. Stathis, J. Iacoponi, V. Paruchuri, V. Narayanan, Extremely scaled gate-first High-k/metal gate Stack with EOT of 0.55 nm using novel interfacial layer scavenging techniques for 22 nm technology node and beyond, IEEE Sym. on VLSI Technology (2009), 138

X.P. Wang, M.-F. Li, C. Ren, X.F. Yu, C. Shen, H.H. Ma, A. Chin, C.X. Zhu, J. Ning, M.B. Yu, D.-L. Kwong, Tuning effective metal gate work function by a novel gate dielectric HfLaO for nMOSFETs. IEEE Electron. Device Lett. 27(1), 31 (2006)

V. Narayanan, V.K. Paruchuri, N.A. Bojarczuk, B.P. Linder, B. Doris, Y.H. Kim, S. Zafar, J. Stathis, S. Brown, J.Arnold, M. Copel, M. Steen, E. Cartier, A. Callegari, P. Jamison, J.-P. Locquet, D.L. Lacey, Y. Wang, P.E. Batson, P. Ronsheim, R. Jammy, M.P. Chudzik, M. Ieong, S. Guha, G. Shahidi, T.C. Chen, Band-Edge High-Performance High-κ/Metal Gate n-MOSFETs using cap layers containing group IIA and IIIB elements with gate-first processing for 45 nm and beyond, IEEE Symp on VLSI Technology (2006), pp. 178–179

H.R. Harris, H. Alshareef, H.C. Wen, S. Krishnan, K. Choi, H. Luan, D. Heh, C.S. Park, H.B. Park, M. Hussain, B.S. Ju, P.D. Kirsch, S.C. Song, P. Majhi, B.H. Lee, R. Jammy, Simplified manufacturable band edge metal gate solution for NMOS without a capping Layer, IEEE Inter. Electron Devices Meeting (IEDM) (2006), pp. 1–4

P.D. Kirsch, M.A. Quevedo-Lopez, S.A. Krishnan, C. Krug, H. AlShareef, C.S. Park, H.R. Harris, N. Moumen, A. Neugroschel, G. Bersuker, B.H. Lee, J.G. Wang, G. Pant, B.E. Gnade, M.J. Kim, R.M. Wallace, J.S. Jur, D.J. Lichtenwalner, A.I. Kingon, R. Jammy, Band Edge n-MOSFETs with High-k/metal gate stacks scaled to EOT = 0.9 nm with excellent carrier mobility and high temperature stability, IEEE Inter. Elec. Dev. Mtg. (IEDM) (2006), pp. 1–4

C.Y. Kang, C.D. Young, J. Huang, P.D. Kirsch, D. Heh, P. Sivasubramani, H.K. Park, G. Bersuker, B.H. Lee, H.S. Choi, K.T. Lee, Y.-H. Jeong, D.J. Lichtenwalner, A.I. Kingon, H.-H. Tseng, R. Jammy, The Impact of La-doping on the reliability of low VT High-k/Metal gate nMOSFETs under various gate stress conditions, IEEE Inter. Elec. Dev. Mtg. (IEDM) (2008), pp. 1–4

C. Ren, D.S.H. Chan, M.-F. Li, W.-Y. Loh, S. Balakumar, C.H. Tung, N. Balasubramanian, D.-L. Kwong, Work function tuning and material characteristics of lanthanide-incorporated metal nitride gate electrodes for NMOS device applications. IEEE Trans. Electron. Dev. 53, 1877 (2006)

P.D. Kirsch, P. Sivasubramani, J. Huang, C.D. Young, M.A. Quevedo-Lopez, H.C. Wen, H. Alshareef, K. Choi, C.S. Park, K. Freeman, M.M. Hussain, G. Bersuker, H.R. Harris, P. Majhi, R. Choi, P. Lysaght, B.H. Lee, H–.H. Tseng, R. Jammy, T.S. Böscke, D.J. Lichtenwalner, J.S. Jur, A.I. Kingon, Dipole model explaining high-k/metal gate field effect transistor threshold voltage tuning. Appl. Phys. Lett. 92, 092901 (2008)

K. Kita, A. Toriumi, Origin of electric dipoles formed at high-k/SiO2 interface. Appl. Phys. Lett. 94, 132902 (2009)

Y. Yamamoto, K. Kita, K. Kyuno, A. Toriumi, Study of La-induced flat band voltage shift in metal/HfLaOx/SiO2/Si capacitors. Jpn. J. Appl. Phys. 46, 7251 (2007)

B.M. Lee, D.J. Lichtenwalner, V. Misra, Unpublished research results

J. Robertson, B. Falabretti, Band offsets of high κ gate oxides on high mobility semiconductors. Mater. Sci. Eng., B 135, 267–271 (2006)

N.G. Wright, C.M. Johnson, A.G. O’Neill, Sulphur based surface passivation for high voltage GaAs Schottky diodes. Solid State Electron. 42, 437 (1998)

M.V. Lebedev, T. Mayer, W. Jaegermann, Sulfur adsorption at GaAs (1 0 0) from solution: role of the solvent in surface chemistry. Surf. Sci. 547, 171–183 (2003)

S. Oktyabrsky, V. Tokranov, M. Yakimov, R. Moore, S. Koveshnikov, W. Tsai, F. Zhu, J.C. Lee, High-k gate stack on GaAs and InGaAs using in situ passivation with amorphous silicon. Mater. Sci. Eng., B 135, 272–276 (2006)

D.J. Lichtenwalner, R. Suri, V. Misra, Effect of GaAs surface treatments on lanthanum silicate high-K dielectric gate stack properties. Mat. Res. Soc. Symp. Proc. 1073, H06–04 (2008)

J.-K. Yang, W.S. Kim, H–.H. Park, Chemical bonding states and energy band gap of SiO2-incorporated La2O3 films on n-GaAs (001). Thin Solid Films 494, 311–314 (2006)

R. Suri, D.J. Lichtenwalner, V. Misra, Impact of elemental arsenic on electrical characteristics of metal-oxide-semiconductor capacitors on GaAs using atomic-layer deposited HfO2 gate dielectric. Appl. Phys. Lett. 92, 243506 (2008)

R.M. Wallace, P.C. McIntyre, J. Kim, Y. Nishi, Atomic layer deposition of dielectrics on Ge and III–V materials for ultrahigh performance transistors. MRS Bull. 34, 493 (2009)

R. Vos, S. Arnauts, I. Bovie, B. Onsia, S. Garaud, K. Xu, Y. HongYu, S. Kubicek, E. Rohr, T. Schram, A. Veloso, T. Conard, L.H.A. Leunissen, P.W. Mertens, Challenges with respect to high-κ/metal gate stack etching and cleaning. ECS Trans. 11(4), 275 (2007)

T. Schram, S. Kubicek, E. Rohr, S. Brus, C. Vrancken, S.-Z. Chang1, V.S. Chang, R. Mitsuhashi, Y. Okuno, A. Akheyar, H.-J. Cho, J.C. Hooker, V. Paraschiv, R. Vos, F. Sebai, M. Ercken, P. Kelkar, A. Delabie, C. Adelmann, T. Witters, L-A. Ragnarsson, C. Kerner, T. Chiarella, M. Aoulaiche, Moon-Ju Cho, T. Kauerauf, K.De Meyer, A. Lauwers, T. Hoffmann, P.P. Absil, S. Biesemans, Novel Process to pattern selectively dual dielectric capping layers using soft-mask only, IEEE Symp on VLSI Technology (2008), pp. 44–45

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this chapter

Cite this chapter

Lichtenwalner, D.J. (2013). Lanthanide-Based High-k Gate Dielectric Materials. In: Kar, S. (eds) High Permittivity Gate Dielectric Materials. Springer Series in Advanced Microelectronics, vol 43. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-36535-5_9

Download citation

DOI: https://doi.org/10.1007/978-3-642-36535-5_9

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-36534-8

Online ISBN: 978-3-642-36535-5

eBook Packages: EngineeringEngineering (R0)