Abstract

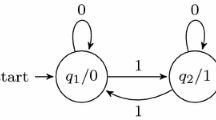

We propose a Universal Spiketrain Processor (USP) – a computing device for high-speed execution of Pulsed Para-Neural Networks (PPNN). PPNN is a graph consisting of processing nodes and directed edges, called axons. We provide a description of USP architecture, a USP-specific language of PPNN coding, and methods of conversion of the already existing PPNN code into a USP code. We also compare the USP’s performance with the already existing cellular-automata-based tools for PPNN simulation.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Buller: CAM-Brain Machines and Pulsed Para-Neural Networks (PPNN): Toward a hardware for future robotic on-board brains. In: Proceedings, 8th International Symposium. On Artificial Life and Robotics (AROB 8th 2003), Beppu, Japan, January 24-26, pp. 490–493 (2003)

Buller, H.E., Joachimczak, M.: Pulsed para-neural network (PPNN) synthesis in a 3-D cellular automata space. In: Proceedings, 9th International Conference on Neural Information Processing (ICONIP 2002), Singapore, November 18-22, vol. 1, pp. 581–584 (2002)

Buller, H., Hemmi, M., Joachimczak, J., Liu, K., Shimohara, K., Stefanski, A.: ATR Artificial Brain Project: Key Assumptions and Current State. In: Proceedings, 9th International Symposium on Artificial Life and Robotics (AROB 9th 2004), Beppu, Japan, January 28-30 (2004)

Buller, Tuli, T.S.: Four-legged robot.s behavior controlled by Pulsed para-neural net orks (PPNN). In: Proceedings, 9th International Conference on Neural Information Processing (ICONIP 2002), Singapore, November 18-22, vol. 1, pp. 239–242 (2002)

Joachimczak, M., Buller, A.: Universal Spiketrain Processor. ATR HIS, Kyoto (2003); Unpublished reseach memo

Gers, F., de Garis, H., Korkin, M.: CoDi-1Bit: A Simplified Cellular Automata based Neuron Model. In: Evolution Artificiele 1997, Nimes, France, October 22, pp. 211–229.

Korkin, M., Fehr, G., Jeffrey, G.: Evolving hardware on a large scale. In: Proceedings, The Second NASA / DoD Workshop on Evolvable Hardware, Pasadena, July 2000, pp. 173–181 (2000)

Jelinski, D., Joachimczak, M.: Heuristic-based Computer-Aided Synthesis of Spatial β-type Pulsed Para-Neural networks (3D-β PPNNs), Proceedings, 8th International Symposium. In: On Artificial Life and Robotics (AROB 8th 2003), Beppu, Japan, January 24-26, pp. 499–501 (2003)

Buller, A., Joachimczak, M., Liu, J., Stefanski, A.: Neuromazes: 3-Dimensional Spiketrain Processors. WSEAS Transactions on Computers 3(1), 157–161 (2004)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2004 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Joachimczak, M., Grzyb, B., Jelinski, D. (2004). Universal Spike-Train Processor for a High-Speed Simulation of Pulsed Para-neural Networks. In: Pal, N.R., Kasabov, N., Mudi, R.K., Pal, S., Parui, S.K. (eds) Neural Information Processing. ICONIP 2004. Lecture Notes in Computer Science, vol 3316. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-30499-9_63

Download citation

DOI: https://doi.org/10.1007/978-3-540-30499-9_63

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-23931-4

Online ISBN: 978-3-540-30499-9

eBook Packages: Springer Book Archive