Abstract

This chapter addresses the design of cost-aware ultra-low-power (ULP) radios for both 2.4-GHz and sub-GHz ISM bands. Starting from the system aspects that provide the essential insights, effective circuit techniques are presented to improve the radio performances and power efficiency, while minimizing the die area and number of external components.

Access provided by CONRICYT-eBooks. Download chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

This chapter addresses the design of cost-aware ultra-low-power (ULP) radios for both 2.4-GHz and sub-GHz ISM bands. Starting from the system aspects that provide the essential insights, effective circuit techniques are presented to improve the radio performances and power efficiency, while minimizing the die area and number of external components.

14.1 ULP Wireless Nodes in the IoT Landscape

Smart cities, environmental monitoring, energy management and healthcare systems, just to name a few, are all inside the gigantic landscape of Internet of Things (IoT) (Stankovic 2014) or Internet of Everything (IoE). The estimated IoT market by 2020 will be close to hundreds of billion dollars (annually ~16 billions). To accelerate the proliferation of IoT products in different application sectors, it is opportune to develop ultra-low-cost software-defined ULP radios that are flexible to support different data rates (e.g., from kb/s to a few Mb/s), different standards [e.g., ZigBee and Bluetooth Low Energy (BLE)] and a wide range of frequency (e.g., sub-GHz and 2.4-GHz ISM bands), while occupying a small die area and entailing a minimum number of external components. These next-generation ULP radios will be decisive for a wide variety of products that have strong competition among cost, performance and time-to-market. Nevertheless, the tradeoff analysis between cost, size and power for an ULP wireless link can involve many parameters that must be co-designed, implying that deeper understanding of the system aspects and effective circuit techniques are both essential to reach an optimum solution.

14.2 System Aspects of Short-Range ULP Radios

Focusing on short-range connectivity with a RF link budget of ~80 to 90 dB, the physical (PHY) layer specifications of Zigbee and BLE are not particularly tough for modern RF skills. Yet, traditional textbook RF and analog techniques can unlikely help to bring down the radio’s power by orders of magnitude, while allowing it to be universal enough to serve multiple bands without resorting from costly external components. The following sub-sections briefly discuss the PHY layer of Zigbee and BLE standards. The pros and cons of opting different frequency bands and supply voltages (VDD) are also mentioned; all are correlated to the overall cost, size and power efficiency of the radios.

14.2.1 ZigBee and Bluetooth Low Energy (BLE) Standards

Both ZigBee and BLE standards are suitable for short-range ULP communication as they draw low peak and average power. Their key features are briefed next.

ZigBee was developed as a wireless personal-area network (WPAN) standard with the IEEE 802.15.4 to define the PHY and Media Access Control (MAC) layers. It can operate at a very low duty cycle (<1%) and is allowed in three different frequency bands. The first band (868 MHz) is for Europe only offering only a single channel. It supports a low bit rate of 20 kbps using binary phase-shift keying (BPSK) modulation. The second band (915 MHz) permits 10 channels and is widely adopted in North America, Australia, New Zealand, and some countries in South America. Each channel supports 40 kbps using BPSK modulation. The third band is 2.4 GHz available worldwide, and has a total of 16 channels with 250 kbps each. Unlike the sub-GHz bands, this third band exploits offset quadrature phase-shift keying (OQPSK) with half sine-wave shaping for its modulation. Beyond these three bands, the IEEE 802.15.4c/d study groups also considered to open 314 to 316 MHz, 430 to 434 MHz, and 779 to 787 MHz bands for use in China, and 950 to 956 MHz for use in Japan. Obviously, an international market will be opened if the ULP radio can be reconfigured to support multiple bands from sub-GHz to 2.4 GHz. The key PHY specifications of ZigBee and BLE standards are summarized in Table 14.1.

BLE is a prospective short-range wireless standard ratified in 2009. It supports 40 channels in the 2.4-GHz band, each of which is 2-MHz wide. It is based on Gaussian frequency-shift keying (GFSK) modulation with an index of 0.5. The state-of-the-art 2.4-GHz receiver (Liu et al. 2014) achieves an energy efficiency of ~1.2 nJ/b at 2 Mb/s. Unsurprisingly, >40% of the receiver power is dissipated by the forefront low-noise amplifier (LNA) and mixer to maximize the sensitivity (−92 dBm). Such a high sensitivity seems overkill, but it is indeed effective to reduce the power consumption of the transmitter which normally has a lower energy efficiency to fulfill an RF link budget of ~90 dB. Thus, it is highly desired to develop circuit techniques for better LNA, mixer and voltage-controlled oscillator (VCO) for a better overall energy efficiency. In fact, for the 2.4-GHz band, Zigbee and BLE share a similar PHY, and modern solutions can easily support both. For the sub-GHz bands, multi-band operation poses additional challenges. To achieve this without leveraging the cost, a fully-integrated RF-tunable ULP radio will be of great relevance.

14.2.2 Cost, Size and Power

Ultra-scaled CMOS technologies are still the best platform for full integration of ULP radios that have RF (transceiver), analog (sensor and power management) and digital (microcontroller and memory). Established technology nodes (e.g., 90 or 65 nm) are regaining lots of interest for low-cost fast-to-market IoT products, as they can leverage more reasonably between the manufacturing cost, development time and power consumption. Apparently, the system cost and size can be optimized by reducing the chip area, number of external components and battery volume that depends on the targeted lifetime of the system. Although using on-chip passives (inductors and transformers) can help to reduce the VDD and system power, we will describe later that recent cost-aware ULP RF and analog circuits can balance better the power, chip area and cost. For instance, a fully-integrated input matching network not only can reduce the cost and system form factor of an ULP receiver, but also enhance its power efficiency. Also, the matching network can offer passive pre-gain to enhance the sensitivity of the receiver. Other low-power techniques such as current-reuse and function-reuse are will be introduced later in this chapter.

14.2.3 Frequency Bands: 2.4 GHz vs. Sub-GHz

Most existing ULP radios were designed for the 2.4-GHz band as it is available worldwide and has a smaller antenna size suitable for integration. Yet, the sub-GHz ISM bands offer other advantages such as longer propagation distance and less interference that are worth to be considered when the power budget is the priority.

Communication range—In highly congested environments, the 2.4-GHz signal can weaken rapidly, which adversely affects the signal quality. To quantify the influence of frequency on path loss with respect to the wavelength λ, we can use the simplified Friis transmission equation,

Hence, it can be calculated that the path loss at 2.4 GHz is 8.5 dB higher than that at 900 MHz. This translates into a 2.67× longer range for a 900-MHz radio. Since the range almost doubles with every 6 dB increment of power, a 2.4-GHz radio will entail an increment of power budget (by 8.5 dB), in order to match the range of a 900-MHz radio. Besides, biological tissues absorb RF energy as a function of frequency. Lower frequencies can penetrate the body easily without being absorbed, meaning a better RF link for sub-GHz when compared to 2.4 GHz for body-area networks.

Interference—The 2.4-GHz band has a high chance to come across interferences due to the co-existence of other wireless standards, degrading the link reliability. For example, the IEEE 802.11 (WiFi) can transmit an output power 10x to 100x higher than the ZigBee. Signals from Bluetooth-enabled computer, cell phone peripherals and microwave ovens can also be considered as “jammers”, which have a much lower output power. Sub-GHz ISM bands are mostly used for proprietary low-duty-cycle links and are not as likely to interfere with each other. A quieter spectrum means easier transmissions and fewer retries, which is more efficient to save the battery power. In fact, due to the limited power budget, it is hard for an ULP radio to tolerate large out-of-channel blockers.

Antenna size—One disadvantage of sub-GHz operation is the larger antenna size since most antenna types are designed to be resonant at their intended operation frequency. Since the antenna size is inversely proportional to the frequency, a small wireless node would prefer the 2.4-GHz band. Communication distance, low potential interference and low power consumption are the obvious advantages of the sub-GHz bands.

14.2.4 Supply Voltage (VDD)

To minimize the system size, short-range ULP radios should run preferably from a tiny battery, thus sub-2 V supply voltages are highly desired. Radios that work down to 1.2 V allow extra flexibility in sensors’ design and reduce the power management constraints (Rajan 2012). Besides, low peak current and sub-1 V VDD also benefit wireless sensors that run from harvested energy sources which will enhance flexibility, lower the maintenance cost, and open up more applications. For example, on-chip solar cells only can provide an output voltage between 200 and 900 mV, while thermoelectric generators exhibit an even lower VDD (50–300 mV) (Bandyopadhyay et al. 2011). Although boost converters can be employed to boost up the output voltage, their efficiency is still quite limited (~75%). Besides, a low peak current consumption will ease the design of the power management. Furthermore, radio operating at higher VDD is only required when a higher output power is entailed. This is not the case for short-range communications, as the output power rarely exceeds 0 dBm. Thus, a low VDD is in general the simplest way to reduce the power consumption at the system level.

In a low VDD design, however, due to the limited dynamic range, for the given parameters such as third-order intercept point (IIP3), noise-figure (NF), gain etc., the current should be larger than that with a high VDD. For example, for the given NF requirement, the current-reuse P-type metal-oxide-semiconductor (PMOS) and N-type metal-oxide-semiconductor (NMOS) self-biased amplifier with a VDD of 1 V consumes half of the current of a single NMOS (or PMOS) without current-reuse and with a VDD of 0.5 V. This constraint is even tighter if a small chip area and/or no/limited external components are imposed for cost reduction. As an example, inductors/transformers can help to boost the operating frequency and bias the circuit with lower voltage headroom and noise. If inductors/transformers cannot be used due to the limited area budget, only resistors or transistors can be adopted instead. This imposes a hard trade-off with IIP3, NF and bandwidth. Thus, to balance the VDD, current, area and external components with the key performance metrics (NF and out-of-band (OB) IIP3), effective system-to-circuit-level co-design, RF and analog circuit techniques become highly important and correlated. The next two sections present the key circuit techniques applied into two state-of-the-art cost-aware ULP receivers: one for the 2.4-GHz band and one for the sub-GHz bands.

14.3 Current-Reuse ULP Receiver Techniques for the 2.4-GHz ISM Band

Nanoscale CMOS offers sufficiently high ft and low Vt favoring the design of ULP receivers via stacking the RF-to-baseband (BB) functions in one cell, while sharing the smallest possible bias current. Also, the signals can be conveyed in the current domain to enhance the area efficiency (i.e., no AC-coupling capacitor), RF bandwidth and linearity at those inner nodes. The proposed Zigbee receiver (Lin et al. 2013, 2014a) is inspired by the above hypothesis, and its block diagram is depicted in Fig. 14.1.

The single-ended RF input (VRF) is taken by a low-Q input-matching network before reaching the Balun-LNA-I/Q-Mixer (Blixer). Merging the Blixer with the hybrid filter not only saves power, but also reduces the voltage swing at internal nodes benefitting the linearity. The wideband input-matching network is also responsible for the passive pre-gain to reduce the NF. Unlike the LMV cell that only can utilize single-balanced mixers (Tedeschi et al. 2010), here the balun-LNA featuring a differential output (±iLNA) allows the use of double-balanced mixers (DBMs). Driven by a 4-phase 25% LO, the I/Q-DBMs with a large output resistance robustly correct the differential imbalances of ±iLNA. The balanced BB currents (±iMIX,I and ±iMIX,Q) are then filtered directly in the current domain by a current-mode Biquad stacked atop the DBM. The Biquad features in-band noise-shaping centered at the desired intermediate frequency (IF, 2 MHz). Only the filtered output currents (±irLPF,I and ± irLPF,Q) are returned as voltages (±Vo,I and ±Vo,Q) through the complex-pole load, which performs both image rejection and channel selection. Out of the current-reuse path there is a high-swing variable-gain amplifier (VGA). It essentially deals with the gain loss of its succeeding 3-stage passive RC-CR polyphase filter (PPF), which is responsible for large and robust image rejection over mismatches and process variations. The final stage is an inverter amplifier before 50-Ω test buffering. The 4-phase 25% LO can be generated by an external 4.8-GHz reference (LOext) after a divide-by-2 (DIV1) that features 50%-input 25%-output, or from an integrated 10-GHz VCO after DIV1 and DIV2 (25%-input 25%-output) for additional testability.

14.3.1 Circuit Implementation

Wideband Input-Matching Network—As shown in Fig. 14.2a, a low-Q inductor (LM) and 2 tapped capacitors (Cp and CM) can be employed for impedance down-conversion resonant and passive pre-gain. A high-Q inductor is unnecessary since the Q of the LC matching is dominated by the low input resistance of the LNA. Thus, a low-Q inductor results in area savings, while averting the need of an external inductor for cost savings. LM also serves as the bias inductor for M1. Rp is the parallel shunt resistance of LM. Cp stands for the parasitic capacitance from the pad and ESD diodes. Rin and Cin are the equivalent resistance and capacitance at node Vin, respectively. R’in is the downconversion resistance of Rin.

LBW is the bondwire inductance and Rs is the source resistance. To simplify the analysis, we first omit LBW and Cin, so that LM, Cp, CM, RS and RT (= Rp//Rin) together form a tapped capacitor facilitating the input matching. Generally, S11 ≤ –10 dB is required and the desired value of R’in is from 26 to 97 Ω over the frequency band of interest. Thus, given the RT and CM values, the tolerable Cp can be derived from \( {\mathrm{R}}_{\mathrm{in}}^{,}={\mathrm{R}}_{\mathrm{T}}{\left(\frac{{\mathrm{C}}_{\mathrm{M}}}{{\mathrm{C}}_{\mathrm{M}}+{\mathrm{C}}_{\mathrm{p}}}\right)}^2 \). The pre-gain value (Apre,amp) from VRF to Vin is derived from \( \frac{{\mathrm{V}}_{\mathrm{in}}^2}{2{\mathrm{R}}_{\mathrm{T}}}=\frac{{\mathrm{V}}_{\mathrm{R}\mathrm{F}}^2}{2{\mathrm{R}}_{\mathrm{S}}} \), which can be simplified as \( {\mathrm{A}}_{\mathrm{pre},\mathrm{amp}}=\sqrt{\frac{{\mathrm{R}}_{\mathrm{T}}}{{\mathrm{R}}_{\mathrm{S}}}} \). The –3-dB bandwidth of Apre,amp is related to the network’s quality factor (Qn) as given by: \( {\mathrm{Q}}_{\mathrm{n}}=\frac{{\mathrm{R}}_{\mathrm{T}}}{2{\upomega}_0{\mathrm{L}}_{\mathrm{M}}}=\frac{\upomega_0}{\upomega_{-3\mathrm{dB}}} \), with \( {\upomega}_0=\frac{1}{\sqrt{{\mathrm{L}}_{\mathrm{M}}{\mathrm{C}}_{\mathrm{EQ}}}} \) and \( {\mathrm{C}}_{\mathrm{EQ}}=\frac{{\mathrm{C}}_{\mathrm{M}}{\mathrm{C}}_{\mathrm{p}}}{{\mathrm{C}}_{\mathrm{M}}+{\mathrm{C}}_{\mathrm{p}}} \).

In our design (RT = 150 Ω, CM = 1.5 pF, LM = 4.16 nH, Rp = 600 Ω, Cp = 1 pF and Rin = 200 Ω), Apre,amp has a passband gain of ~4.7 dB over a 2.4-GHz bandwidth (at RF = 2.4 GHz) under a low Qn of 1. Thus, the tolerable Cp is sufficiently wide (0.37 to 2.1 pF). The low-Q LM is extremely compact (0.048 mm2) in the layout and induces a small parasitic capacitance (~260 fF, part of Cin). Figure 14.2b demonstrates the robustness of S11-bandwidth against LBW from 0.5 to 2.5 nH. The variation of Cin to S11-bandwidth was also studied. From simulations, the tolerable Cin is 300 to 500 f. at LBW = 1.5 nH.

Balun-LNA—The common-gate (CG) common-source (CS) balun-LNA (Blaakmeer et al. 2008a ) avoids the off-chip balun and achieves a low NF by noise canceling, but the asymmetric CG-CS transconductances and loads make the output balancing not wideband consistent. In Blaakmeer et al. (2008b), output balancing is achieved by scaling M5–8 with cross-connection at BB, but that is incompatible with this work that includes a hybrid filter. In Mak and Martins (2011), by introducing an AC-coupled CS branch and a differential current balancer (DCB), the same load is allowed for both CS and CG branches for wideband output balancing. Thus, the NF of such a balun-LNA can be optimized independently. This technique is transferred to this ULP design, but only with the I/Q-DBMs inherently serves as the DCB, avoiding a high VDD (Mak and Martins 2011). The detailed schematic is depicted in Fig. 14.2a. To maximize the voltage headroom, M1 (with gm,CG) and M2 (with gm,CS) were sized with non-minimum channel length (L = 0.18 μm) to lower their VT. The AC-coupled gain stage is a self-biased inverter amplifier (AGB) powered at 0.6-V (VDD06) to enhance its transconductance (gm,AGB)-to-current ratio. It gain-boosts the CS branch while creating a loop gain around M1 to enhance its effective transconductance under less bias current (IBIAS). This scheme also allows the same IBIAS for both M1 and M2, requiring no scaling of load (i.e., only RL). Furthermore, a small IBIAS lowers the supply requirement, making a 1.2-V supply (VDD12) still adequate for the Blixer and hybrid filter, while relaxing the required LO swing (LOIP and LOIn). C1–3 for biasing are typical metal-oxide-metal (MoM) capacitors to minimize the parasitics.

The balun-LNA features partial-noise canceling. To simplify the study, we ignore the noise induced by DBM (M5–M8) and the effect of channel-length modulation. The noise transfer function (TF) of M1’s noise (In,CG) to the BB differential output (Vo,Ip – Vo,In) can be derived when LOIp is high, and the input impedance is matched,

where Gm,CS = gm,CS + gm,AGB. The noise of M1 can be fully canceled if RinGm,CS = 1 is satisfied. However, Rin ≈ 200 Ω is desired for input matching at low power. Thus, Gm,CS should be ≈5 mS, rendering the noises of Gm,CS and RL still significant. Thus, device sizings for full noise cancellation of M1 should not lead to the lowest total NF (NFtotal). In fact, one can get a more optimized Gm,CS (via gm,AGB) for stronger reduction of noise from Gm,CS and RL, instead of that from M1. Although this noise-canceling principle has been discussed in Bruccoleri et al. (2004) for its single-ended LNA, the output balancing was not a concern there. Here, the optimization process is alleviated since the output balancing and NF are decoupled. The simulated NFtotal up to the Vo,Ip and Vo,In nodes against the power given to the AGB is given in Fig. 14.2c. NFtotal is reduced from 5.5 dB at 0.3 mW to 4.9 dB at 0.6 mW, but is back to 5 dB at 0.9 mW. Due to the use of passive pre-gain and a larger Rp that is ~3 times of Rin, the noise contribution of the inductor is <1% from simulations. The simulated NF at the outputs of the LNA and test buffer are 5.3 and 6.6 dB, respectively.

Double-Balanced Mixers Offering Output Balancing—The output balancing is inherently done by the I/Q-DBMs under a 4-phase 25% LO. For simplicity, this principle is described for the I channel only under a 2-phase 50% LO, as shown in Fig. 14.3, where the load is simplified as RL. During the first-half LO cycle when LOIp is high, iLNAp goes up and appears at Vo,Ip while iLNAn goes down and appears at Vo,In. In the second-half LO cycle, both of the currents’ sign and current paths of iLNAp and iLNAn are flipped. Thus, when they are summed at the output during the whole LO cycle, the output balancing is robust, thanks to the large output resistance (9 kΩ) of M5-M8 enabled by the very small IBIAS (85 μA). To analytically prove the principle, we let \( {\mathrm{i}}_{\mathrm{LNAp}}={\upalpha \mathrm{I}}_{\mathrm{A}} \cos \left({\upomega}_{\mathrm{s}}\mathrm{t}+{\upvarphi}_1\right) \) and \( {\mathrm{i}}_{\mathrm{LNAn}}=-{\mathrm{I}}_{\mathrm{A}} \cos \left({\upomega}_{\mathrm{s}}\mathrm{t}+{\upvarphi}_2\right) \), where IA is the amplitude, ωs is the input signal frequency, α is the unbalanced gain factor and φ1 and φ2 are their arbitrary initial phases. When there is sufficient filtering to remove the high-order terms, we can deduce the BB currents iMIX,Ip and iMIX,In as given by,

and a consistent proof for I/Q-DBMs under a 4-phase 25% LO is obtained. Ideally, the DBM can correct perfectly the gain and phase errors from the balun-LNA, independent of its different output impedances from the CG and CS branches. In fact, even if the conversion gain of the 2 mixer pairs (M5, M8 and M6, M7) does not match (e.g., due to non-50% LO duty cycle), the double-balanced operation can still generate balanced outputs (confirmed by simulations). Of course, the output impedance of the DBM can be affected by that of the balun-LNA [Fig. 14.2a], but is highly desensitized due to the small size of RL (i.e., the input impedance of the hybrid filter) originally aimed for current-mode operation. Thus, the intrinsic imbalance between Vo,lp and Vo,ln is negligibly small (confirmed by simulations).

For devices sizing, a longer channel length (L = 0.18 μm) is preferred for M5–8 to reduce their 1/f noise and Vt. Hard-switch mixing helps to desensitize the I/Q-DBMs to LO gain error, leaving the image rejection ratio (IRR) mainly determined by the LO phase error that is a tradeoff with the LO-path power. Here, the targeted LO phase error is relaxed to ~4o, as letting the BB circuitry (i.e., the complex-pole load and 3-stage RC-CR PPF) to handle the IRR is more power efficient.

Hybrid Filter 1 st Half—Current-Mode Biquad with IF Noise-Shaping—The current-mode Biquad [Fig. 14.4a] proposed in Pirola et al. (2010) is an excellent candidate for current-reuse with the Blixer for channel selection. However, this Biquad only can generate a noise-shaping zero spanning from DC to \( \sim 2\uppi 0.1{\mathrm{Q}}_{\mathrm{B}}{\upomega}_{0\mathrm{B}}\ \mathrm{MHz} \) for Mf1–Mf2, where QB and ω0B are the Biquad’s quality factor and –3-dB cutoff frequency, respectively. This noise shaping is hence ineffective for our low-IF design having a passband from ω1 to ω2 (= ω0B), where ω1 > 0.1QBω0B. To address this issue, an active inductor (Lact) is added at the sources of Mf1–Mf2. The LactCf1 resonator shifts the noise-shaping zero to the desired IF. The cross-diode connection between Mi1–Mi4 (all with gm,act) emulate Lact ≈ Ci/gm,act 2 (Ler et al. 2008; Chen et al. 2012). The small-signal equivalent circuit to calculate the noise TF of in,Mf1/in,out is shown in Fig. 14.4b. The approximated impedance of ZP in different frequencies related to ω0r is summarized in Fig. 14.5a, where \( {\upomega}_{0\mathrm{r}} = \frac{\upomega_1+{\upomega}_2}{2} \) is the resonant frequency of LactCf1 at IF. The simulated in,Mf1/in,out is shown in Fig. 14.5b. At the low frequency range, ZP behaves inductively, degenerating further in,Mf1 when the frequency is increased. At the resonant frequency, ZP = Rsf, where Rsf is the parallel impedance of the active inductor’s shunt resistance and DBM’s output resistance. The latter is much higher when compared with RL thereby suppressing in,Mf1. At the high frequency range, ZP is more capacitive dominated by Cf1. It implies in,Mf1 can be leaked to the output via Cf1, penalizing the in-band noise. At even higher frequencies, the output noise decreases due to Cf2, being the same as its original form (Pirola et al. 2010).

The signal TF can be derived from Fig. 14.6. Here \( {\mathrm{R}}_{\mathrm{L}}=\frac{1}{{\mathrm{g}}_{\mathrm{mf}}},\ {\mathrm{L}}_{\mathrm{biq}}=\frac{{\mathrm{C}}_{\mathrm{f}2}}{{\mathrm{g}}_{\mathrm{mf}}^2} \). For an effective improvement of NF, Lact ≫ Lbiq should be made. The simulated NFtotal at Vo,Ip and Vo,In with and without the Lact is shown Fig. 14.6, showing about 0.1 dB improvement at the TT corner (reasonable contribution for a BB circuit). For the SS and FF corners, the NF improvement reduces to 0.04 and 0.05 dB, respectively. These results are expected due to the fact that at the FF corner, the noise contribution of the BB is less significant due to a larger bias current; while at the SS corner, the IF noise-shaping circuit will add more noise by itself, offsetting the NF improvement. Here Mf1–Mf4 use isolated P-well for bulk-source connection, avoiding the body effect while lowering their VT.

Hybrid Filter 2nd Half—Complex-Pole Load—Unlike most active mixers or the original Blixer (Blaakmeer et al. 2008a, b) that only use a RC load, the proposed “load” synthesizes a 1st-order complex pole at the positive IF (+IF) for channel selection and image rejection. The circuit implementation and principle are shown in Fig. 14.7a and b, respectively. The real part (RL) is obtained from the diode-connected ML, whereas the imaginary part (gm,Mc) is from the I/Q-cross-connected MC. The entire hybrid filter offers 5.2-dB IRR, and 12-dB (29-dB) adjacent (alternate) channel rejection as shown in Fig. 14.8 (the channel spacing is 5 MHz). Similar to gm-C filters the center frequency is defined by gm,McRL.. When sizing the –3-dB bandwidth, the output conductances of MC and ML should be taken into account.

Current-Mirror VGA and RC-CR PPF—Outside the current-reuse path, Vo,I and Vo,Q are AC-coupled to a high swing current-mirror VGA formed with ML [Fig. 14.7a] and a segmented MVGA (Fig. 14.9), offering gain controls with a 6-dB step size. To enhance the gain precision, the bias current through MVGA is kept constant, so as its output impedance. With the gain switching of MVGA, the input-referred noise of MVGA will vary. However, when the RF signal level is low the gain of the VGA should be high, rendering the gain switching not influencing the receiver’s sensitivity. The VGA is responsible for compensating the gain loss (30 dB) of the 3-stage passive RC-CR PPF that provides robust image rejection of >50 dB (corner simulations). With the hybrid filter rejecting the out-band blockers the linearity of the VGA is further relaxed, so as its power budget (192 μW, limited by the noise and gain requirements).

A 3-stage RC-CR PPF can robustly meet the required IRR in the image band (i.e., the –IF), and cover the ratio of maximum to minimum signal frequencies (Kaykovuori et al. 2008; Behbahani et al. 2001). In our design, the expected IRR is 30 to 40 dB and the ratio of frequency of the image band is fmax/fmin (=3). However, counting the RC variations as large as ±25%, the conservative Δfeff = fmax_eff/fmin_eff should be close to 5. The selected RC values are guided by Behbahani et al. (2001)

Accordingly, the matching of the resistors (σR) and capacitors (σC) can be relaxed to 0.9% (2.93%) for 40-dB (30-dB) IRR with a 3σ yield. Here, ~150-kΩ resistors are chosen to ease the layout with a single capacitor size (470 fF), balancing the noise, area and IRR. The simulated worst IRR is 36 dB without LO mismatch, and still over 27 dB at a 4o LO phase error checked by 100x Monte-Carlo simulations. Furthermore, if the 5-dB IRR offered by the complex-pole load is added the minimum IRR of the IF chain should be 32 dB. The final stage before 50-Ω output buffering is a self-biased inverter amplifier (power = 144 μW), which embeds one more real pole for filtering. The simulated overall IF gain response is shown in Fig. 14.10, where the notches at DC offered by the AC-coupling network, and around the –IF offered by the 3-stage RC-CR PPF, are visible. The IRR is about 57 dB [=52 dB (RC-CR PPF) + 5 dB (complex-pole load)] under an ideal 4-phase 25% LO for the image band from [fLO – 3, fLO – 1] MHz.

VCO and Dividers and LO Buffers—To fully benefit the speed and low-Vt advantages of fine linewidth CMOS, the entire LO path is powered at a lower supply of 0.6 V to reduce the dynamic power. For additional testability, an on-chip VCO is integrated. It is optimized at ~10 GHz to save area and allows division by 4 for I/Q generation. The loss of its LC tank is compensated by complementary NMOS-PMOS negative transconductors.

The divider chain [Fig. 14.11a] cascades two types of div-by-2 circuits (DIV1 and DIV2) to generate the desired 4-phase 25% LO, from a 2-phase 50% output of the VCO. The two latches (D1 and D2) are employed to build DIV1 that can directly generate a 25% output from a 50% input (Razavi et al. 1995), resulting in power savings due to less internal logic operation (i.e., AND gates) and load capacitances. Each latch consists of two sense devices, a regenerative loop and two pull up devices. For 25%-input 25%-output division, DIV2 is proposed that it can be directly interfaced with DIV1. The 25% output of DIV1 are combined by MD1 to MD4 to generate a 50% clock signal for D3 and D4.

For testing under an external LOext source at 4.8 GHz, another set of D1 and D2 is adopted. The output of these two sets of clocks are combined by transmission gates and then selected. Although their transistor sizes can be reduced aggressively to save power, their drivability and robustness in process corners can be degraded. From simulations, the sizing can be properly optimized. The four buffers (Buf1–4) serve to reshape the pulses from DIV2 and enhance the drivability. The timing diagram is shown in Fig. 14.11b. Due to the very small IBIAS for the I/Q-DBMs, a LO amplitude of around 0.4 Vpp is found to be more optimized in terms of NF and gain as simulated and shown in Fig. 14.12a. To gain benefits from it CLO is added to realize a capacitor divider with CMIX,in (input capacitance of the mixer) as shown in Fig. 14.12b. This act brings down the equivalent load (CL,eq) of Buf1–4 by ~33%.

14.3.2 Experimental Results

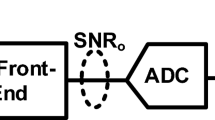

The ZigBee receiver was fabricated in 65-nm CMOS (Fig. 14.13) and optimized with dual supplies (1.2 V: Blixer + hybrid filter, 0.6 V: LO and BB circuitries). The die area is 0.24 mm2 (0.3 mm2) without (with) counting the LC-tank VCO. Since there is no frequency synthesizer integrated, the results in Fig. 14.14a–d were measured under LOext for accuracy and data repeatability. The S11-BW (<–10 dB) is ~1.3 GHz for both chip-on-board (CoB) and CQFP-packaged tests [Fig. 14.14a], which proves its immunity to board parasitics and packaging variations. The gain (55–57 dB) and NF (8.3–11.3 dB) are also wideband consistent [Fig. 14.14b]. The gain peak at around 2.4–2.5 GHz is from the passive pre-gain. Following the linearity test profile of Tedeschi et al. (2010), two tones at [LO + 12 MHz, LO + 22 MHz] are applied, measuring an IIP3out-band of –6 dBm [Fig. 14.14c] at the maximum gain of 57 dB (there is 24-dB gain loss in Fig. 14.14c associated with the test buffer and used 1:8 transformer). This high IIP3 is due to the direct current-mode filtering at the mixer’s output before signal amplification. The asymmetric IF response [Fig. 14.14d] shows 22-dB (43-dB) rejection at the adjacent (alternate) channel, and 36-dB IRR. Differing from the simulated IF frequency response that has three notches at the image band under an ideal LO, the measured notches are merged. Similar to Behbahani et al. (2001), this discrepancy is likely due to the LO gain and phase mismatches, and the matching and variations of the RC-CR networks. The layout design is similar to Behbahani et al. (2001) that uses dummy to balance the parasitic capacitances. The filtering rejection profile is ~80 dB/decade. The spurious free dynamic range (SFDR) is close to 60 dB according to Tedeschi et al. (2010),

where SNRmin = 4 dB is the minimum signal-to-noise ratio required by the application, and BW = 2 MHz is the channel bandwidth.

The receiver was further tested at lower voltage supplies as summarized in Table 14.2. Only the NF degrades more noticeably, the IIP3, IRR and BB gain are almost secured. The better IIP3 for 0.6-V/1-V operation is mainly due to the narrower –3-dB bandwidth of the hybrid filter. For the 0.5-V/1-V operation, the degradation of IIP3out-band is likely due to the distortion generated by AGB. Both cases draw very low power down to 0.8 mW, being comparable with other ULP designs such as Herberg et al. (2011).

The LC-tank VCO was tested separately. Its power budget is related with its output swing and is a tradeoff with the phase noise, which measures—114 dBc/Hz at 3.5 MHz that has an enough margin to the specifications (Liscidini et al. 2008) [Fig. 14.15a]. Porting it to the simulation results, it can be found that the corresponding VCO’s output swing is 0.34 Vpp and the total LO-path power is 1.7 mW (VCO + dividers + BUFs). Such an output swing is adequate to lock DIV1 as shown in its simulated sensitivity curve [Fig. 14.15b].

The chip summary and performance benchmarks are given in Table 14.3, where (Tedeschi et al. 2010) is a current-reuse architecture and (Zhang et al. 2013) is an ultra-low-voltage design. For this work, the results measured under a 10-GHz on-chip VCO are also included for completeness, but they are more sensitive to test uncertainties. The degraded NF and IRR are mainly due to the phase noise of the free-running VCO. In both cases, this work succeeds in advancing the IIP3out-band, power and area efficiencies, while achieving a wideband S11 with zero external components. Particularly, when comparing with the recent work (Zhang et al. 2013), this work achieves 8x less area and 15.5 dBm higher IIP3, together with stronger BB channel selectivity.

14.4 Function-Reuse ULP Receiver Techniques for the Sub-GHz ISM Bands

Differing from the previous design that is for single band, the function-reuse receiver (Lin et al. 2014b, c) to be described here can flexibly support multiple bands (433/860/915/960 MHz) and can operate at a single low VDD. It features a gain-boosted N-path switched-capacitor (SC) network embedded into a function-reuse RF front-end, offering concurrent RF (common-mode) and BB (differential-mode) amplification, LO-defined RF filtering, and input impedance matching with zero external components. The details are presented next.

14.4.1 Receiver Architecture

Specifically, the gain-boosted 4-path SC network [Fig. 14.16a] separates the output of each gain stage Gm (Gm has a transconductance of gm3, output resistance of 4RL, and feedback resistor of RF3) with capacitor Co that is an open circuit at BB. The I/Q BB signals at VB1,I± and VB1,Q± are further amplified along the Path C [Fig. 14.16b] by each Gm stage. With the memory effect of the capacitors, the functional view of the gain response is shown in Fig. 14.16c. In order to achieve current-reuse between the RF LNA and BB amplifiers without increasing the VDD, the circuit published in Han and Gharpurey (2008) with an active mixer has a similar function. However, the BB NF behavior and the RF filtering behavior are different from the N-path passive mixer applied here that is at the feedback path. For the BB amplifiers, it is one Gm with one RF3, balancing the BB gain and OB-IIP3. After considering that the BB amplifiers have been absorbed in the LNA, the I/Q passive mixers and capacitors absorbed by the 4-path SC network, the blocks after the LNA can be assumed virtual. These virtual blocks reduce the power, area and NF. To validate the above viewpoint, the gain and noise performances under two sets of RF3 are simulated. Here, the virtual blocks in Fig. 14.16c are implemented with physical transistors and capacitors for the BB amplifiers and the mixers while the buffer is ideal. Thus, the power of the modeled receiver is at least 2x larger than the proposed receiver. For the IB BB gain at VB2,I± (VB2,Q±) between the proposed function-reuse receiver and its functional view, the difference is only 1 dB at a large RF3 of 150 kΩ [Fig. 14.17a]. For a small RF3, the gain error goes up to 2 dB [Fig. 14.17b], which is due to the gain difference between the model of the N-path tunable LNA [Fig. 14.16c] and the implementation of the function-reuse receiver that has AC-coupling. For the NF difference (ΔNF), with a large (small) RF3, it is ~0.8 dB (3.5 dB) as compared in Fig. 14.18a, b. This is due to the lower gain at the LNA’s output, forcing the input-referred noise from the downconversion passive mixers and the BB amplifiers to increase with a small RF3. Either with a small or large RF3, it is noteworthy that the variation of BB NF is small (i.e., for RF3 = 20 kΩ it is 3.6 dB while for RF3 = 150 kΩ it is 3.4 dB), because the BB NTF has a weak relation with RF3. It also indicates that the BB NTF is weakly related with the gain at the LNA’s output, which is dissimilar to the usual receiver where the NF should be small when the LNA’s gain is large. Similarly, the NF at the LNA’s output (now shown) can be larger than that at BB due to the different NTFs.

14.4.2 Low-Voltage Current-Reuse VCO-Filter

In order to further optimize the power, the VCO is designed to current-reuse with the BB complex low-IF filter (Fig. 14.19). The negative transconductor of the VCO is divided into multiple Mv cells. The aim is to distribute the bias current of the VCO to all BB gain stages (A1, A2…A18) that implement the BB filter. For the VCO, MV operates at the frequency of 2fs or 4fs for a div-by-2 or div-by-4 circuit. Thus, the VCO signal leaked to the source nodes of MV (VF1,I+, VF1,I-) is pushed to very high frequencies (4fs or 8fs) and can be easily filtered by the BB capacitors. For the filter’s gain stages such as A1, Mb (gMb) is loaded by an impedance of ~1/2gMv when Lp can be considered as a short circuit at BB. Thus, A1 has a ratio-based voltage gain of roughly gMb/gMv, or as given by 4TgMb/GmT, where GmT is the total trans-conductance for the VCO tank. The latter shows how the distribution factor T can enlarge the BB gain, but is a tradeoff with its input-referred noise and can add more layout parasitics to Vvcop,n (i.e., narrower VCO’s tuning range). The –R cell using cross-coupled transistors is added at VF1,I+ and VF1,I- to boost the BB gain without loss of voltage headroom. For the BB complex poles, A2,5 and Cf1 determine the real part while A3,6 and Cf1 yield the imaginary part. There are three similar stages cascaded for higher channel selectivity and image rejection ratio (IRR). Rblk and Cblk were added to avoid the large input capacitance of A1,4 from degrading the gain of the front-end.

14.4.3 Experimental Results

Two versions of the receiver were fabricated in 65-nm CMOS (Fig. 14.20) and optimized with a single 0.5-V VDD. With (without) the LC tank for the VCO, the die area is 0.2 mm2 (0.1 mm2). Since the measurement results of both are similar, only those measured with VCO in Fig. 14.21a–d are reported here. From 433 to 960 MHz, the measured BB gain is 50 ± 2 dB. Two tones at [fs + 12 MHz, fs + 22 MHz] are applied, measuring an OB-IIP3 of –20.5 ± 1.5 dBm at the maximum gain. The IRR is 20.5 ± 0.5 dB due to the low-Q of the VCO-filter. The IIP3 is mainly limited by the VCO-filter. The measured NF is 8.1 ± 0.6 dB. Since the VCO is current-reuse with the filter, it is interesting to study its phase noise with the BB signal amplitude. For negligible phase noise degradation, the BB signal swing should be <60 mVpp, which can be managed by variable gain control. If a 60-mVpp BB signal is insufficient for demodulation, a simple gain stage (e.g., inverter amplifier) can be added after the filter to enlarge the gain and output swing. The total power of the receiver is 1.15 mW (0.3 mW for the LNA + BB amplifiers and 0.65 mW for VCO-filter and 0.2 mW for the divider), while the phase noise is –117.4 ± 1.7 dBc/Hz at 3.5-MHz frequency offset. The S11 is below –8 dB across the whole band. The asymmetric IF response shows 24-dB (41-dB) rejection at the adjacent (alternate) channel.

To study the RF filtering behavior, the P1dB and blocker NF are measured. For the in-band signal, the P1dB is –55 dBm while with a frequency offset frequency of 20 MHz, it increases to –35 dBm, which is mainly due to the double-RF filtering [Fig. 14.22a]. For an offset frequency of 60 MHz, the P1dB is –20 dBm, limited by the current-reuse VCO-filter. For the blocker NF, with a single tone at 50 MHz, the blocker NF is almost unchanged for the blocker <–35 dBm. With a blocker power of –20 dBm, the NF is increased to ~14 dB [Fig. 14.22b].

This work is compared with the prior art in Table 14.4, where (Lin et al. 2013) is the current-reuse architectures described previously, while (Zhang et al. 2013) is the cascade architecture with ULV supply for energy harvesting. For this work, the results measured under an external LO are also included for completeness. In both cases, this work succeeds in advancing the power and area efficiencies with multi-band convergence, while achieving tunable S11 with zero external components. When comparing with the most recent ULV design (Zhang et al. 2013), this work saves more than 10x of area while supporting multi-band operation with zero external components.

14.5 Sub-1 V ULP 2.4GHz Transmitter

This section briefly covers an ongoing-design of a sub-1 V ULP 2.4-GHz transmitter (TX) with scalable output power (Pout) and system efficiency for ZigBee and other Internet-of-Things wireless solutions.

To improve the system efficiency of a TX, which normally consists of a VCO (or DCO) and a power amplifier, it is worth to consider a current-reuse topology between the two blocks. The current-reuse VCO-PA (Li et al. 2015) has demonstrated good system efficiency (17.5%), but has a limited Pout (-1 dBm) after stacking. Thus, our recent work (Peng et al. 2017) reported a function-reuse DCO-PA that not only shares bias current, but also upholds a full VDD for both the DCO and PA operation.

Here, the basic circuit is inspired by the class-F oscillator (Fig. 14.23), which is attractive for its high FoM of 192 dBc/Hz (Babaie et al. 2013). It features a resonant tank (LpCp, LsCs) with a moderately-coupling k to peak up the drain impedance (Zd) at both 1st and 3rd harmonics, resulting in a pseudo-square drain voltage (Vd) to reduce the oscillator’s impulse sensitivity function. Although Vd and the drain current (Id) are alike a square-wave, the tank’s resonant response recovers a sine Vg by suppressing the harmonic components, while offering a passive gain to Vg under step-up ratioing (Ls > Lp). These properties are preserved when it is modified as a class-F VCO that can directly up the antenna (Fig. 14.24). This scheme reuses the amplifying device (M1) to unify the DCO and PA functions for power and area savings (Table 14.5).

Class-F VCO (Babaie et al. 2013)

Ongoing work on a Class-F VCO driving up the antenna (Peng et al. 2016)

L1–3 form a transformer enabling self-oscillation and boosts up Vg by step-up ratioing (L3 > L1), and output-impedance matching to deliver adequate Pout (>0 dBm) to RL. The coupling coefficients can be customized for optimum performance.

14.6 Conclusions and Future Perspectives

This chapter described the system aspects and circuit techniques of building cost-aware ultra-low-power (ULP) radios for both 2.4-GHz and sub-GHz ISM bands. We demonstrated that effective co-design between the system and circuit levels, as well as RF and analog block levels, are decisive to concurrently balance the cost and power budgets, while keeping up the radio performance without resorting from external components. Other state-of-the-art techniques are summarized in Lin et al. (2016) and Yu et al. (2017).

For future development, to cope with the fast market shift and many upcoming applications, multi-band multi-standard ULP radios with flexible data rate will become promising for the future IoT growth. In addition to the obvious goal of high energy efficiency during the active mode of the radios, they should also be designed for very low sleep/leakage power, preferably in the range of pW (Paidimarri et al. 2015), such that after heavily duty cycling, the average system power can be minimized. The technology choices also offer the flexibility of using low-Vt thin-oxide transistors for core circuits such that a lower VDD can be used to save power, whereas high-Vt or thick-oxide transistors can be used to suppress the sleep current. Mixed-VDD design can be a chip-level strategy for power savings (Mak and Martins 2012).

To save power, it is possible to avoid the RF PLL for channelization by using a temperature-compensated thin-film bulk-acoustic-wave resonator (FBAR) that assists the RF-to-IF downconversion. Thus, the channel selection can be delayed to lower frequency (Wang et al. 2014).

The average power is critical for a long battery lifetime, as it will dominate the maintenance cost of massive-scale wireless sensor networks. This fact urges the need of highly autonomous ULP radios that can survive with mainly/only energy harvesting. To this point, fully-integrated ULP power management units and multi-source energy harvesters will be of great importance (Masuch et al. 2013).

For the transceiver, although the sensitivity of a state-of-the-art ULP receiver is better than −90 dBm (Liu et al. 2014), their tolerability to large out-of-band blockers should have room to be further improved. The gain-boosted N-path filtering technique (Lin et al. 2014c) can be a helpful technique to enhance the resilience of the receiver. For the state-of-the-art transmitters, their power efficiency is still not that high (Liu et al. 2015a) at a 0-dBm output power. Thus, it is worth to revisit the design of ULP PA and VCO as described in (Peng et al. 2017).

LO generation can consume significant power and area when approaching multi-band operation. For example, for a universal radio to cover the 2.4 GHz and sub-GHz ISM bands, the tuning range of the VCO should be 57% if a 2.4-GHz VCO is selected and followed by a divide-by-4 circuit. Such a wide tuning range should consume more power than the single-band design. In fact, from area and tuning range’s viewpoint, a ring oscillator can be more attractive. However, to meet the required phase noise, ULP consumption is still challenging. Time-interleaved ring oscillator (Yin et al. 2016a, b) with effective phase noise reduction offers the potential to alleviate this tradeoff.

References

M. Babaie, R. Staszewski, Third-harmonic injection technique applied to a 5.87-to-7.56 GHz 65nm class-F oscillator with 192 dBc/Hz FoM. ISSCC Dig. Tech. Papers (Feb. 2013), pp. 348–349

S. Bandyopadhyay, A. Chandrakasan, Platform architecture for solar, thermal and vibration energy combining with MPPT and single inductor, in Proceedings Symposium on VLSI Circuits (2011), pp. 238–239

F. Behbahani, Y. Kishigami, J. Leete, A.A. Abidi, CMOS mixers and polyphase filters for large image rejection. IEEE J. Solid-State Circuits 36, 873–887 (2001)

S. Blaakmeer, E. Klumperink, D. Leenaerts, B. Nauta, Wideband balun-LNA with simultaneous output balancing, noise-canceling and distortion-canceling. IEEE J. Solid-State Circuits 43, 1341–1350 (2008a)

S. Blaakmeer, E. Klumperink, D. Leenaerts, B. Nauta, The blixer, a wideband Balun-LNA-I/Q-mixer topology. IEEE J. Solid-State Circuits 43, 2706–2715 (2008b)

F. Bruccoleri, E. Klumperink, B. Nauta, Wide-band CMOS low-noise amplifier exploiting thermal noise canceling. IEEE J. Solid-State Circuits 39, 275–282 (2004)

Y. Chen, P.-I. Mak, L. Zhang, Y. Wang, A 0.07mm2, 2mW, 75MHz-IF, 4th-order BPF using a source-follower-based resonator in 90 nm CMOS. IET Electron. Lett. 48, 552–554 (2012)

J. Han, R. Gharpurey, Recursive receiver down-converters with multiband feedback and gain-reuse. IEEE J. Solid-State Circuits 43, 1119–1131 (2008)

A.C. Herberg, T.W. Brown, T.S. Fiez, K. Mayaram, A250-mV, 352-μW GPS receiver RF front-end in 130-nm CMOS. IEEE J. Solid-State Circuits 46(4), 938–949 (2011)

J. Kaykovuori, K. Stadius, J. Ryynanen, Analysis and design of passive polyphase filters. IEEE Trans. Circuits Syst. I, Reg. Papers 55, 3023–3037 (2008)

C.L. Ler, A.K. A’ain, A.V. Kordesh, CMOS source degenerated differential active inductor. IET Electron. Lett. 44, 196–197 (2008)

C. Li, A. Liscidini, A current re-use PA-VCO cell for low-power BLE transmitters, in European Solid-State Circuits Conference, Paper No. 1198 (Sept. 2015)

Z. Lin, P.-I. Mak, R.P. Martins, A 1.7 mW 0.22 mm2 2.4 GHz ZigBee RX exploiting a current-reuse Blixer + Hybrid filter topology in 65nm CMOS. ISSCC Dig. Tech. Papers (Feb. 2013), pp. 448–449

Z. Lin, P.-I. Mak, R.P. Martins, A 2.4-GHz ZigBee receiver exploiting an RF-to-BB-current-reuse Blixer + Hybrid filter topology in 65-nm CMOS. IEEE J. Solid-State Circuits 49, 1333–1344 (2014a)

Z. Lin, P.-I. Mak, R. P. Martins, A 0.5V 1.15mW 0.2mm2 Sub-GHz ZigBee receiver supporting 433/860/915/960MHz ISM bands with zero external components. ISSCC Dig. Tech. Papers (Feb. 2014b), pp. 164–165

Z. Lin, P.-I. Mak, R.P. Martins, A Sub-GHz multi-ISM-band ZigBee receiver using function-reuse and gain-boosted N-path techniques for IoT applications. IEEE J. Solid-State Circuits 49, 2990–3004 (2014b)

Z. Lin, P.I. Mak, R.P. Martins, Ultra-Low-Power and Ultra-Low-Cost Short-Range Wireless Receivers in Nanoscale CMOS. Series of Analog Circuits and Signal Processing (ACSP) (Springer, Berlin, 2016)

A. Liscidini, M. Tedeschi, R. Castello, A 2.4GHz 3.6mW 0.35mm2 quadrature front-end RX for ZigBee and WPAN applications. ISSCC Dig. Tech. Papers (Feb. 2008), pp. 370–371

Y.-H. Liu, A. Ba, J. van den Heuvel et al., A 1.2 nJ/bit 2.4 GHz receiver with a sliding-IF phase-to-digital converter for wireless personal/body area networks. IEEE ISSCC Dig. Tech Papers (Feb. 2014), pp. 166–167

Y.-H. Liu, C. Bachmann, X. Wang et al., A 3.7mW-RX 4.4mW-TX fully integrated bluetooth low-energy/IEEE802.15.4/proprietray SoC with an ADPLL-based fast frequency offset compensation in 40 nm CMOS. ISSCC Dig. Tech. Papers (Feb. 2015), pp. 236–237

W.-H. Yu, H. Yi, P.-I. Mak, J. Yin, R.P. Martins, A 0.18 V 382 μW bluetooth low-energy (BLE) receiver with 1.33 nW sleep power for energy-harvesting applications in 28 nm CMOS, in IEEE ISSCC Dig., Tech Papers, 2017, to appear

P.-I. Mak, R.P. Martins, A 0.46-mm2 4-dB NF unified receiver front-end for full-band mobile TV in 65-nm CMOS. IEEE J. Solid-State Circuits 46, 1970–1984 (2011)

P.-I. Mak, R.P. Martins, High-/Mixed-Voltage Analog and RF Circuit Techniques for Nanoscale CMOS. Series of Analog Circuits and Signal Processing (ACSP) (Springer, Berlin, 2012)

J. Masuch, M. Delgado-Restituto, Ultra Low Power Transceiver for Wireless Body Area Networks, Series of Analog Circuits and Signal Processing (ACSP) (Springer, Berlin, 2013)

A. Paidimarri, N. Ickes, A. P. Chandrakasan, A +10 dBm 2.4 GHz transmitter with sub-400pW leakage and 43.7% system efficiency. ISSCC Dig. Tech. Papers (Feb. 2015), pp. 246–247

X. Peng, J. Yin, P.-I. Mak, W.-H. Yu, R.P. Martins, A 2.4-GHz ZigBee Transmitter using a function-reuse Class-F DCO-PA and an ADPLL Achieving 22.6% (14.5%) system efficiency at 6-dBm (0-dBm) Pout. IEEE J. Solid-State Circuits (2017), to appear

A. Pirola, A. Liscidini, R. Castello, Current-mode, WCDMA channel filter with in-band noise shaping. IEEE J. Solid-State Circuits 45, 1770–1780 (2010)

J. Prummel, M. Papamichail, M. Ancis et al., A 10 mW bluetooth low-energy transceiver with on-chip matching. ISSCC Dig. Tech. Papers (Feb. 2015), pp. 238–239

R. Rajan, Ultra-Low Power Short-Range Radio Transceiver (Microsemi Corporation, Aliso Viejo, CA, 2012)

B. Razavi, K.F. Lee, R.H. Yan, Design of high-speed, low-power frequency dividers and phase-locked loops in deep submicron CMOS. IEEE J. Solid-State Circuits 30, 101–109 (1995)

J.A. Stankovic, Research directions for the internet of things. IEEE Internet Things J. 1(1), 3–9 (2014)

M. Tedeschi, A. Liscidini, R. Castello, Low-power quadrature receivers for ZigBee (IEEE 802.15.4) applications. IEEE J. Solid-State Circuits 45, 1710–1719 (2010)

K. Wang, J. Koo, R. Ruby, B. Otis, A 1.8 mW PLL-free channelized 2.4 GHz ZigBee receiver utilizing fixed-LO temperature-compensated FBAR resonator. ISSCC Dig. Tech. Papers (Feb. 2014), pp. 21–22

J. Yin, P.-I. Mak, F. Maloberti, R.P. Martins, A time-interleaved ring-VCO with reduced 1/f3 phase noise corner, extended tuning range and inherent divided output. IEEE J. Solid-State Circuits 51, 2979–2991 (2016)

F. Zhang, K. Wang, J. Koo, Y. Miyahara, B. Otis, A 1.6 mW 300 mV supply 2.4 GHz receiver with –94 dBm sensitivity for energy-harvesting applications. ISSCC Dig. Tech. Papers (Feb. 2013), pp. 456–457

Acknowledgement

This research is funded by the Macau Science and Technology Development Fund (FDCT)—SKL Fund, and the University of Macau—MYRG2015-00040-FST.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer International Publishing AG

About this chapter

Cite this chapter

Mak, PI., Lin, Z., Martins, R.P. (2017). Circuit Techniques for IoT-Enabling Short-Range ULP Radios. In: Alioto, M. (eds) Enabling the Internet of Things. Springer, Cham. https://doi.org/10.1007/978-3-319-51482-6_14

Download citation

DOI: https://doi.org/10.1007/978-3-319-51482-6_14

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-51480-2

Online ISBN: 978-3-319-51482-6

eBook Packages: EngineeringEngineering (R0)