Abstract

This chapter presents two recent projects performed at ABB within the area of hybrid circuit breakers where mechanical contacts have been combined with semiconductor components to increase the performance. The first project includes a traditional parallel hybrid topology that is utilized in a medium voltage fault current limitation application in an AC-distribution network where the functionality has been proven in field during a 2-year long trial. The second project uses small scale semiconductor components in a resonant configuration to create a local zero-crossing and enable DC-interruption in a mechanical contact system.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

Keywords

- Hybrid DC circuit breaker

- Fault current limiting circuit breaker

- FLCB

- DC switch

- DC contactor

- Resonant circuit

1 Introduction

The hybrid circuit breakers considered in this chapter consist of a combination of mechanical and solid-state devices. The idea is to utilize each component where it has the maximal performance and to compensate for the other components’ shortcomings at the cost of increased complexity. For the hybrid topology to be competitive compared to both the solid-state circuit breaker and the mechanical circuit breaker, the combination must provide the possibility to reduce the requirements on both components compared to the alternative solutions.

2 PowerFul CB: A Hybrid Fault Current Limiting Circuit Breaker for AC Distribution Networks

Between 2017 and 2022, a project developing and testing a hybrid fault current limiting circuit breaker (FLCB) was running under the name PowerFul CB. The project is a collaboration between ABB and UK Power Networks, an electrical distribution network operator covering London, the South East, and East of England. The application as an FLCB is to limit and interrupt the current before the first peak in the event of a fault in an AC network to avoid reaching the system design limit. This technology can enable more generation to be added to the network and allows an increase in the prospective fault current, without requiring costly upgrades to the substations and their switchgear.

Even though this project has its application in an AC distribution network, the task of limiting and interrupting the rising current before its first peak is very similar to interrupting a rising fault current in a DC system. During the project, a device has been developed and implemented in a pilot installation. The device was tested according to applicable parts of the standards and additional project-specific features to be qualified and allowed for installation in the electric distribution network of London in the UK. After testing, installation, and commissioning, the pilot device has successfully proven its capabilities in the network during a 2-year long trial period.

Limitation of fault currents in AC distribution systems is out of the scope of this book, so the application will not be described in detail here. More information about the application can be found in the detailed project description [1]. Considering the shortage of MVDC systems where circuit breakers can be tested under real conditions, this project provides an important contribution to the proof of concept of hybrid DC circuit breakers’ capabilities and to build confidence in the technology. The hybrid topology is very suitable to limit and interrupt fast rising currents also in an MVDC network, and the pilot device described here can be used in such an application without adaptation.

Requirements of the FLCB

One major challenge when developing new technologies is to define relevant design parameters. As this project was initiated from a clearly defined application within the MV distribution network, the requirements were rather well-defined. However, from a product point of view, with market analysis and cost-benefit analysis, there is a desire to reach a larger market. Further, other parameters such as space requirements and availability are added to the technical specifications. Therefore, the design values for the device were agreed according to Table 10.1. The voltage level in the trial site is 11 kV, and the current differs depending on the running arrangement of the FLCB.

Topology and Design Considerations

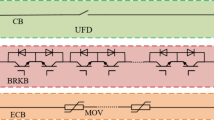

In its simplest form, the mechanical-solid-state hybrid circuit breaker consists of three parallel components: a mechanical switch, a power semiconductor, and a metal oxide varistor as shown in Fig. 10.1.

The actual current limitation and energy absorption is, as in most DC circuit breaker topologies, performed by a metal oxide varistor. Its non-linear resistive behavior is utilized both to limit the voltage across the other components and to absorb the magnetic energy stored in the system, forcing the current down to zero.

The purpose of the other two components can be viewed in two different ways. Most commonly, the hybrid circuit breaker is considered as a solid-state circuit breaker, where the power semiconductor is used as the main interruption means, but due to the high conduction losses, it is bypassed by a mechanical switch during normal operation to fulfill specifications on cooling or energy efficiency. However, it can also be viewed from another perspective: a power semiconductor is introduced to aid in the current interruption and relax the demands on the mechanical device. Interrupting and limiting direct currents at higher voltages is challenging for a traditional mechanical circuit breaker as the demands on arc voltage and speed of operation are high. When the interruption is performed by a power semiconductor, the requirement on the mechanical switch is changed from current interruption capability to a capability of commutating the current into the semiconductor. The arc voltage only has to be high enough to push the current through the parasitic inductance between the mechanical switch and the power semiconductor. Thus, the mechanical switch can be made lighter and hence naturally faster.

The implementation of the PowerFul CB can be seen in Fig. 10.2. To increase the reliability, the FLCB is built up of four series connected modules, each consisting of the three parallel branches. The components are chosen such that three modules are enough to handle the system voltage to limit and interrupt the current. By including a fourth module in series, a redundancy is introduced so that the trial device can accept one failure in any of the component and still manage the interruption. This redundancy significantly increases the reliability of the device to meet the high requirements of power availability in the distribution network.

To decrease cost and development time, and increase the confidence in the pilot device, many of the components used in the FLCB are existing products. The semiconductors are high power BiGTs, the surge arresters are off the shelf products, while the mechanical commutation switches are specifically developed for the project.

Operation Principle

Figure 10.3 shows the current and voltage during interruption of a rising current by the hybrid circuit breaker in a test of a single module. When a low impedance fault is applied to the system around t = −0.4 milliseconds, the current starts to rise rapidly in the mechanical switch (fast commutation switch, FCS) as shown in yellow. At t = 0 the circuit breaker is tripped, and a command is sent to open the mechanical switch. Due to the mechanics, there is a delay before the contacts of the mechanical switch separate, here around t = 0.4 milliseconds, and an electrical arc is formed between the contacts. As the arc voltage is higher than the voltage drop across the semiconductors, the arc voltage commutates the current into the parallel branch containing the power semiconductors (here BiGT). It is desired that the loop between the parallel branches is small to facilitate a fast commutation to minimize the arcing time. Once the current has commutated fully, the arc ceases. The current, shown in purple, is now allowed to flow through the semiconductors as the mechanical switch continues to open and regain insulation strength between the contacts. Once the mechanical switch has opened enough, the semiconductors are turned off at t = 0.7 milliseconds, forcing the current into the third branch containing the metal oxide varistor. The voltage across the device rises up to the conduction level of the surge arrester, and as this is higher than the system voltage, the current starts to decrease. Once the current reaches zero, the voltage across the hybrid circuit breaker is equal to the system voltage, and only a small residual current flows through the surge arrester.

Testing

Development tests have been performed on all components during the design phase, and qualifying tests on the FLCB for installation in the network have been carried out. As far as possible, the FLCB was tested according to the AC circuit breaker standard IEC 62271-100 in line with the qualification of all other equipment in the system. However, some features of the FLCB, like the current limitation capability, are not applicable to standard circuit breakers and had to be verified specifically for the FLCB. Table 10.2 summarizes some of the tests performed according to the standard and some of the additional tests performed on the FLCB in agreement with UK Power Networks.

Figure 10.4 shows the current and voltage waveforms in one phase when interrupting a short-circuit current during the qualification type-test. At the time t = 0, the circuit is closed by an external switch, and a current with a prospective amplitude of 25 kA rms starts to rise. The prospective fault current is shown in a dashed red line, and it is slightly asymmetric reaching above 50 kA on the positive peak. At a level of 4 kA instantaneous current, the fault is detected by the FLCB control system, and the FLCB operation is triggered. The blue curve shows the actual current that flows through the FLCB. It is limited within a millisecond and reaches a peak below 13 kA before it decays down to zero. The voltage across the FLCB is shown by the black curve. Due to the low resistance of the mechanical switches, the voltage across the FLCB is low, typically less than 1 Volt, during the rise of the fault current. Once the FLCB has operated, the decaying current is conducted by the metal oxide varistors that limit the voltage, and due to their non-linear characteristics, the voltage across the FLCB is kept almost constant around 15 kV during the decay. When the current reaches zero, the FLCB blocks further current from flowing, and the voltage across it follows the sinusoidal system voltage.

A Close-Open test was performed during the type-test and is shown in Fig. 10.5. The system voltage, shown in black, is applied across the FLCB, and the FLCB is closed by turning on the BiGTs at the time t = 0. The blue curve shows that the current starts to rise rapidly due to the low impedance of the circuit. As in the previous test, the fault is detected, and the FLCB is tripped when the current passes 4 kA. At this point, the current through the FLCB is carried solely by the semiconductors, and the mechanical switches are still open. Hence, the FLCB acts as a solid-state circuit breaker, and the current is interrupted within microseconds. A transient over-voltage from the metal oxide varistors is seen in the voltage during the decay of the current before the current reaches zero, and the voltage across the FLCB returns to follow the system voltage.

Field Experience

The FLCB pilot device was installed in the electricity distribution network of London during a 2-year long trial period to confirm its long-term performance. Most of the time, it was connected as a bus-coupler, tying two busbars in the substation together to increase the redundancy and reliability of the network. It was also tested in another network configuration where it carried the full load current from one of the feeding transformers. Both configurations render similar fault current shapes and are very similar to applications as a circuit breaker or bus-tie in a DC-system.

Figure 10.6 shows an example of a fault current that was detected, limited, and interrupted during the trial. Before the fault occurs, symmetrical load currents in all three phases flow through the mechanical switches of the FLCB. Close to the negative peak of the load current, a single phase to ground fault occurs in phase L1, shown in blue. Since the power factor is rather close to 1, the phase to ground voltage is also close to its maximum resulting in an almost linear rise of the fault current. The rate of rise of the fault current is determined by the system voltage and network impedance, but also by the impedance of the fault, i.e., both the location and impedance of the fault itself. In this case the rate of rise can be estimated to 1.8 kA/ms, which is rather low compared to the initial rate of rise of 11 kA/ms for a 25 kA symmetric fault that the FLCB is designed for. Once the current crosses 4 kA, the FLCB control system detects it as a fault current and trips the FLCB. During the FLCB operation, the current keeps rising almost unaffectedly, and 0.7 ms after the trip, the semiconductors are turned off and the current is limited. The decay of the current to zero depends on the phase angle of the voltage, and the system configuration and loading. Within a few milliseconds, the current through the FLCB reaches zero.

When a fault occurs close to peak voltage, considering a mainly inductive circuit, the fault current is symmetric around zero. This means the prospective peak current is lower than for an asymmetric fault, where the fault occurs close to the voltage zero-crossing. However, the symmetric fault current provides the highest rate of rise of the fault current, and since the FLCB acts and limits the current on the rising edge, the resulting limited peak current is higher for the symmetrical fault than for the asymmetrical fault. For a simple DC-system that consists of a 6-pulse rectified AC voltage source, and neglecting the contributions from any smoothing capacitors, the rise of the fault current is very similar to the symmetrical fault current in the AC-network [2].

During the trial, the FLCB has proven its capabilities of current interruption on the rising edge and to limit the fault current within 0.7 milliseconds after fault detection. The peak current could be further decreased by decreasing the tripping level of the FLCB, but this level is always a trade-off between low peak current and avoiding unnecessary tripping. During the trial, several faults with lower amplitude have also occurred where the FLCB did not trip as the fault current did not reach the trip level. This ability is easily forgotten but is an important part of the selectivity and discrimination schemes of the protection in the electrical power system.

Scaling

For low voltage DC applications, the parallel hybrid topology is often considered too expensive. Partly because the market is very cost-driven so that full scale power semiconductors become unreasonably expensive, but also because that mechanical circuit breaker technology is more feasible due to the lower system voltage.

For high voltage DC applications, the hybrid topology becomes rather expensive since many semiconductors are required in series to handle the system voltage. Further, the voltage drop across these components becomes high, increasing the requirements on the arc voltage of the mechanical commutation switch. One possible solution to this is to split the mechanical switch into two components: a load commutation switch and an ultrafast disconnector [3].

The parallel hybrid topology is well suited for medium voltage DC applications. There are power semiconductors available in suitable voltage ranges, the required commutation voltage is manageable, and the voltage level gives reasonable dimensions for the mechanical switches.

Summary

In the PowerFul CB project, a hybrid fault current limiting circuit breaker has been developed, tested, and demonstrated in field. During a 2-year long trial in an 11 kV electric power distribution network, the device has proven its capability to limit and interrupt fast rising fault currents in a real environment. Since the topology of the FLCB is identical to a hybrid DC circuit breaker, the project and the successful trial also contributes to the proof of concept and long-term development of future hybrid DC circuit breakers.

3 A Novel Low Voltage Hybrid DC Switch Using Resonant Current Injection

In this part, a novel concept of a low voltage DC switch is reported based on a resonant current injection technique. Instead of pre-charging a resonant capacitor prior to each operation, the main feature of this design is that the arc voltage across the contacts is utilized to charge the capacitor. Thyristor groups are used to control the charging and the discharging of the resonant capacitor in appropriate polarities. This concept presents a low-cost design with shorter breaking time than a conventional DC switch. A prototype of a DC switch based on the proposed concept was built and tested in the ABB Corporate Research Center in Västerås, Sweden, during the years 2014–2017. The concept, the design, and the tests presented here have been carried out by Zichi Zhang, Stefan Valdemarsson, and Erik Johansson.

Introduction

Conventional low voltage DC switches often connect all three or four poles of an AC switch in series, to create an arc voltage high enough to overcome the system voltage and force the current to zero. However, it is challenging for conventional DC switches to interrupt direct current at higher voltage ratings than 1 kV. Combined in one device, many splitter plates are required to be piled up to generate a high enough arc voltage. Hence, the dimensions of the switches become very bulky and costly. Another way to break a direct current is to generate an injection current from a pre-charged capacitor, creating a local current zero crossing in the switch [4]. Unfortunately, the market for low voltage switches is cost sensitive, and the cost of such a solution for a low voltage DC switch is generally too high. Pure solid-state devices are even more expensive, and losses need to be handled with active cooling, especially when the maximum continuous current is higher than 1 kA.

Hybrid switches have been a recent trend as they combine the advantages of conventional mechanical devices (passive cooling, overload abilities, etc.) and solid-state devices (fast interruption, controllability). At low voltage, ABB launched the world’s first low voltage molded-case hybrid switch in 2014 [5]. Further, Eaton has released a hybrid DC contactor up to 1000 VDC [6]. Among these low voltage hybrid switches, the solid-state parts are used to break the nominal current lower than 1 kA. For higher currents, these hybrid switches still rely on conventional arc chamber technology to break the current, due to the high cost of solid-state parts for higher currents.

This novel concept of a low voltage DC switch is classified as a hybrid switch containing both mechanical devices and semiconductors, but it is not the solid-state device that interrupts the current. Instead, it is based on current injection to create a local zero-crossing of the arc current. However, unlike a traditional resonant circuit breaker topology like the one described in [4], the proposed design doesn’t need to pre-charge the resonant capacitor. Instead, the semiconductors use the arc voltage to build up a high enough voltage across the capacitor to create the desired zero-crossing of the arc current. The most distinctive features of the novel design are the fast current interruption, and the relatively low cost of the power electronic components.

Basic Principle

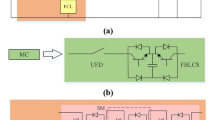

The diagram of the proposed DC switch is shown in Fig. 10.7. This hybrid switch conducts current and provides current interruption capabilities in both directions. It consists of two groups of thyristors, a resonant circuit with a capacitor and an inductor, a surge arrester (MOV) and a mechanical switch, here represented by two moving electrical contacts in series. The surge arrester provides counter overvoltage to interrupt current in the circuit, transforming the magnetic energy stored in the external system inductance into heat. The mechanical switch can be of single contact or dual contact design. In the case of dual contact design, the current injection parts and the surge arrester are parallel to only one electrical contact while the other contact can be seen as a disconnector.

Once the arc voltage across the contacts of the switch is detected, thyristor T1 is fired. The capacitor is charged by the arc voltage across the contact on the left; see Fig. 10.8. T1 switches off automatically once the injection current reaches zero, and the capacitor is fully charged.

Once the blocking state of T1 is checked, the thyristor T2 is fired to let the resonant capacitor discharge and change polarity at the end of this discharge half-period, according to Fig. 10.9. By repeating the described process of firing T1 and T2, a series of progressively larger resonant injection currents are generated. When the injection current reaches the amplitude of the load current, a local current zero crossing is created at the contact gap on the left, and the electrical arc can be successfully extinguished.

The thyristors are placed in pairs, coupled in antiparallel to be able to react similarly for both current directions. It is enough to fire both thyristors in the same group together as the arc voltage (positive or negative) will determine which one will conduct.

Once the arc is interrupted, the main current charges the resonant capacitor until the operation voltage level of the surge arrester is reached, as shown in Fig. 10.10. At that time, the current commutates to the surge arrester and eventually reaches zero after a time depending on the overvoltage formed by the surge arrester and the external inductance in the circuit; see Fig. 10.11.

The arc might restrike if the transient recovery voltage between the contact gap is larger than the voltage withstand strength (between contacts on the left in the figures). In this case, T2 should be fired again to change the polarity of the resonant capacitor. The same procedure of firing T1 and T2 goes on till the current is properly interrupted. The dual contact design can provide the disconnection function for this hybrid switch so that no external mechanical disconnector is required between the load and the source.

The current interruption process is summarized in Fig. 10.12 in terms of injection current i1, discharge current i2, DC main current Idc, and voltage across this DC switch. After contact separation, an arc is detected by an arc voltage across the device, and T1 and T2 are fired following a defined time sequence. After the second pulse of i1 in the illustration, the injection current reaches an amplitude to interrupt the current in the contact gap. The main current Idc charges the capacitor, and the contact voltage increases until an arc is reignited in the contact gap. The current injection process starts again to eventually interrupt the arc current a second time. The current Idc charges the capacitor until the gap voltage across the switch reaches the operating voltage of the surge arrester. The surge arrester clamping voltage is chosen higher than the system voltage to create an overvoltage which limits and eventually interrupts the current Idc in the circuit.

Simulation Results

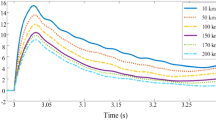

A PSCAD simulation model was built to study the feasibility of the concept and evaluate the important parameters for a successful interruption. A simulation result is shown in Fig. 10.13. The simulation uses the current to interrupt 1 kA, with a system voltage of 1 kV, the resonant capacitor 60 μF, the resonant inductor 5 μH, and the arc voltage 55 V. The switch opens at 0.049 s and the arc immediately exhibits a constant 55 V. The current injection is initiated 1 ms after the contact separation. The amplitude of the positive current injection pulses increases each time, and the current zero crossing is reached at the fourth positive pulse. The current I_total charges the capacitor and the contact voltage U_total increases up to the clamping voltage of the surge arrester, around 1.3 kV. The surge arrester operates and the current in the circuit i_total drops to zero at 0.053 s.

Design Considerations

The electronic and the control unit needs power. To avoid extra equipment to be connected to the device and relying on an external power supply, a self-powered supply is configured to accept the arc voltage over the electrical contacts as its source and deliver a stable 5 V TTL level. This voltage powers a microcontroller which generates the sequence of control pulses to fire the thyristors T1 and T2. As soon as an arc voltage is detected, the power supply needs to be turned ON and stabilized, which means that a waiting time is required before being able to start the T1 and T2 firing sequence. The minimum dead time is estimated to be 1 ms between the contact separation and the first T1 firing, but to guarantee a sufficient margin, the deadtime is set to 2 ms.

Furthermore, the control system checks if the thyristor T1 is indeed in blocking mode, before firing T2. The sequence then continues until a stop condition is fulfilled. Those conditions are timeout, no voltage supply available, or information output that the gap voltage is above a high voltage threshold indicating that the interruption has been successful. If a restrike occurs, the control unit receives the information of HV failure. The microcontroller can react by restarting the pumping sequence by firing T2 first this time; see Fig. 10.12. More information is available in [7].

A special arc chute has been designed to face the challenges of interruption of such currents with electrical contacts in air. It is placed in the vicinity of the electrical contact on the left in the Figs. 10.7–10.11. A novel design of splitter plates has been proposed to improve the re-ignition voltage withstand, the arc resistance and the current interruption, compared to the arc chute used in standard AC switching devices (steel plates as standard). It is especially necessary for high current interruption that the arc enters in the arc chute to provide enough arc voltage to inject high enough current per pumping cycle and interrupt faster, thus reducing the arcing time. If the current interruption is faster, it is less likely to have an arc restrike because long arcing time degrades the strength of the recovery voltage withstand of the open gap contact. Furthermore, the electrical endurance is improved by reducing the arcing (erosion) time. The novel design combines steel splitter plates with laminated brass layers on top and bottom surfaces. Steel provides magnetic forces to attract the electrical arc from the contacts into the arc chute whereas brass brings high re-ignition voltage withstand and arc resistance. More information is available in [8].

Experimental Results

A prototype of the described switch was built to verify the concept at ABB Corporate Research in Västerås, Sweden. A series of tests have been performed at different current and voltage levels. One of the test results is shown in Fig. 10.14 to illustrate the efficiency of the concept. The device is made with a single arc chute of 7 laminated splitter plates to interrupt the arc current and limit the probability of reignition.

The current in the circuit at this specific test is 2000 A and the system voltage around 1650 V. Once the arc starts, the current in the circuit drops a bit due to the arc voltage, limiting the current. The current injection process starts 2 ms after contact separation. The current injection pulses increase stepwise until reaching the main current amplitude at 0.168 s, creating the conditions for a successful arc current interruption. The contact gap voltage reaches the operating voltage level of the surge arrester, and the main current in the circuit is commutated into the surge arrester. The current in the circuit is eventually interrupted after time 0.1705 s. The time to interrupt the current by the surge arrester depends on the time constant of the circuit, the surge arrester clamping voltage, and the system voltage.

Summary

The hybrid DC switch uses the arc voltage to start an oscillation of an injection current. The injection current pulses increase stepwise until a local current zero crossing is created. The costs of this device are greatly reduced because low-cost thyristors can be used, compared to equivalent conventional hybrid devices. The complexity of having a pre-charged capacitor to inject a counter current and create a local current zero crossing is avoided. Furthermore, the current interruption of this design has been shown to be faster than a traditional DC switch with only splitter plates as means for interruption, and this prototype is even potentially more compact than a traditional equivalent device. The simulations and the experiments demonstrate the feasibility of this low voltage hybrid DC switch design to break DC load current up to 2000 A.

4 Conclusions

This chapter has presented two recent projects with hybrid DC circuit breakers performed at ABB. The concepts are very different in their topologies, but both utilize a combination of semiconductors and mechanical contacts to maximize the performance. The hybrid technology has its most obvious advantages in the medium voltage range where the semiconductors decrease the demand on the mechanical contact’s arcing voltage without requiring excessive number of components in series to handle the voltage level. However, it has also been shown that different hybrid topologies can be used to facilitate efficient switching both for lower and higher voltage systems.

In addition to the two projects presented here, ABB has also been active in research on other DC switching technologies, including solid-state, resonant, and pure mechanical. The different technologies have both benefits and drawbacks meaning there is no optimal DC circuit breaker topology for all applications. The choice of technology and topology should therefore always be based on the requirements of the application, and optimized considering both performance, cost, and complexity.

References

UK Power Networks innovation, PowerFul CB project webpage, [Online]. Available: https://innovation.ukpowernetworks.co.uk/projects/powerful-cb/

J. Magnusson, A. Bissal, G. Engdahl, J.A. Martinez-Velasco, Design Aspects of a Medium Voltage Hybrid DC Breaker (IEEE PES Innovative Smart Grid Technologies, Europe, 2014)

M. Callavik, A. Blomberg, J. Häfner, B. Jacobson, The hybrid HVDC breaker: An innovation breakthrough enabling reliable HVDC grids, ABB Grid Systems, Technical Paper, Nov 2012

L. Liljestrand, M. Backman, L. Jonsson, M. Riva, E. Dullni, Medium Voltage DC vacuum circuit breaker. 3rd international conference on electric power equipment - switching technology (ICEPE-ST), Busan, Korea, Oct 2015

ABB, ABB launches first low voltage moulded-case hybrid switch, [Online]. Available: https://new.abb.com/low-voltage/products/circuit-breakers/highligths/news/abb-launches-first-low-voltage-moulded-case-hybrid-switch

Eaton, Maintenance-Free. Reliable. Cost-Effective. High DC switching made simple. DC contactors in current range 300 A and 600 A [Online]. Available: https://www.eaton.eu/ecm/groups/public/@pub/@europe/@electrical/documents/content/pct_1845518.pdf

M. Pathmanathan, G. Zanuso, Z. Zhang, S. Valdemarsson, E. Johansson, Self-powered supply and control system for hybrid semiconductor DC switch. EPE 2018 ECCE Europe, Riga, Latvia, Sept 2018

Z. Zhang, S. Valdemarsson, E. Johansson, G. Johansson, T. Gentzell, Novel DC arc chute design using laminated splitter plates. 22nd International conference on gas discharge and applications, Serbia, Novi Sad, Sept 2018

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 This is a U.S. government work and not under copyright protection in the U.S.; foreign copyright protection may apply

About this chapter

Cite this chapter

Magnusson, J., Schaeffer, D. (2023). ABB’s Recent Advances on Hybrid DC Circuit Breakers. In: Kizilyalli, I.C., Shen, Z.J., Cunningham, D.W. (eds) Direct Current Fault Protection. Power Systems. Springer, Cham. https://doi.org/10.1007/978-3-031-26572-3_10

Download citation

DOI: https://doi.org/10.1007/978-3-031-26572-3_10

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-26571-6

Online ISBN: 978-3-031-26572-3

eBook Packages: EnergyEnergy (R0)