Abstract

Energy meters are usually directly floating on the live wire due to the direct current sensing (e.g. shunt resistors) and/or voltage sensing (resistance dividers). For safety’s viewpoint, the meters have to be isolated to protect human beings from 220 V power line. The isolation is usually accomplished by opto-couplers. There are two ways of isolations. One is to isolate the whole meter by floating the metering chip and MCU (Micro Control Unit) on the live wire and using opto-couplers to interface with communication modules and/or socket of IC (Intelligent Card) cards. The other is use opto-couplers to isolate the metering chips and the MCU such that the MCU is not floating on the live wire but share the ground with communication modules and/or socket of IC cards. There are pros and cons of each method. For the latter method, the MCU and energy metering chip must be powered in different domain, as energy meter chip must connect directly to power line. The following figure shows the block diagrams of single-phase meter and poly-phase metering having different power domain. In this kind of meters, the MCU and metering chip have to be in different power domain, and opto-couplers are inserted between MCU and meter chip for communication.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

1 Introduction

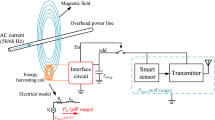

Energy meters are usually directly floating on the live wire due to the direct current sensing (e.g. shunt resistors) and/or voltage sensing (resistance dividers). For safety’s viewpoint, the meters have to be isolated to protect human beings from 220 V power line. The isolation is usually accomplished by opto-couplers. There are two ways of isolations. One is to isolate the whole meter by floating the metering chip and MCU (Micro Control Unit) on the live wire and using opto-couplers to interface with communication modules and/or socket of IC (Intelligent Card) cards. The other is use opto-couplers to isolate the metering chips and the MCU such that the MCU is not floating on the live wire but share the ground with communication modules and/or socket of IC cards. There are pros and cons of each method. For the latter method, the MCU and energy meter chip must be powered in different domain, as energy metering chip must connect directly to power line. The following figure shows the block diagrams of single-phase meter and poly-phase metering having different power domain. In this kind of meters, the MCU and meter chip have to be in different power domain, and opto-couplers are inserted between MCU and metering chip for communication (Figs. 1 and 2).

In the application that needs isolation between metering chip and MCU, every metering chip is powered independently. There are typically two kinds of power supply circuits. Power transformer (PT) based power supply and capacitor-divider network based power supply as shown in the following figures (Figs. 3 and 4).

Compared to the PT based power supply, the capacitor-divider network based power supply has weaker driving capacity but better reliability, such as electromagnetic compatibility performance. And more over, the capacitor-divider network based power supply is a more cost-efficient way.

In the capacitor-divider network based power supply, the capacitance of C6 is key to the driving capacity and reliability. The bigger the capacitance of C6, the more driving capability the power supply has but the worse reliability. Apparently using smaller capacitor offers better reliability and lower cost. But it calls for ultra-low power metering chips. Most low power energy metering chips consume a current north of 3 mA, too high for reliable capacitance-divider based power supply scheme. The current dissipation of the metering chip has to be at least halved.

In this chapter a low power single phase energy metering chip is introduced. It consists of three low power ADCs (Analog-Digital-Converter) to convert analog signals to digital domain, a energy metering application specific hardwired DSP (Digital Signal Processor) to process such signals, a system control module to manage power modes, and a UART (Universal Asynchronous Receiver/Transmitter) based peripheral for communication. The chip consumes only 1.5 mA at full-function meter mode, and 13 μA average power for current detection in anti-tempering mode. This chip is currently in production.

Low power consumption is realized in the following aspects:

-

Low power metering modes design

-

Low power metering algorithm design

-

Low power DSP architecture design

-

Low power circuits design

-

Low power clock network design

2 Architecture of Energy Metering Chip

2.1 Overall Diagram

The overall diagram is shown in the following figure. The energy metering chip is divided into five major blocks.

-

Analog unit (AFE)

-

DSP unit (DSP)

-

Communication unit (COMM)

-

System management unit (SYS)

-

Storage unit (MEM) (Fig. 5)

2.2 Analog Unit

The block diagram of the analog unit is show in the following figure (Fig. 6).

Three high precision sigma-delta ADCs are integrated into energy metering chip. One is used to convert the voltage signal, one is used to convert the current signal, and one is used to convert a multi-function signal such as temperature, internal/external DC signals. The ADCs can sample at 800 or 200 KHz, for higher precision or lower power consumption respectively. To further improve the noise performance, low noise amplifiers precede the ADCs.

There are three clock generators within the analog unit. One uses external crystal input to generate precise 3.2768 MHz clock. The other two clock generators use internal resistance and capacitors (RC) to generate 3.2 MHz/32 KHz clock signals. All the clock signals are managed by the system.

The analog unit also has a power management block. The ultra low power low drop linear regulator (LDO) generates 1.8 V power supply for digital circuits. It only dissipated 2-uA standby current. 3.3 V power input is used as supply for IO and analog unit. A POR (Power on Reset) and power down detection circuit is integrated in the power management unit. The band-gap circuit provides a 1.2 V reference voltage with a typical temperature drift of 10 ppm/℃. The temperature sensor makes it possible to calibrate the reference for a higher energy metering precision.

2.3 DSP Unit

The DSP is specifically design for power metering applications. Instruction set, register file, ALU (Arithmetic-Logic Unit) and bus architecture are all dedicatedly designed for power metering algorithm and for low power consumption. The DSP samples the data from ADC and provides power/ energy, RMS (Root Mean Square) values, frequency of voltage signal (Fig. 7).

2.4 Communication Unit

Communication unit maintain a protocol based on a two-wire low speed UART transaction. Through this interface, the MCU on the energy meter can configure the chip and retrieve data from the chip. The RX-pin of the interface also serves as wake-up and reset pin, which can save MCU IO (Input Output) resource and reduce BOM (Bill of Material) cost (Fig. 8).

2.5 System Management Unit

System management unit maintains the function mode of the chip to achieve low power applications. It works on a 32 KHz clock and consumes very little power (Fig. 9).

2.6 Storage Unit

Storage unit consists of a SRAM (Static Random Access Memory) and some registers. The SRAM is the data memory to realize DSP algorithm and the register stores the configuration information for all other parts of the chip.

3 Low Power Design and Consideration

Low power design is considered at the following levels:

-

Low power metering modes design

-

Low power metering algorithm design

-

Low power DSP architecture design

-

Low power clock network design

-

Low power circuits design

3.1 Metering Modes Design

The energy metering chip samples signals of voltage and current, and provide following information:

-

Signal waveform data, including original data, AC (Alternating Current) components and DC (Direct Current) component

-

RMS value of the signal

-

Active power and re-active power of voltage/current signals

-

Energy of active/re-active power

-

All above-mentioned information for fundamental (50/60 Hz) component of voltage/current signals

-

Frequency of fundamental component of the voltage signal

The clock frequency and function of chip can be configured as different metering mode to realize different power consumption (Fig. 10).

3.1.1 Full Function, Full Precision Mode

In the full function/full precision mode, the chip works at full speed and provides all possible information at highest precision. In this mode, the chip consumes a maximal current of 1.5 mA. This mode is used when the energy meter is well powered and needs the highest metering precision.

3.1.2 Full Function, Less precision Mode

The full function/less precision mode is used in low power/low cost application where precision is not the highest priority. In this mode, the sampling rate and the working current of the ADC is cut down to save power consumption, while the DSP functions are all enabled to provide all possible information. In this mode about 1.3-mA current is consumed by the chip.

3.1.3 Less Function, Full Precision Mode

The less function/full precision mode is used in low power/low cost application where not all functions are necessary. In this mode, some of the DSP functions are disabled to save power, but basic energy metering information such as power/RMS are provided. In this mode about 1-mA current is consumed by the chip.

3.1.4 Anti-Tampering Mode

A typical tampering method is to cut the voltage input of the energy meter to make the chip see a voltage of 0 V. In this case, the chip still can see a current signal. Since power equals to voltage multiplied by current, the chip meters the power of zero. To avoid this, the chip needs to use RMS of the current signal as a virtual power and provide this power information. As voltage signal is cut to zero, the energy meter cannot get power from voltage signal. The energy meter can either get power supply from battery or from an inductor coil. To extend the battery life or to save the cost of the inductor coil, low power consumption is necessary in this case. In this case, the voltage ADC and the multi-function ADC are shut down; the sampling rate and the working current of the current ADC is cut down; the DSP function is reduces to only provide RMS of current signal; the power consumption of energy metering chip is reduced to about 400 μA.

3.1.5 Sleep Mode

When there is no voltage signal or current signal, the chip can go to sleep mode, in which all data are kept in SRAM and registers. All ADC is shut down and DSP is stopped but the LDO and lower frequency clock as well as the system monitoring circuits are still working. In this mode, the chip only consumes about 4.5 μA.

3.1.6 Current Detecting Mode

In the anti-tampering mode, the current signal can be 0. If the energy meter is working in full speed with the power supply from the battery, it will use up the battery in a couple of days. To avoid this, current detecting mode is introduced. Under current detecting mode, the chip is waken up periodically and works for a short period of time to monitor the original waveform of the fundamental signal. If the value of the waveform crosses the pre-set threshold, the chip will switch to anti-tampering mode, otherwise it will sleep again. In the current detecting mode, the chip only consumes around 13 ~ 850 μA, depending on how often the chip wakes up to monitor the current (Fig. 11).

3.2 Metering Algorithm Design

A low power metering algorithm means the algorithm consumes as little horse power of DSP as possible. Here are some principles for low power algorithm design:

-

Use multi-rate design [1]

-

Use shift/ add instead of multiply

-

Tradeoff in filter design

-

Use fix-point than floating-point design

3.2.1 Multi-Rate Processing

Sigma-delta ADC needs a CIC (Cascaded Integrator-Comb) filter to filter out high frequency noise. CIC filter is a typical multi-rate processing, which consists of an integrator and a differentiator. The integrator operates at ADC’s sampling rate of 819.2 KHz. With a down-sampling factor of 64, the differentiator works on a much lower frequency of 12.8 KHz. Through the CIC filter, the data rate is reduced by 64 times.

Half-band-filter is another down-sampling filter that reduces the data rate by two.

In metering algorithms, there are a lot of processes to extract DC/AC part of signals through high-pass/ low-pass filters. In the metering application, the components of signals are DC@0 Hz, fundamental@50 Hz (or 60 Hz), harmonic@100/150/200 Hz, etc. In this case, CIC filter is a ideal candidate to realize high-pass/low-pass filters, which makes the whole metering algorithm work in a multi-rate manner (Fig. 12).

3.2.2 Multiplication Replacement

Multiplication is frequently used in filter design. But multiplication is much more complex than adder or shifter in circuit design and consumes more power. In a low power design, we must reduce the usage of multiplication and use adder/ shifter instead. The following are two examples.

In different energy meter applications, we need to adjust the AC amplitude of input signals. In this case, we can use X2,/2, X4,/4, X8,/8 to realize a rough adjustment, which need only shift operation. And a fine adjustment can be realized in calibration, which need multiplication. As we discussed in the previous section, the calibration functions are at a very low frequency.

In metering algorithms, operation that in the form of “Y = A × X” cannot be avoided. But we can carefully design the factor A to avoid usage of multiplication. For instance, if A is 0.57, we can adjust it to 0.5625, which is 9/16, “9/16X” equals to “1/2X + 1/16X” (Fig. 13).

3.2.3 Trade off in Filter Design

In low power energy metering applications, metering performance and power consumption must be balanced carefully. Extreme metering performance is never the only design goal. To meet low power requirement, we must use the simplest filter that can meet the metering requirement.

For example, a 90-degree phase needs to be inserted between voltage and current signals to calculate reactive power. There are two typical filters that can realize such requirement. Differentiator filter and Hilbert filter. The differentiator filter is very simple, but the amplitude-frequency response is not as flatten as Hilbert filter. But in current energy metering applications, the required precision of reactive power is much lower than the one of active power. So we can implement differentiator filter in the energy metering algorithm for lower power consumption.

3.2.4 Fix Point Implementation

The required dynamic range of current in a energy meter is typically 1000:1 with a accuracy of about 1 ‰. This leads to a minimal bit width of 21 bits. Considering noise, input signal and internal feed-back filter implementation, a 32bit fix point algorithm is enough to meet the accuracy and dynamic range requirement. A lot of CIC filters are used in the algorithm, they are very fix-point-friendly filters.

3.2.5 Low Power DSP Architecture Design

A specifically optimized DSP architecture is designed for low power energy meter algorithm implementation. Its diagram is shown in the following figure (Fig. 14).

Every clock cycle, DSP fetch an instruction through the instruction bus (I-bus) interface and send it to the decoder module. The DSP controls the register file to realize data access through the data bus (D-bus) interface or ALU operations in ALU module.

The DSP works in a 2-stage pipeline, instruction fetch and instruction execute as shown in the following figure. If there is a branch instruction, a delay slot must be added after the branch instruction to be executed. A delay slot can be any instruction, if no instruction is needed to be executed, a NOP can be inserted (Fig. 15).

3.2.6 Register File

The register file is shown in the following figure (Fig. 16).

Only two 64-bit registers RegA/RegB and one 1-bit register RegC are integrated into the register file. The two 64-bit registers are used as the source and destination for ALU and can realize data load/store from and to the memory. Most operations in the algorithm are of 32 bits, but CIC filter sometimes need more than 32 bits. That’s why we need 64-bit RegA and RegB. The 1-bit register is used as branch condition flag.

3.2.7 ALU

ALU unit processes data from RegA and RegB and send result back to RegA as shown in the following figure (Fig. 17).

Through profiling the metering algorithm, we design the ALU with following features to be the most suitable module.

The ALU can realize complex add/sub in 64-bit manner. Such an add/sub unit is combined with additional shift and anti-saturation options. As we discussed in the previous sections, to reduce power consumption, the metering algorithm majorly consists of add and shift operation. And to avoid saturation in the filters, anti-saturation operation is necessary for output and every feedback nodes of the filter. A complex add/sub unit can realize those three operation in a single clock as shown in the following figure. This reduces the clock frequency of the DSP and the number of register operation (Fig. 18).

The ALU can realize multiplication and square root in a slower manner. At 3,200 Hz rate-level, only several multiplications operations are needed for power and RMS calculation. Other multiplication operations for calibration and so on are executed at 50 or 12.5 Hz rate-level. In the case of square root, the operation is only at 50 Hz. To reduce power consumptions, the multiplication unit is designed as a 32 × 32bit multiplication generating a 64-bit result in 32 clock cycles. To balance the area and accuracy, the square root unit is designed as a 50-bit square root generating a 25-bit result in 26 clock cycles.

To avoid unnecessary power consumption in ALU, every major arithmetic unit is integrated with an isolation unit to tie the input to zero when there is no corresponding operation to eliminate unnecessary circuit switches [2]. This is illustrated in the following figure (Fig. 19).

3.2.8 Bus Architecture

The bus of DSP is of Harvard architecture with a 16-bit instruction bus and a 32-bit data bus. The bus architecture is shown in the following figure (Fig. 20).

Most operations in the metering algorithm are if 32 bits. The 32-bit data bus can achieve higher power efficiency than 64-bit data bus. And we can realize a 64-bit bus access through two 32-bit load/store operation.

Of the instruction bus, there is only one ROM (Read Only Memory) stored instruction for the DSP.

On the data bus, there is a SRAM, a set of register pool and some peripherals. SRAM acts as data for metering algorithms. Register pool stores configuration for DSP, analog front end and communication. Peripherals include some external modules for metering application.

3.2.9 Instruction Set Architecture

The instruction set is a highly optimized 16-bit RISC (Reduced Instruction Set Computing) Instruction set architecture (ISA).

3.2.9.1 NOP

The NOP (No Operation) instruction does nothing. It is used to fill the space for multi-cycle operations such as multiplication or to fill the delay slot in the branching operation.

3.2.9.2 Memory Access

LOAD/STORE instructions are used to exchange data between the registers and the memory. As there are only two 64-bit registers in the register file, only direct addressing mode is supported.

A SWAP instruction is used to swap information between regA and regB. As all ALU instruction is in the mode of “regA = ALU(regA, regB)”. A SWAP operation can reduce the need for load/store operation (Fig. 21).

3.2.9.3 ALU

ARC (Arithmetic Command) realizes a one-clock-cycle arithmetic operation for the complex add/sub operation. It is a combination of add/sub, shift and anti-saturation.

Multiplication/square root (MUL/SQT) realize multi-clock-cycle arithmetic operation for multiply and square root. Such operation starts with a START option and, after a curtain number of clock cycles, ends with a LOAD operation to load the result to the register. Between START and LOAD, any other instructions can be inserted to realize a parallel processing. If there is no other instruction to be executed, NOP must be inserted instead (Fig. 22).

3.2.9.4 Branching

There are unconditional jump instruction JMP and register RegC based conditional jump instruction JPC in the instruction set. There are two stages in the DSP pipeline, when executing the branch instruction, the next instruction is already fetched into the decoder, so a delay slot must be inserted after every branch instruction. The delay can be replaced by any instruction, if there is nothing to do, a NOP can be used as delay slot instruction. This is shown in the following figure (Fig. 23).

A special conditional jump flag instruction CND is introduced in this instruction set. CND is used to compare an internal counter with a given condition. This instruction is specifically designed for multi-rate realization. Through this we can easily design real-time multi-rate program (Fig. 24).

3.2.10 Reliability Consideration

Like most computer architecture, this energy metering DSP works basing on a Program Counter (PC), which increments by 1 for no-branching instruction and set to a destination address for branching instruction every clock cycle. For reliability consideration, typical MCU/DSP system introduces a Watch Dog Timer (WDT) unit. Through resetting the WDT, the MCU/DSP realizes a “Feed Dog” operation. If the WDT is not fed on time, it will reset the whole MCU/DSP system and reset PC to zero. The necessary feeding frequency is about 1 s. To enhance the reliability, this DSP introduces a similar method, but there is no need for “Feed Dog” operation. The WDT of this DSP resets the PC every 256 clock cycles. This makes the maxim number of fault operation is 255 and makes it a more stable design.

3.3 Low Power Communication Unit

MCU and metering chip are isolated, the communication between them need opto-coupler for each signal as shown in the following figure. The opto-coupler circuit needs a pull-up resister or pull-down resister that will consume extra power in some case. The key to save communication power is to reduce the number of opto-coupler (Fig. 25).

A half-duplex UART communication is used in the metering chip. Only 2 opto-couplers are need for this communication protocol. And as the data transaction is in a half-duplex way, only one opto-coupler may consume energy at one time (Fig. 26).

3.4 Low Power Analog Circuits Design

Most analog circuits have the same architecture as the one in the energy meter SoC in other chapter. In this energy metering chip, the most power consuming part, analog-digital-convert is optimized for lower power consumption. The following table shows current dissipation for each part of analog circuits (Table 1).

In most cases, the multi-function ADC is power off. Only in those applications that need extreme precision, the multi-function ADC is power on to measure the temperature and to calibrate the band-gap according to the temperature.

To further save power, the bias current of ADC can be reduced into two levels, the SNR of ADC will become worse, or in another words, we have to sacrifice metering performance for lower power consumption.

For reliable UART communication, we will need a stable clock. In case there is no external crystal oscillator, an internal clock has to be generated. Such internal RC oscillator is shown in the following figure (Fig. 27).

The high-speed RC oscillator is designed to generate a backup 3.2 MHz clock for external 3.2 MHz crystal. For a reliable UART communication, the maxim baud-rate error is 5 %. The RC oscillator is integrated with a trimming feature to be configured to 3.2 MHz ± 2 %, and can maintain a frequency of 3.2 MHz ± 3 % from − 40 to 85 °C. This RC oscillator consumes less power than external crystal oscillator, and makes the chip more reliable in case the external crystal is damaged.

3.5 Low Power Clock Network Design

An un-optimized clock network can consume 30 to 50 % power of the whole chip [3, 4]. The situation goes even worse for those slow modules like UART, SPI (Serial Peripheral Interface), RTC (Real Time Counter), etc. Clock gating is the most efficient methodology to reduce the power consumption of clock network. In the metering chip design, four stages of clock gating are introduced.

3.5.1 Clock Gating for Conditional Registers

By default, a conditional register can be implemented with a mux (multiplex) in front of a standard flop, as shown in the following figure. The register updates data from D when condition signal “cond” is true and keeps its value otherwise. For those conditional registers that only need to be updated occasionally, most of the power occurs in the associate clock network. Use clock-gating unit to realize the conditional function is a good alternative for further power saving (Fig. 28).

The clock-gating part of conditional register is not just a single AND, it must be a special design unit to avoid glitch on clock network. The following is a latch based clock-gating cell. The latch updates data from EN when CLK is low and gate the CLK with an AND cell (Fig. 29).

3.5.2 Clock Gating for Modules

There are a lot of conditional registers in the modules. Every group of conditional registers has a clock-gating unit. These clock gating units are loads of the clock tree, and will keep switching even the according conditional registers are clock-gated. To reduce this part of power consumption, a module level clock gating unit is implemented to further save the clock network power consumption when the module is in idle status or unselected (CS = 0). This is shown in the following figure (Fig. 30).

3.5.3 Clock Gating for Instructions

Not all modules need to be active for an instruction in the DSP. The decoder of DSP will find the necessary modules for current instruction and disable all unnecessary modules through clock gating. For instance, when executing the instruction NOP, no module is active, so all modules including ALU, register files, bus interface, etc. are clock-gated to save power. When executing a memory access instruction, ALU will be shut down through clock-gating to reduce power consumption (Fig. 31).

3.5.4 Clock Gating for Working Mode

For some extremely low power oriented applications, the chip needs to consume as little power as possible. For instance, in sleep mode as we described in previous sections, the chip works with power supplied by a battery, in this case, ultra low power design is the key to extend the battery life. A global clock gating unit is implemented into the chip for such circumstance to cut down the whole clock network, and leave only leakage current in the chip.

3.5.5 Multi-Stage Clock Gating Scheme

The clock gating is designed to be 3-stages in the metering chip as shown in the following figure (Fig. 32).

The first stage is a global clock gating. In sleep mode, the clock network is gated to achieve ultra low power consumption at about 4.5 μA.

The second stage is module level clock gating. It is controlled through the module select signal for those peripherals such as the register pool, or is controlled by the decoding result of current instruction.

The last stage is the conditional register clock gating. It controls the clock network for every group of registers with the same condition.

Most registers in the metering chip update their data in a very slow frequency, only RegA and RegB in the register file of the DSP core update in a relatively fast speed. Through the 3-stage clock gating, the power consumption of the clock network can be significantly reduced to a very low level less than 10 % power consumption of the whole chip.

4 Results

The metering chip is fabricated in TSMC mixed-mode technology and is assembled in a 16-pin SOP package. In a dynamic input range of 1:5000 of current signal, the chip’s metering error is less than 0.1 %. This performance can be maintained during − 40 to 85 °C working conditions. EMI rejection features can be proved to have 15 KV contact and non-contact discharge tolerance. It is the world’s first single phase energy metering chip consumes only 1.5 mA with full function. The die photo is shown in the following figure. This chip is currently in full production (Figs. 33 and 34).

References

Chih-hsien Kung; Devaney M J. “Multirate Digital Power Metering,” Proc. of the Instrumentation and Measurement Technology Conference, 1995.

Chandrakasan A P, Srivastava M B, Brodersen R W. Energy efficient programmable computation [A]. In: Proceedings of International Conference on VLSI Design, Calcutta, India, 1994, pp 261–264.

J Oh, M Pedram. Gated clock routing for low power microprocessor design. IEEE Trans. On CAD, Jun-2001, Vol. 20, No. 6, pp 715–722.

Mohanty S P, Ranganathan N, Krishna V. Datapath Scheduling using Dynamic Frequency Clocking[A]. In: IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, Pennsylvania, 2002, pp 58–63.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2014 Springer Science+Business Media New York

About this chapter

Cite this chapter

Yang, K., Zhong, S., Kong, Q., Men, C., Tan, N. (2014). Low Power Energy Metering Chip. In: Tan, N., Li, D., Wang, Z. (eds) Ultra-Low Power Integrated Circuit Design. Analog Circuits and Signal Processing, vol 85. Springer, New York, NY. https://doi.org/10.1007/978-1-4419-9973-3_7

Download citation

DOI: https://doi.org/10.1007/978-1-4419-9973-3_7

Published:

Publisher Name: Springer, New York, NY

Print ISBN: 978-1-4419-9972-6

Online ISBN: 978-1-4419-9973-3

eBook Packages: EngineeringEngineering (R0)