Abstract

Analysis and design of a low-noise transconductance amplifier (LNTA) aimed at selective current-mode (SAW-less) wideband receiver front-end is presented. The proposed LNTA uses double cross-coupling technique to reduce noise figure (NF), complementary derivative superposition, and resistive feedback to achieve high linearity and enhance input matching. The analysis of both NF and IIP3 using Volterra series is described in detail and verified by SpectreRF ® circuit simulation showing NF < 2 dB and IIP3 = 18 dBm at 3 GHz. The amplifier performance is demonstrated in a two-stage highly selective receiver front-end implemented in 65 nm CMOS technology. In measurements the front-end achieves blocker rejection competitive to SAW filters with noise figure 3.2–5.2 dB, out of band IIP3 >+17 dBm and blocker P1dB >+5 dBm over frequency range of 0.5–3 GHz.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

For a multi-standard radio receiver the wideband RF front-end circuit is essential. It is well known that a low-noise amplifier (LNA) as the first front-end stage largely decides the receiver performance in terms of noise figure (NF) and linearity. With relaxed requirements on RF filters the demands placed on the front-end linearity are usually increased according to intermodulation or cross-modulation effects evoked by strong interferers. While the nonlinear contribution of the following receiver stages is raised by the LNA gain, the overall NF is reduced. As a consequence a reasonable balance between linearity and noise performance of the LNA, mixer, and to some extent the baseband stages must be attained. One possible solution to this problem is a current-mode front-end where LNA is a transconductance amplifier (LNTA) followed by a passive mixer [1–7]. Since current rather than a voltage is applied, the mixer design is simplified and also the effect of 1/f noise is diminished. Most of those designs implement the concept of so called SAW-less front-end making use of N-path filtering [8]. In fact, it is the high output impedance of LNTA that jointly with low impedance of the N-path circuitry enables significant blocker attenuation at offset frequencies. In this case the demands for the input range (up to 0 dBm, i.e. 632 mVpp), and respectively for the linearity and compression of the LNTA, are exacerbated since the attenuation is achieved at the output rather than at the input of the amplifier. Additionally, such an LNTA is challenged by the requirement of wideband (WB) operation typical of the contemporary multi-band radios.

The LNTA nonlinearity originates from two major sources: nonlinear transconductance which converts linear input voltage to nonlinear output drain current, and nonlinear output conductance, the effect of which is evident under large output voltage swing. The latter can be avoided using a low impedance output load that is usually achieved using a passive mixer followed by a transimpedance amplifier (TIA) [1–6].

Several techniques exist to improve linearity of LNAs [9]. The optimization of gate bias voltages can fairly improve linearity of LNA [10] but it leads to reduced range of the input amplitudes and increased sensitivity to process variation. The WB negative feedback by resistive source degeneration also improves linearity but limits the voltage headroom of the devices and adds extra noise. Superposition of an auxiliary transistor to cancel nonlinearity of the main device, called derivative superposition (DS), extends fairly the linear gain range [11, 12]. Its variant referred to as the complementary DS also improves the second order nonlinearity of the amplifier [13]. More recently, this technique has been also presented in [7, 14, 15]. Unlike DS, in the post-distortion technique (PD) the auxiliary device operates in saturation and is controlled by the output voltage. The PD advantage is in superior PVT robustness as demonstrated e.g. in [16].

Other critical concerns in LNA/LNTA design i.e., the input matching and noise figure (NF) usually cannot be compromised. A popular wideband matching technique exploits the common gate (CG) circuit with its input impedance approximated by the inverse of the front device transconductance (1/gm). Since in this case gm is virtually bound to 20 mS, achieving larger effective values of the amplifier transconductance requires an extra amplification stage. To guarantee NF of the CG amplifier below 3 dB extra mechanisms are necessary, such as negative/positive feedback [17, 18], output noise cancellation using an auxiliary amplifier [19] (also called feed forward cancellation), or capacitive cross coupling when a balanced circuit is used [20]. Another WB matching technique providing a low NF is based on the reactive feedback which requires on-chip RF transformers [21].

A combination of a low noise figure with high linearity for wideband LNTA applications in CMOS was presented in [1–6, 13, 22, 23]. In particular, the noise cancelling receiver demonstrated in [4] extends the noise cancelling to the N-path filter/mixer resulting in the superior NF, but it consumes more power than the circuits using conventional noise cancellation [1–3, 5, 6].

In this paper we present analysis and design of LNTA suitable for current-mode wideband front-end with RF N-path filtering in 0.5–3 GHz frequency range. The LNTA design combines two linearization techniques, namely the derivative superposition and resistive feedback, with NF reduction by double capacitive cross-coupling which results in superior noise performance. The resistive feedback also helps to attain good input matching without sacrificing gain of the common gate input stage. By using elevated supply voltage the LNTA can tolerate blockers up to 0 dBm without compression. The mathematical analyses of NF and IIP3 are described in detail and the achieved estimates are verified by SpectreRF ® simulation. The LNTA is implemented and measured in a two-stage highly selective receiver front-end, integrated using 65 nm CMOS technology [7].

The paper is arranged as follows. In Sect. 2 we derive the LNTA circuit architecture combining various mechanisms to achieve the intended performance. In Sect. 3 we analyze the noise figure and verify the attained estimate by simulation. The Volterra series based analysis of IIP3 and verification is presented in Sect. 4. In Sect. 5 the LNTA implementation as a part of the receiver front-end with RF N-path filtering is presented. Conclusion is provided in the last section.

2 LNTA design

Based on our preliminary work [15], here, we describe the LNTA design in detail, including a complete noise and linearity analysis.

For high linearity we refer to the complementary DS technique, which due to the reusing of current, gives also significant power savings. The complementary common gate (CG) architecture has been preferred over its counterpart, common source (CS) (Fig. 1), for the ease in achieving wideband input matching and low noise figure.

By using appropriate bias voltages the nonlinear third order g m terms can be cancelled providing a high value of IIP3 [13, 14, 22, 24]. In this case the pMOS is an auxiliary transistor with g m much smaller than that of nMOS. Large off-chip inductors L 1, L 2 rather than resistors are used to guarantee maximum bias voltage V ds and thereby to reduce the g ds nonlinearity that is increasingly pronounced in deep submicron CMOS.

The input impedance and noise factor for the DS-CG circuit can be estimated from

where R so is the source resistance, γ is the excess channel thermal noise coefficient, and α = g m /g d0 , with g m as the device transconductance and g d0 as zero-biased channel conductance.

Clearly, for perfect matching we have F ≈ 1 + γ/α. In deep submicron CMOS γ/α > 2/3, and to reduce its effect on F we use a differential (balanced) variant of this circuit where the capacitive cross-coupling technique is adopted [20, 25]. In this case, F can be estimated from

according to partial noise cancellation achieved in this circuit. We observe that for γ/α ≈ 1, the expected noise figure is NF = 10log(1.5) ≈ 1.75 dB.

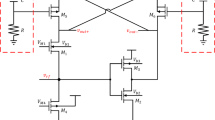

Further noise factor improvement as we proposed in [15] can be achieved by using double capacitive cross-coupling circuit shown in Fig. 2 (to be discussed in detail in Sect. 3).

By sizing up the transistors the LNTA transconductance can be increased to some extent, but the input impedance is decreased accordingly and the reflection coefficient S11 is largely deteriorated. One solution to mitigate this tradeoff is based on the source degeneration technique. Acting as a local negative feedback it additionally improves circuit linearity. With a resistance R sn as shown in Fig. 3 the LNTA input impedance can be restored as demonstrated by (4) for the n-MOS part of the circuit. Knowing that g m /C gs = 2πf T where f T ≈ 100 GHz, for simplicity we can assume ωC gs /g m = f /f T ≈ 0. Then for the nMOS part of the circuit we find

where Y dsn is the drain-source admittance and Z L is the loading impedance while the inductor reactance goes to infinity. A similar formula can be derived for the pMOS part (Z (p) in ) and assuming the drain-source admitances are small enough we find the LNTA input impedance as Z (p) in ‖Z (n) in .The LNTA transconductance is inversely proportional to Z in that is

Hence, there is a tradeoff between the input matching and LNTA gain. For perfect matching no increase in G m is achieved. In practice, however, the requirement is S11 < −10 dB. To meet this condition the corresponding boundaries of Z in can be found: \(Z_{in} \in \left( {0.67,\;{\kern 1pt} 2} \right)\,R_{so}\), where R so is the matching resistance. In an extreme case, when Z in = 2R so and R s = 0 we have G m ≈ 2/2R so . Next, the transistors are sized up and by using R s we obtain Z in = 0.67R so with the corresponding G m ≈ 3/R so . This means 3× increase in G m (9.5 dB) is feasible while S11 = −10 dB. Clearly, larger values of R s should be avoided here to preserve a sufficient V ds voltage headroom. Also the noise factor is traded for S11 as the R s resistors add noise. Moreover, when the loading impedance Z L is selective (as for N-path filters), its impedance goes down at offset frequencies and the input impedance (4) is reduced accordingly providing thereby attenuation of blockers at the amplifier input.

The proposed final LNTA circuit, designed in 65 nm CMOS is shown in Fig. 4. It combines the discussed above techniques to achieve high linearity and a low noise figure over a wide frequency range. Four off-chip inductors providing reactance of a few hundred Ohms each are large enough to guarantee S11 < −10 dB also at lower frequencies. Similarly, the coupling capacitances C s > 10 pF should be chosen (X s < 2 Ω) to avoid reduction of LNTA transconductance gain. Four of them (connected to transistor gates) must be integrated at the expense of the silicon area overhead. After choosing the bias voltages (to be discussed in Sec. IV) and the output DC equal to VDD/2 the sizes of the MOS transistors Mp, Mn were chosen to achieve the best third-order g m cancellation with 29 μm/65 nm and 48 μm/65 nm, respectively. The source degeneration resistors providing correction of S11 are R sp = 17 Ω and R sn = 111 Ω.

3 LNTA noise analysis

The circuit model for noise analysis is shown in Fig. 5. In each half of the circuit there are five noise sources to be considered: v ns (source noise), v nM1 (of M1), v nM3 (of M3), v nRsp (of R sp ) and v nRsn (of R sn ), using the following equations

where k is Boltzmann’s constant, T is the absolute temperature in Kelvin. The differential noise current at the output i n_out = i y − i x can calculated using superposition principle. In particular for v ns the currents i 1,…, i 4 as shown in Fig. 5 can be found as

with \(g_{m1,2t} = \frac{1}{{R_{sn} \left( {1 + \frac{{sC_{gsn} }}{{g_{m1,2} }}} \right) + \frac{1}{{g_{m1,2} }}}}\)

Using Kirchhoff’s Voltage Law (KVL) for the loop from v x to v y through v ns and Kirchhoff’s Current Law (KCL) at nodes v x , v y we have

Substituting (7) into (9), the voltage of v x − v y can be found as

with \(g_{m1,2tz} = g_{m1,2t} \left( {1 + \frac{{2sC_{gsn} }}{{g_{m1,2} }}} \right)\),

The output differential noise current i ns_out = i y − i x due to noise source of v ns can be calculated as

With similar procedure, we can calculate the output differential noise currents i nM1_out , i nM3_out , i nRsp_out , i nRsn_out due to v nM1, v nM3, v nRsp and v nRsn respectively

The same noise contribution will be achieved from the other half of the circuit. The noise factor (F) and noise figure (NF) will be calculated based on (12–16) as

In order to compare NF of the proposed circuit to the one with conventional cross-coupling, the equivalent circuit can be simplified by ignoring the gate-source capacitances. The noise factor in this case will be

The input impedance of the differential circuit ideally should be Z in = 2R so . Then for matching we need

For brevity we can assume that the differential circuit is perfectly balanced having the same γ, α values for all transistors. Then (19) can be simplified to

It should be noted that the double cross-coupling results in ¼ coefficient for the (γ/α) contribution as compared to ½ for the traditional cross-coupling. Moreover, the noise factor contribution by the source degeneration resistors (the 3rd term in (21)) appears less than the one by transistors for (γ/α) > 1. A comparison between NF of the proposed circuit and the conventional one (3) for g m1 = g m2 = 30 mS, g m3 = g m4 = 13.6 mS, R so = 50 Ω, R sn = 111 Ω, R sp = 17 Ω, is shown in Table 1. With technology scaling the ratio (γ/α) is increasingly large so the NF improvement is more pronounced. For example with (γ/α) = 1.5 the proposed LNTA can improve NF from 2.43 dB down to 1.34 dB.

The NF comparison of the presented analytical model and SpectreRF® circuit simulation including the gate-source capacitances according to (12-16) is shown in Fig. 6. In this verification we use specifications captured from the designed chip: g m1 = g m2 = 30 mS, g m3 = g m4 = 13.6 mS, R so = 50 Ω, R sp = 17.2 Ω, R sn = 110.8 Ω, C gsn = 30 fF, C gsp = 20 fF. As seen the respective differences remain within 0.08 dB that can be considered negligible.

4 Linearity analysis using Volterra Series

The simulation environment using a conventional inverter, here, also considered as common-source complementary DS circuit, with output bias voltage was proposed in [13] as shown in Fig. 7(a). This circuit can achieve high linearity due to subtraction of the nonlinear current components of the transistors M p and M n . Both the second and third order terms can be partly cancelled if the circuit is appropriately biased. However, the useful input range is very narrow as shown for g 3 in Fig. 7(b) where g 3 = ∂3 i o /∂(V in )3. In effect the possible blockers are not well tolerated by this circuit, still resulting in significant distortion.

A possible way to overcome this problem is using different bias voltages for M p and M n in combination with the resistive source degeneration applied to the both transistors as presented in Fig. 8(a) [15]. In Fig. 8(b), the input voltage range can be significantly increased comparing the previous case in Fig. 7(b). The combined g 3 is less than its components g n3 and g p3 in the operating range as seen in the zoom view. Moreover, it should be noted that R sp is much less than R sn in order to maintain the output bias voltage at V dd /2 while M n is larger than M p . Should we increase the size of M p and the resistance of R sp , the effective g 3 would be less, but its range would shrink degrading the linearity for large blockers.

The following analysis aims at describing IIP3 and third-order gain H 3 of LNTA using the Volterra series approach. Figure 9 shows the small-signal model for linearity analysis where the differential circuits are assumed to be identical for simplicity. The drain current of M p and M n can be modelled up to 3rd-order as

where g ip and g in are the ith-order coefficients of M p and M n , accordingly, obtained by taking the derivative of the drain DC current I SD /I DS with respect to the gate-source voltage V SG /V GS at the DC bias point

Applying the Volterra series to the output voltage

where v in = v inp − v inn and v out = v outp − v outn . If circuits are completely symmetric v out can be calculated as

From (27) and (57) from Appendix 1, we have

where

Substituting (59–64), (45), (51–55), (22–23) into (58) and comparing with (28), we can find A 1, A 2 and A 3

If two single-ended circuits are identical, we substitute (28, 29) into (31) and have

From [16, 23], IIP3 can be estimated as

DS technique has been used to cancel the third-order transconductance distortion g 3 well [9] but the operating range of input voltage V gs is not wider than 200 mV. In this design, we propose a technique that can cancel the third-order voltage gain (41) in larger operating range up to 650 mV shown in Fig. 10. From that figure, the bias voltages can be chosen as Vgsn = 570 mV and Vsgp = Vgsn + 190 mV = 760 mV. Therefore IIP3 of LNTA is not sensitive to the bias voltages and can tolerate large blockers up to 0 dBm.

The IIP3 obtained by the Volterra series model (42) and by SpectreRF™ simulations are depicted in Fig. 11 for two RF frequencies with the following parameters g 1n = 30 mS, g 1p = 13.6 mS, g 2n = 57 (mA/V2), g 2p = 8.2 (mA/V2), g 3n = −70.3 (mA/V3), g 3p = −9.6 (mA/V3), r dn = 339 Ω, r dp = 843 Ω at VDD = 2.5 V with R so = 50 Ω, L p = 30 nH, L n = 70 nH, R sp = 17.2 Ω, R sn = 110.8 Ω, C gsn = 30 fF, C gsp = 20 fF.

IIP3 comparison of analytical expression (42) and SpectreRF® simulation for LNTA, using two-tone 40 MHz spacing (transistor level)

As shown, IIP3 is rising with the loading capacitance due to the reduced output voltage swing. For the same reason larger IIP3 values are attained at the higher operating frequency. It should be noted that the increment of IIP3 for C load increased from 0.2 pF to 1 pF (5×) at f RF = 520 MHz is almost the same as the one achieved for the frequency change from 520 MHz to 3 GHz (~5× as well) for C load = 0.2 pF.

In post-layout simulation with pad and bonding wire parasitics the IIP3 estimate at f RF = 3 GHz with 40 MHz spacing is reduced by 4 dB, i.e. from 22 dBm at transistor level to 18 dBm for 2.5 V supply. The Monte-Carlo post-layout simulation under process variation with fixed bias is shown in Fig. 12. The mean value is 17.9 dBm while the standard variation is only 0.24 dB. To see the separate contributions to IIP3 by the different mechanisms used we found IIP3 to be reduced by 3 dB, down to 15 dBm, for supply voltage changed to the standard value, 1.2 V. The circuit will lose 6 dB more when the derivative superposition technique is excluded resulting in IIP3 = 9 dBm. Finally, by removing the resistive degeneration, IIP3 = 5 dBm is attained.

Using a linear model also the LNTA transconductance estimate can be verified against the analytical model (5). From simulations over the operating frequency range with Z L ≪ r ds , G m varying between 17 and 17.7 mS can be found whereas from (5) it is around 18 mS. To reduce the effect of r ds on G m in this simulation a larger C L = 4 pF has been chosen.

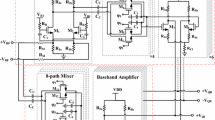

5 Implementation of a selective receiver front-end

The proposed LNTA is used in a selective two-stage RF front-end [7] shown in Fig. 13. In order to tolerate blockers up to 0 dBm (632 mVpp) we have used elevated supply voltage of 2.5 V for LNTA1 and the standard supply of 1.2 V for the LNTA2. To prevent loading of the first stage, which could degrade the filter transfer function, a simple CMOS buffer is added in front of LNTA2 as shown in Fig. 14. The schematic topology of LNTA2 is similar to LNTA1 except for the values of bias voltages, resistances and sizes of transistors. The design was fabricated in 65 nm CMOS technology and the chip photo is shown in Fig. 15. A significant portion of the chip area is occupied by the banks of baseband capacitors C BB , which allow for bandwidth programming. The maximum power consumption at 3 GHz amounts for 113 mW and it drops to 46 mW at 0.5 GHz.

Chip photo [7]

With N-path filter as a load the LNTA noise figure is raised by approximately 1 dB that can be attributed to noise folding as devised in [7]. In effect, the two-stage front-end NF varies between 3.2 dB and 5.2 dB for frequencies between 500 MHz and 3 GHz, respectively. The NF at 2 GHz under 0 dBm blocker with 100 MHz offset is 12 dB that is below the 3GPP limit. Similarly, the in-band IIP3 is only less than 0 dBm due to large loading impedance (large voltage swing). On the contrary, the out-of-band IIP3 is as large as +20 dBm in the lower frequency range and +17 dB at 3 GHz. Additionally, superior blocker rejection of 44 dB is attained for frequencies up to 2 GHz and 38 dB at 3 GHz owing to the two-stage filtering [7]. Measured S11 for different LO frequencies is shown in Fig. 16. Within the whole frequency range 0.5–3 GHz, S11 is below −10 dB in the bandwidth of interest.

A comparison of the state-of-the-art and the presented LNTA design as well as the respective RF front-end based on N-path filtering is given in Table 2. In simulations the stand-alone amplifier compares favorably to the other work. Clearly, the LNTA design is critical for the performance of the measured front-end which, while superior in terms of blocker rejection, can be found well in line with the remaining state-of-the-art specifications.

6 Conclusions

In this paper we have presented LNTA design suitable for current-mode wideband front-end in CMOS technology. The amplifier architecture has been derived from the common gate circuit making use of complementary DS technique, which enables highly linear amplification. The tradeoff between the input matching and the transconductance of transistors (g m ) has been mitigated by resistive source degeneration. As a negative feedback it also supported the amplifier linearity. On the other hand, a suitable impedance mismatch at the input was useful to achieve a larger amplifier gain (G m ).

Superior noise performance has been attained by the double capacitive cross-coupling technique in a differential setup as proposed in this work. In effect, the LNTA compares favorably with the state-of-the-art designs both in terms of NF and linearity.

We have presented a complete NF analysis and Volterra series based IIP3 analysis of the amplifier. The obtained estimates were shown compliant with the circuit simulation results. The LNTA was implemented in 65 nm CMOS as a part of a tunable RF front-end using two-stage N-path filtering technique that provided blocker rejection competitive to SAW filters. Owing to the LNTA design the front-end linearity and noise performance have been placed well in line with the state-of-the-art.

References

Ru, Z., et al. (2009). Digitally enhanced software-defined radio receiver robust to out-of-band interference. Journal of Solid-State Circuits, 44(12), 3359–3375.

Yu, C. Y., et al. (2011). A SAW-less GSM/GPRS/EDGE receiver embedded in 65-nm SoC. IEEE Journal of Solid-State Circuits, 46(12), 3047–4060.

Mirzaei, A., et al. (2011). A 65 nm CMOS quad-band SAW-less receiver SoC for GSM/GPRS/EDGE. IEEE Journal of Solid-State Circuits, 46(4), 946–950.

Murphy, D., Darabi, H., et al. (2012). A blocker-tolerant, noise-cancelling receiver suitable for wideband wireless applications. IEEE Journal of Solid-State Circuits, 47(12), 2943–2963.

Kim, J., & Silva-Martinez, J. (2013). Low-power, low-cost CMOS direct-conversion receiver front-end for multistandard applications. IEEE Journal of Solid-State Circuits, 48(9), 2090–2103.

Fabiano, I., et al. (2013). SAW-less analog front-end receivers for TDD and FDD. IEEE Journal of Solid-State Circuits, 48(12), 3067–3079.

Qazi, F., et al. (2015). Two-stage highly selective receiver front-end based on impedance transformation filtering. IEEE Transactions on Circuit and Systems II, 62(5), 421–425.

Franks, L. E., & Sandberg, I. W. (1960). An alternative approach to the realization of network transfer functions: The N-path filter. Bell System Technical Journal, 39(5), 1321–1350.

Zhang, H., & Sanchez-Sinencio, E. (2011). Linearization techniques for CMOS low noise amplifiers: A tutorial. Transactions on Circuit and Systems, 58(1), 22–36.

Aparin, V., et al. (2004). Linearization of CMOS LNAs via optimum gate biasing. Proceedings of IEEE International Conference on Circuits and Systems, IV, 748–751.

Kim, T. W., Kim, B., & Lee, K. (2004). Highly linear receiver front-end adopting MOSFET transconductance linearization by multiple gated transistors. Journal of Solid-State Circuits, 39(1), 223–229.

Aparin, V., et al. (2005). Modified derivative suprposition method for linearizing FET low-noise amplifiers. IEEE Transactions on Microwave Theory Techniques, 53(2), 571–581.

Im, D., et al. (2009). A wideband CMOS low noise amplifier employing noise and IM2 distortion cancellation for a digital TV tuner. Journal of Solid-State Circuits, 44(3), 686–698.

Geddada, H. M., et al. (2014). Wide-band inductorless low-noise trans-conductance amplifiers with high large-signal linearity. IEEE Transactions on Microwave Theory and Techniques, 62(7), 1495–1505.

Duong, Q.-T., & Dąbrowski, J. (2011). Low noise transconductance amplifier design for continuous-time delta sigma wideband front-end. European Conference on Circuit Theory and Design (ECCTD), 3, 825–828.

Zhang, H., et al. (2009). A low-power, linearized, ultra-wideband LNA design technique. Journal of Solid-State Circuits, 44(2), 320–330.

Woo, S., et al. (2009). A 3.6 mW differential common-gate CMOS LNA with positive-negative feedback. IEEE International Solid-State Circuits Conference—Digest of Technical Papers, ISSCC, 2009, 218–219.

Kim, J., et al. (2010). Wideband common-gate CMOS LNA employing dual negative feedback with simultaneous noise, gain, and bandwidth optimization. IEEE Transactions on Microwave Theory and Techniques, 58(9), 2340–2351.

Bruccoleri, F., et al. (2004). Wide-band CMOS low-noise amplifier exploiting thermal noise canceling. Journal of Solid-State Circuits, 39(2), 275–282.

Zhuo, W., et al. (2000). Using capacitive cross-coupling technique in RF low noise amplifier and down-conversion mixer design. European Solid-State Circuits Conference, ESSCIRC, 3, 77–80.

Reiha, M., & Long, J. (2007). A 1.2 V reactive-feedback 3.1–10.6 GHz low-noise amplifier in 0.13 μm CMOS. Journal of Solid State Circuits, 42(5), 1023–1033.

Chen, W.-H., et al. (2008). A highly linear broadband CMOS LNA employing noise and distortion cancellation. Journal of Solid-State Circuits, 43(5), 1164–1176.

Blaakmeer, S. C., et al. (2008). Wideband balun-LNA with simultaneous output balancing, noise-canceling and distortion-canceling. Journal of Solid-State Circuits, 43(6), 1341–1350.

Ahsan, N. et al. (2008). Highly linear wideband low power current mode LNA. International Conference on Systems and Electronic Systems, ICSES. doi:10.1109/ICSES.2008.4673361

Amer, A., et al. (2007). A 90-nm wideband merged CMOS LNA and mixer exploiting noise cancellation. Journal of Solid-State Circuits, 42(2), 323–328.

Mehrpoo, M., & Staszewski, R. B. (2013). A highly selective LNTA capable of large-signal handling for RF receiver front-ends. In Proceedings of IEEE RFIC symposium (pp. 185–188).

Zhang, L., et al. (2015). Analysis and design of a 0.6–10.5 GHz LNTA for wideband receivers. Transactions On Circuits and Systems II, Express Briefs, 62(5), 431–435.

Mirzaei, A., et al. (2011). A low-power process-scalable super-heterodyne receiver with integrated high-Q filters. Journal of Solid-State Circuits, 46(12), 2920–2932.

Darvishi, M., et al. (2013). Design of active N-path filters. Journal of Solid-State Circuits, 48(12), 2962–2976.

Author information

Authors and Affiliations

Corresponding author

Appendices

Appendix 1: Derivation of the Volterra operators for the proposed LNTA: G1, G2 and G3

For the circuit shown in Fig. 9 the respective currents and voltages can be expressed as

where

Substituting (22, 23) into (43, 44) with maximum 3rd order of v in , we have

where

Substituting (22, 23), (45, 51–55) into (46), we have

Appendix 2: Derivation of the Volterra operators for the proposed LNTA: A1, A2, A3, H1, H2 and H3

For the circuit of Fig. 9 the current and voltage equations follow

where

For differential mode, the single voltages should be

Rights and permissions

About this article

Cite this article

Duong, QT., Qazi, F. & Dąbrowski, J.J. Analysis and design of low noise transconductance amplifier for selective receiver front-end. Analog Integr Circ Sig Process 85, 361–372 (2015). https://doi.org/10.1007/s10470-015-0629-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0629-5