Abstract

Frequency multiplication by 3/2 is proposed as a means to expand the frequency generation capabilities of a single LC VCO. Fractional frequency multiplication is obtained by cascading a broadband injection locked modulo-two divider and a multiply-by-three circuit based on edge combining. The proposed solution is inductorless, thus very compact. It allows the generation of all frequencies from 2.7 to 6.1 GHz with a performance suitable for cellular standards. It shows a phase noise floor below −150 dBc/Hz and a spurious level below −35 dBc. The multiplier by 3/2 consumes 5 mA and the VCO draws 10 mA from a 1.2 V supply. The additional power consumption due to the multiplier trades with the small area penalty and the flexibility of this solution, compared to the use of multiple LC VCOs.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The evolution of multi-standard radios has led to devices capable of combining many different functions on a single chip. Transceivers compliant to all GSM and WCDMA standards are now available in a monolithic form (see e.g. [1, 2]). One of the key factors of this rush towards integration is the ever increasing miniaturization of the available technology, which allows for increased functionality per unit area, and better performance of the active devices at radio frequencies. Ultra-scaled technologies, on the other hand, do not bring about particular advantages as far as passive components are concerned. Worse than that, passive components do not scale in area as their active counterparts do. Since silicon area is increasingly expensive as technology scales down, the use of large passive components such as inductors is becoming increasingly critical. Some building blocks, however, cannot avoid the use of area-consuming passive devices. Frequency generation circuits, for example, have to rely on high quality LC tanks to comply with the stringent phase noise requirements of cellular standards. In order to perform the generation of the carriers for all standards, they also have to feature quite a large tuning range (TR).

Accommodating a large tuning range while achieving low phase noise is not an easy task to accomplish. Changing the capacitance in the LC tank is the usual way to tune the oscillation frequency. Wide tuning range LC oscillators are usually designed employing a digitally controlled switched capacitor bank, along with a small varactor for continuous tuning capability [3, 4]. This arrangement shows a trade-off between achievable tuning range and phase noise performance, such that it is very difficult to obtain a tuning range of an octave, and still show a phase noise performance compliant with e.g. the GSM standard. The use of multi-mode resonators has been proposed as a means to expand the tuning range of LC oscillators [5]. This solution adds complexity to the design, but it helps reducing the power consumption (in the worst case) for a given overall tuning range and a target phase noise performance. However, it still awaits a proof of its effectiveness over other approaches, even the use of multiple LC oscillators, as far as area consumption is concerned.

One characteristic of multi-standard radios that allows to skew a little the issue of broadband frequency generation and look at it from a different perspective is that the phase noise requirements change depending on the particular carrier we need to generate. In fact, GSM and WCDMA standards call for different phase noise performances. Moreover, it is worth to notice that almost all the GSM and WCDMA bands can be addressed by a single voltage controlled oscillator (VCO) operating from 2.7 to 4.1 GHz, i.e. at twice (or four times) the carrier frequencies, combined with a set of suitable frequency dividers. The latter are anyway required to generate the phases for quadrature modulation/demodulation. In this context, only WCDMA band VII, extending from 2.5 to 2.7 GHz, is not covered.Footnote 1 As such, a dedicated solution could be devised. A supplementary LC VCO tailored for band VII would be the simplest approach, leading to low power consumption, because of the limited required tuning range and the somewhat relaxed phase noise specifications (compared to GSM). The area occupation of the additional tank is however an issue. An inductorless approach would be preferred.

In this paper, we propose to use a fractional frequency multiplier combined with a high performance LC VCO to generate all the carriers required by the GSM and WCDMA standards, including the WCDMA band VII. The multiply-by-3/2 circuit addresses the latter frequency range. Since it is inductorless, it is very compact. Combined with the 2.7–4.1 GHz VCO, it allows the generation of all frequencies from 2.7 to 6.1 GHz, thus covering more than an octave. Such an approach could also be considered for systems operating on a even broader range of frequencies than the cellular systems, e.g. the software-defined radios.

Since the phase noise requirements for the WCDMA band VII are more relaxed compared to the performance that the VCO must show in the other bands, the 4 dB penalty introduced (at small offsets from the carrier) by the frequency multiplication by 3/2 is not an issue. Nevertheless, the noise floor introduced by the multiplier has to be low enough, such that the operation of the transceiver as a whole is not impaired. WCDMA is a frequency division duplexing (FDD) system, where the transmitter and the receiver operate at the same time. At large offsets, the phase noise is dictated by the leakage of the transmitter into the receiver at the duplexer distance. We target a transmitter leakage 6 dB below the thermal noise floor (−174 dBm/Hz), not to impair the noise figure of the receiver [6]. Considering a 55 dB duplexer attenuation, available from commercial products, the phase noise floor at 120 MHz offset (i.e., the distance between receive band VII and transmit band VII) from a +24 dBm carrier should be below −149 dBc/Hz.

The paper is organized as follows: in Sect. 2 the proposed architecture, made of the cascade of a VCO, a divide-by-two block and a multiply-by-3 circuit, is described. The details of the circuit-level implementation of the multiplier and the divider are addressed in Sects. 3 and 4, respectively, while some discussion on the alternatives to the proposed solution is carried out in Sect. 5. The VCO design is described in Sect. 6. Transistor-level simulation results are presented in Sect. 7. Eventually, the paper is wrapped up in Sect. 8.

2 Fractional frequency multiplier: concept and system architecture

In order to expand the range of frequencies generated out of a single VCO, we propose to employ fractional frequency multiplication by 3/2. In this way, starting from an oscillator with a tuning range narrower than one octave, it is possible to obtain a continuous frequency tuning in excess of 2:1, in turn enabling the generation of any other lower frequency by successive frequency divisions by two, in principle down to DC.

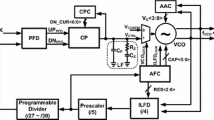

A block diagram of the proposed system is shown in Fig. 1. The VCO operates from 2.7 to 4.1 GHz, that is at twice (or four times) the frequencies required in the GSM/EDGE standards (GSM850, GSM900, DCS, PCS). It also enables the generation of the carriers for all the bands in the WCDMA standard, with the exception of the band VII. In any case, frequency division by two (or by four) is required to generate the actual LO signals and the phases for quadrature up- or down-conversion.

The key building block is the fractional frequency multiplier by 3/2, which is made of the cascade of a modulo-two divider and a tripler. Note that the choice of dividing first results in lower frequencies of operation for the sub-circuits making up the fractional multiplier, as compared to the complementary choice of multiplying first. The VCO signals from 3.3 to 3.6 GHz are input to the fractional frequency multiplier to achieve (twice) the frequencies required for the WCDMA band VII. Note that spanning the entire VCO tuning range one gets at the output of the fractional multiplier the frequencies from 4.0 to 6.1 GHz, which, combined to those produced by the VCO itself, give a continuous frequency range in excess of one octave.

In the following, we will describe in details the tripler implementation and the multi-phase input signals it requires, as well as the block feeding the tripler, which combines the division-by-two and the multi-phase generation functions.

3 Frequency multiplication by edge combining

The technique we employ to achieve frequency multiplication is edge combining [7]. The input signal is made of three replicas of the clock, each phase shifted by ±120° with respect to the others. On the rising edges of each input waveform pulses are generated and then combined. The output waveform is thus at three times the frequency of the input signal. The operation principle of edge combining is sketched in Fig. 2.

The details of the proposed circuit-level implementations are shown in Fig. 3. The pulses are created by a classic monostatic circuit based on a NAND gate. Pulse combination is performed in the current domain, in a wired-or fashion. A pseudo-nMOS load made of a pMOS device completes the ratioed logic gate implementing the edge combiner. The entire circuit is replicated to achieve a pseudo-differential configuration. The outputs are fed to an SR latch to regenerate rail-to-rail signals out of the ratioed logic levels.

The accuracy of the phase shifts in the input waveforms is of great importance to get a clean frequency multiplication. In fact, if the phase progression of the inputs is not uniform, the pulses generated at the output will not be evenly distributed in time. As a consequence, a spurious tone at the same frequency of the input will show up in the spectrum of the output waveform. The larger the mismatch in the 0–120–240° phase progression, the larger the spurious. We can analyze the impact of the phase mismatch on the spurious generation with the help of Fig. 4. The actual signal at the output of the tripler, v out(t), can be decomposed in the sum of an ideal signal, v idl(t), and a spurious signal, v spr(t):

In v idl(t), the time shift between the combined pulses is exactly T/3, T being the period of the input waveform. The spurious signal takes into account the leads and lags between the combined pulses. In the time-domain, it can be written as

where a 1,2 = 1 if the actual pulse lags the ideal one, and a 1,2 = −1 if the actual pulse leads the ideal one. Note that, without lack of generality, we assume unitary amplitude for v out(t), v idl(t), and v spr(t) (after all we are interested in the analysis of the spurious tones).

Taking the Fourier transform of (2), we obtain:

where \(F=1/T,\,\delta_1 = D_1/T\), and \(\delta_2 = D_2/T\). The larger spurious tone is generated at the frequency of the input waveform. Setting k = 1 in (3), approximating \({\rm sinc} (\delta_{1,2})e^{j \pi a_1 \delta_{1,2}}\approx 1\), since \(\delta_{1,2} \ll 1\), assuming for simplicity \(\delta_1 = \delta_2 = \delta\), and normalizing by the amplitude of the spectrum of v idl(t) at the output frequency (i.e. at three times the input frequency), we can estimate the relative spurious amplitude as

in the worst case when a 1 and a 2 have different signs. To put (4) in perspective, consider that to achieve a spurious level below −25 dBc, \(\delta\) must be as small as 1%. Consequently, the phase error in the phase shifted signals must be smaller than 3.6°.

The way the phase shifted signals are generated is therefore crucial for the correct operation of the tripler. This issue will be addressed in the next Section.

4 Division by two and triphase generation

The modulo-two divider is the key building block in the system, as it both performs the frequency division, and generates the phase-shifted signals required by the tripler. Both functions are accomplished by a three-stage injection-locked ring oscillator.

This solution is compact and robust, as broad locking ranges are attainable. As a consequence, the circuit does not require any calibration or tuning. Moreover, it does not affect the phase noise performance at low frequency offsets, because of the injection locking mechanism. However, at larger frequency offsets a noise floor is observed, due to the noise added by the various devices at the output of the divider.

4.1 Injection locked divide-by-two circuit

The divider is based on direct injection-locking of a differential three-stage ring oscillator, as illustrated in Fig. 5. The particular choice of the number of stages of the ring and the differential architecture result in a six-phase output signal, i.e. the output nodes of the ring are arranged in a phase progression with 60° steps. This allows us to combine the division by two and multi-phase generation function required by the edge combiner in one single building block.

Each delay cell is made of a current-starved inverter in which an nMOS differential pair is loaded by a cross-coupled pMOS pair. The resulting logic is basically of the ratioed type. The ratio of the pMOS to nMOS device size is chosen for balanced operation. All the cells share a common current source implemented by a resistor, to limit its noise contribution and current consumption.

A multi-phase multiple inputs scheme [8] is used to widen the locking range. Since the ring features three stages, and frequency division by two is performed, the input signals must be phase shifted by ±120° with respect to each other. The resulting phase sequence is not trivial, i.e. a dedicated circuit has to generate it, as discussed in Sect. 4.2.

Frequency division is achieved by super-harmonic injection locking, which, to take place, needs some mixing operation to occur. In fact, a tone must be generated at a frequency close to the free running frequency of the ring oscillator, such that the latter is pulled to it. The injection devices, whose operation is sketched in Fig. 6, act as current commutating mixers. It can be shown [9] that, for typical values of the input signal amplitude (V inj) and quiescent point (V CM), the injection devices are almost always on and in the saturation region. The input synchronization signal is applied to the gate terminal, such that the drain current contains a component at the input frequency. Because of the large signal AC operation of the ring oscillator, the drain and source terminals, which are connected to the output nodes of the ring oscillator, swap every half period of the output waveform. As a consequence, the drain current of the injection transistors changes polarity and is effectively modulated by a wave at the output frequency. The beating between the input signal and the output wave results in the mixing operation required by the super-harmonic injection-locking mechanism. The current injected at the locking frequency ωinj is approximately calculated [9] as:

where \(\beta=\mu C_{\rm ox}{\frac{W}{L}}\) is the gain factor of the injection device, and V t,n is its threshold voltage.

Despite resulting from quite a coarse approximation, (5) gives fundamental design guidelines, since larger injection currents result in a wider locking range. A large amplitude of the injection signal, V inj, helps increasing the locking range. Nevertheless, even a relatively small injection signal may result in a broad locking range if an adequate value of V CM is selected. Moreover, larger injection devices enhance the locking range.

4.2 Triphase generation circuit

The triphase injection signals needed to lock the modulo-two divider are generated by means of a passive three-phase filter.

Asymmetric sequence polyphase filters are able to generate N-phase signals out of differential (or even single-ended) ones and to reject unbalances in the obtained phase sequences [10].

For the sake of completeness, in the following we review briefly the fundamentals of the theory presented by Gingell [10], which is instrumental for the correct design of the triphase generation circuit. Any set of N phasors \(a_n,\,n=1\ldots N\), can be represented as a linear combination of N symmetrical sequences weighted by the complex coefficients \(s_r,\,r=1\ldots N\), with

Vice versa, once the coefficients s r are known, the set of N unbalanced phasors is obtained as

Note that the vectors of the symmetrical sequences can be explicitly obtained by setting all s r but one equal to zero in (7). For example, in the case N = 3, the symmetrical sequences are the common mode signal \([1\; 1\; 1]\), the forward sequence \([1\; e^{-j{\frac{2\pi}{3}}}\; e^{-j{\frac{4\pi}{3}}}]\), and the reverse sequence \([1\; e^{j{\frac{2\pi}{3}}}\; e^{j{\frac{4\pi}{3}}}]\). Since the forward and reverse sequences are one the complex conjugate of the other, they can be interpreted as a set of positive frequency phasors and a set of negative frequency phasors, respectively. The decomposition of a generic set of unbalanced phasors in symmetrical sequences by means of (6) is illustrated in Fig. 7 for the case of N = 3.

The key property of asymmetric sequence polyphase filters is that they are capable of attenuating the reverse (forward) sequence while passing the forward (reverse) sequence through. Since we aim at generating a balanced triphase signal out of a differential one, we employ a polyphase filter to reject the reverse (or negative frequency) sequence embedded in the differential signal. However, since the polyphase filter does not reject the common-mode sequence s 1, the differential signal we start from (i.e. the unbalanced sequence) must be carefully selected. Using (6), one can see that choosing the a n phasors as \([1\; 0\; {-1}]\) avoids the generations of a common-mode sequence, as this choice results in the sequence coefficients \(s_1=0, \,s_2=e^{j{\frac{\pi}{6}}}/\sqrt{3}\), and \(s_3=e^{-j{\frac{\pi}{6}}}/\sqrt{3}\).

Because of the symmetry of the circuit, the transmission zeros of the polyphase filter can be derived analyzing one generic output node of a single section. In the general N-phase case, shown in Fig. 8, each output node is connected to each input node by an admittance Y k . For the r-th sequence, for each pair of corresponding terminals, the input–output relationship is [10]

where, assuming no loading at the output nodes,

From (9), for the r-th sequence, the condition for the output voltage to be nulled is

In our design N = 3. To derive the required filter parameters, let’s consider the forward sequence (r = 2), and let’s assume that each output is only connected to two adjacent inputs. With these assumptions, (10) is recast as

Setting for simplicity Y 1 = 2/R, from (11) we get

As a consequence, choosing Y 2 as the parallel combination of a resistance R and a capacitance \(\sqrt{3}C\), the filter will show a zero at a negative angular frequency equal to ω− = −1/RC, while it will not show a zero at the corresponding positive frequency ω+ = 1/RC, as (11) is not satisfied for ω = ω+. Since, as previously discussed, a negative frequency for the forward sequence can be interpreted as the reverse sequence, the filter will let the forward sequence through, while suppressing the reverse sequence.

In Fig. 9 the schematic of the designed triphase generation circuit is depicted. As discussed, the connection of the input signal to the polyphase filter is critical to achieve output signals that are evenly spaced apart by 120°. The filter is designed following the same guidelines as the more common four-phase case [10]. Two sections are used, yielding two transmission zeros. The zero frequencies are staggered to achieve a broader frequency response. Moreover, the impedance of the second stage is made larger to decrease the loading of the first stage.

As discussed in Sect. 3, a precise phase progression is very important to avoid large spurious tones in the spectrum of the tripler. In Fig. 10, the phase error \(\Updelta \phi\) in the signals output by the triphase filter is shown for the nominal values of the resistances and capacitances, and for ±20 % spreads. In the worst case, the phase error is smaller than 6° within the tuning range of the VCO. The phase error gets halved at the output of the frequency divider. As a consequence, using (4) we expect a worst case spurious level below −27 dBc at the output of the tripler

5 Digression on alternative architectures

The discussion carried out in Sect. 4.2 on polyphase filters suggests that another approach can in principle be followed to implement the frequency multiplication by 3/2. The six phases needed by the edge combiner could be generated using a six-phase filter, while the modulo-two division could be realized in a standard fashion by a digital state machine, avoiding the potential issue of failures in the injection locking process. The six-phase filter will have zeros at the negative angular frequency of −1/RC if \(Y_1=1/R,\,Y_2=Y_3=j\omega C/\sqrt{3}\), and Y k = 0 for \(k=4\ldots6\), as can be verified using (10). This approach, however, has a severe problem, in that the digital implementation of the divide-by-two has square-wave outputs with a rich harmonic content, and it is well known that polyphase filters are impaired by the presence of higher harmonics. As a consequence, the time delays between the output waveforms are not the required ones, and the resulting phase sequence is deteriorated. On the other hand, in the proposed architecture the triphase filter is directly driven by the VCO, which features a highly sinusoidal output voltage. The impedance of the triphase filter should be high enough, in order not to affect the quality factor and the resonance frequency of the VCO.

6 Voltage controlled oscillator

A thorough discussion of the VCO design is carried out in [6]; here we report its main features for the sake of completeness. Figure 11 shows a highly simplified schematic view of the VCO. It is the classical differential single-switch (SS) pair LC-tank architecture, which was preferred to the double-switch (DS) pair architecture because of the improved robustness in the presence of parasitic capacitance at the (single-ended) outputs of the LC tank [11]. Since such a parasitic capacitance is largely unavoidable in a very-large-TR VCO, the SS VCO has a phase-noise lead of several dB on the DS VCO [11]. Another advantage of the SS topology is that the oscillation amplitude can ideally swing from 0 V (ground) to twice V dd, which helps achieving a very low phase noise (at the price of a large current consumption). In principle, this can be accomplished with the DS VCO as well, if powered from a 2V dd power supply; however, the PMOS pair in the DS VCO needs to be scaled up by at least a factor 2 compared to the NMOS pair, which greatly increases the total parasitic capacitance in parallel to the LC tank, impairing both TR and phase noise.

The tail bias current of the VCO is set by a number of resistors (controlled by a 4-bit digital word) instead of NMOS current sources, in order to avoid the up-conversion of 1/f NMOS noise. On the other hand, this choice lowers the tail impedance, with a somewhat adverse impact on the loss introduced by the cross-coupled transistors [12], as well as on the up-conversion of their 1/f noise into 1/f 3 phase noise.

The oscillation frequency is set in a digital fashion with a capacitor bank [3, 13], divided into a 5-bit coarse tuning and a 5-bit fine tuning, after which an analog voltage and an AMOS varactor perform the finest frequency control and enable phase lock in a mixed-mode PLL. The analog tuning constant of the VCO is small (between 12 and 32 MHz/V across the TR), and therefore there is no need for a very large capacitor in the PLL loop filter to keep the effect of thermal noise at an acceptable level. Thus, the loop filter can be fully integrated with a modest area consumption (especially considering the overall area of the multi-standard radio) without any noise penalty. Phase modulation for GSM/PCS/DCS signals is achieved through a second AMOS varactor, whose size is adjusted according to the standard being addressed. This varactor, much smaller than the former one, is designed for sufficiently linear phase modulation.

Overall, after investigating several alternatives, the chosen VCO architecture was found to yield the best trade-offs between power consumption, phase noise, TR, and area.

In order to avoid the hazard of frequency pulling on the TX VCO, it is crucial to minimize the parasitic magnetic coupling between the TX VCO and the other circuits in the radio, notably the RX VCO and the power amplifier (PA). In fact, both TX VCO and RX VCO are active at the same time and at very close frequencies in WCDMA mode, and may easily pull or modulate each other, due to their relative proximity on the same silicon chip. Furthermore, although both VCOs are operating at twice or four times the frequency of the PA, previous experience showed that the second or fourth harmonic of the single-ended PA output may be strong enough to pull them. This issue is particularly critical in GSM/EDGE mode, where the TX VCO must be immune to a PA carrier power level above 30 dBm.

A very effective way of minimizing magnetic pulling on a VCO is to adopt an 8-shaped layout for the inductor (Fig. 12), which rejects any common-mode magnetic field [14, 15] . Additionally, the magnetic field generated by the 8-shaped coil vanishes (far) away from the coil, further reducing the pulling risk between RX VCO and TX VCO.

The inductor quality factor diminishes by approximately 30 % in the 8-shaped coil, but the process used still allows for a very high Q (about 25 at 4 GHz), since in the CMOS technology employed in this work it is possible to put two thick metal layers in parallel to minimize resistive losses (indeed, the availability of such a high-Q inductor is a necessary condition to obtain the desired VCO performance).

7 Simulation results

The proposed circuit has been simulated at the transistor level in a digital 90 nm CMOS technology. In Fig. 13, the intrinsic phase noise of the VCO running at 3.6 GHz is shown, along with the phase noise of the corresponding waveform at the output of the fractional multiplier at 5.4 GHz. At small offsets, the difference between the two curves is the expected 20 log103/2 = 4 dB . At offsets larger than 100 MHz, the noise floor shown by the multiplier is below −150 dBc/Hz, compliant to the WCDMA band VII requirements.

As discussed, any imbalance in the phase sequence at the input of the edge combiner results in a spurious tone in the multiplier output spectrum at the frequency of the input signal. The phase imbalances are due to the limited rejection of the negative frequency sequence in the triphase generator, to the presence of harmonics in the VCO output, and to mismatches in the components of the frequency multiplier. The spectrum at the output signal of the multiplier is shown in Fig. 14. The desired signal is at 5.4 GHz, while a spurious tone with a −41 dBc lower level is observed at 1.8 GHz.

The spurious level, relative to the desired signal, is shown in Fig. 15 across the entire frequency range of operation of the designed circuit. The frequency indicated in the plot is the frequency of the spurious tone, i.e. the frequency of the input waveform of the edge-combining tripler. In any case, the undesired tone is below −35 dBc.

The entire circuit consumes 15 mA from a 1.2 V supply. The oscillator draws 10 mA, while the remaining 5 mA are split almost evenly between between the injection-locked frequency divider and the edge combiner.

8 Conclusion

An inductorless approach to expand the frequency range that can be obtained out of a single LC VCO has been presented. It is based on the cascade of a divide-by-two and a multiply-by-three circuit, with a resulting fractional frequency multiplication by 3/2. This approach makes it possible to achieve an overall frequency range in excess of one octave, from 2.7 to 6.1 GHz. The lower portion of this range is covered by a high performance LC VCO compliant with the stringent GSM phase noise requirements. The higher portion is achieved by the fractional multiplier, which features a performance still suitable to the cellular standards, and in particular to the WCDMA band VII, with a phase noise floor below −150 dBc/Hz and a spurious level below −35 dBc.

The key building block of the presented circuit is the injection-locked modulo-two divider that combines frequency division-by-two with multi-phase signal generation, enabling the operation of the following edge combiner. A triphase filter is used to generate the correct phase sequence needed for injection-lock.

Notes

It is worth noticing that it is not desirable to let the VCO operate at the carrier frequency, to avoid pulling from the power amplifier of the radio.

References

Nilsson, M., Mattisson, S., Klemmer, N., Anderson, M., Arnborg, T., Caputa, P., Ek, S., Fan, L., Fredriksson, H., Garrigues, F., Geis, H., Hagberg, H., Hedestig, J., Huang, H., Kagan, Y., Karlsson, N., Kinzel, H., Mattsson, T., Mills, T., Mu, F., Mandrtensson, A., Nicklasson, L., Oredsson, F., Ozdemir, U., Park, F., Pettersson, T., Pandhlsson, T., Pandlsson, M., Ramon, S., Sandgren, M., Sandrup, P., Stenman, A., Strandberg, R., Sundstroandm, L., Tillman, F., Tired, T., Uppathil, S., Walukas, J., Westesson, E., Zhang, X., & Andreani, P. (2011). A 9-band WCDMA/EDGE transceiver supporting HSPA evolution. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (pp. 366–368) San Francisco, CA.

Cicalini, A., Aniruddhan, S., Apte, R., Bossu, F., Choksi, O., Filipovic, D., Godbole, K., Hung, T.-P., Komninakis, C., Maldonado, D., Narathong, C., Nejati, B., O’Shea, D., Quan, X., Rangarajan, R., Sankaranarayanan, J., See, A., Sridhara, R., Sun, B., Su, W., van Zalinge, K., Zhang, G., & Sahota, K. (2011). A 65nm CMOS SoC with embedded HSDPA/EDGE transceiver, digital baseband and multimedia processor. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (pp. 368–370). San Francisco, CA.

Kral, A., Behbahani, F., & Abidi, A. (1998). RF-CMOS oscillators with switched tuning. In Proceedings of the IEEE Custom Integrated Circuits Conference (pp. 555–558). Santa Clara, CA.

Berny, A. D., Niknejad, A. M., & Meyer, R. G. (2005). A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration. IEEE Journal of Solid-State Circuits, 40(4), 909–917.

Bevilacqua, A., Pavan, F. P., Sandner, C., Gerosa, A., & Neviani, A. (2007). Transformer-based dual-mode voltage controlled oscillators. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(4), 293–297.

Andreani, P., Kozmin, K., Sandrup, P., Nilsson, M., & Mattsson, T. (2011). A TX VCO for WCDMA/EDGE in 90 nm RF CMOS. IEEE Journal of Solid-State Circuits, 46(7), 1618–1626.

Oncu, A., Wasanthamala Badalawa, B. B. M., & Fujishima, M. (2007). 22–29 GHz ultra-wideband CMOS pulse generator for short-range radar applications. IEEE Journal of Solid-State Circuits, 42(7), 1464–1471.

Chien, J.-C., & Lu, L.-H. (2007). Analysis and design of wideband injection-locked ring oscillators with multiple-input injection. IEEE Journal of Solid-State Circuits, 42(9), 1906–1915.

Dal Toso, S., Bevilacqua, A., Tiebout, M., Da Dalt, N., Gerosa, A., & Neviani, A. (2010). An integrated divide-by-two direct injection-locking frequency divider for bands S through K u . IEEE Transactions on Microwave Theory and Techniques, 58(7), 1686–1695.

Gingell, M. J. (1975). The synthesis and application of polyphase filters with sequence asymmetric properties. Ph.D. dissertation. London: University of London. Available Online: http://www.ethos.ac.uk.

Andreani, P., & Fard, A. (2006). More on the 1/f 2 phase noise performance of CMOS differential-pair LC-tank oscillators. IEEE Journal of Solid-State Circuits, 41(12), 2703–2712.

Murphy, D., Rael, J. J., & Abidi, A. A. (2010). Phase noise in LC oscillators: A phasor-based analysis of a general result and of loaded Q. IEEE Transactions on Circuits and Systems-I: Regular Papers, 57(6), 1187–1203.

Sjöland, H. (2002). Improved switched tuning of differential CMOS VCOs. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 49(5), 352–355.

Mattsson, T. (2006). Method of and inductor layout for reduced VCO coupling. US Patent 7,151,430 B2.

Nagata, M., Masuoka, H., Fukase, S., Kikuta, M., Morita, M., & Itoh, N. (2006). 5.8 GHz RF transceiver LSI including on-chip matching circuits. In Proceedings of IEEE Bipolar/BiCMOS Circuits and Technology Meeting (pp. 1–4).

Acknowledgments

This work has been partially supported by the VINNOVA Industrial Excellence Center in System Design on Silicon (SoS) at the Dept. of Electrical and Information Technology, Lund University, Sweden.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bevilacqua, A., Andreani, P. A 2.7–6.1 GHz CMOS local oscillator based on frequency multiplication by 3/2. Analog Integr Circ Sig Process 74, 11–20 (2013). https://doi.org/10.1007/s10470-012-9892-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9892-x