Abstract

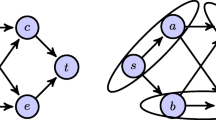

The logical test of integrated VLSI circuits is one of the main phases of their design and fabrication. The pseudo-exhaustive approach for the logical test of integrated circults consists in partitioning the original circuits to be tested into non-overlapping subcircuits with a small, bounded number of subcircuits, which are then exhaustively tested in parallel. In this work, we present an approximate algorithm for the problem of partitioning integrated combinational circuits, based on the tabu search metaheuristic. The proposed algorithm presents several original features, such as: the use of a reduced neighborhood, obtained from moves involving only a subset of boundary nodes; complex moves which entail several resulting moves, although the variations in the cost function are easily computable; a bi-criteria cost function combining the number of subcircuits and the number of cuts, which simultaneously adds a diversification strategy to the search; and the use of a bin-packing heuristic as a post-optimization step. The behavior of the proposed algorithm was evaluated through its application to a set of benchmark circuits. The computational results have been compared with those obtained by the other algorithms in the literature, with significant improvements. The average reduction rates have been of the order of 30% in the number of subcircuits in the partition, and of the order of 40% in the number of cuts.

Article PDF

Similar content being viewed by others

Avoid common mistakes on your manuscript.

References

A.A. Andreatta, A graph partitioning heuristic for the parallel pseudo-exhaustive logical test of VLSI combinational circuits, M.Sc. Dissertation, Department of Electrical Engineering, Catholic University of Rio de Janeiro (1994), in Portuguese.

E.C. Archambeau and E.J. McCluskey, Fault coverage of pseudo-exhaustive testing,Digest of Papers of the 14th Int. Conf. on Fault-Tolerant Computing (IEEE, 1984) pp. 141–145.

Z. Barzilai, D. Coppersmith and A.L. Rosenberg, Exhaustive generation of bit patterns with applications to VLSI self-testing, IEEE Trans. Computers C-32(1983)190–193.

F. Berglez and H. Fujiwara, A neutral netlist of 10 combinational benchmark circuits and a target translator inFortran, Paper presented at the special session onATPG and Fault Simulation, Int. Symp. on Circuits and Systems, Kyoto (IEEE, 1985).

Z. Barzilai, J. Savir, G. Mankowsky and M.G. Smith, The weighted syndrome sums approach to VLSI testing, IEEE Trans. Computers C-30(1981)996–1001.

S.N. Bhatt, F.R.K. Chung and A.L. Rosenberg, Partitioning circuits for improved testability,Proc. 4th MIR Conf. on Advanced Research in VLSI (MIT, Cambridge, 1986) pp. 91–106.

S. Bozorgui-Nesbat and E.J. McCluskey, Structured design for testability to eliminate test pattern generation,Digest of Papers of the 10th Int. Symp. on Fault-Tolerant Computing (IEEE, 1980) pp. 158–163.

M.A. Breuer and A.D. Friedman,Diagnosis and Reliable Design of Digital Systems (Computer Science Press, Woodland Hills, 1976).

E. Calia and A. Lioy, Test generation in a distributed environment, Research Report, Instituto Politecnico di Torino (1991).

C.L. Chen, Linear dependencies in linear feedback shift registers, IEEE Trans. Computers C-35(1986)1086–1088.

M. Davis-Moradkhan, The problem of partitioning the nodes of a graph and its applications in VLSI technology: An overview, Rapport MASI 90.08, Laboratoire MASI, Université Paris VI (1990).

M. Davis-Moradkhan, Partitioning problems in VLSI technology, Doctorate Thesis, Université Paris VI (1993), in French.

M. Davis-Moradkhan and C. Roucairol, Comparison of two heuristics for partitioning combinational circuits for parallel pseudo-exhaustive testing, Rapport MASI 92.25, Laboratoire MASI, Université Paris VI (1992).

M. Davis-Moradkhan and C. Roucairol, Graph partitioning applied to the problem of logic testing of VLSI combinational circuits, Rapport MASI 92.41, Laboratoire MASI, Université Paris VI (1992).

M.R. Garey and D.S. Johnson, Strong NP-completeness results: Motivation, examples and implications, J. ACM 25(1978)499–508.

F. Glover, Future paths for integer programming and links to artificial intelligence, Comp. Oper. Res. 13(1986)533–549.

F. Glover, Tabu search — Part I, ORSA J. Comput. 1(1989)190–206.

F. Glover, Tabu search — Part II, ORSA J. Comput. 2(1990)4–32.

F. Glover, Tabu search: A tutorial, Interfaces 20(1990)74–94.

F. Glover and H.J. Greenberg, New approaches for heuristic search: A bilateral linkage with artificial intelligence, Euro. J. Oper. Res. 39(1989)119–130.

F. Glover and M. Laguna, Tabu search, in:Modern Heuristic Techniques for Combinatorial Problems, ed. C.R. Reeves (Blackwell, London, 1993) pp. 70–150.

A. Hertz and D. de Werra, Using tabu search for graph coloring, Computing 29(1987)345–351.

A. Hertz and D. de Werra, The tabu search metaheuristic: How we used it, Ann. Math. Art. Int. 1(1990)111–121.

E.J. McCluskey, Built-in self-test techniques, IEEE Design Test Comp. 2(1985)21–28.

E.J. McCluskey, Built-in self-test structures, IEEE Design Test Comp. 2(1985)29–36.

E.J. McCluskey and S. Bozorgui-Nesbat, Design for autonomous test, IEEE Trans. Computers C-30(1981)866–874.

S.D. Millman and E.J. McCluskey, Detecting bridging faults with stuck-at test sets,Proc. Int. Test Conf. (IEEE, 1988) pp. 773–783.

Y. Min and Z. Li, Pseudo-exhaustive testing strategy for large combinational circuits, Comp. Syst. Sci. Eng. 1(1986)213–220.

E.I. Muehldorf and A.D. Savkar, LSI logic testing — An overview, IEEE Trans. Computers C-30(1981)1–17.

O. Patashnik, Optimal circuit segmentation for pseudo-exhaustive testing, Doctorate Thesis, Department of Computer Science, Stanford University (1990).

C.V. Ramamoorthy and R.C. Cheung, Design of fault tolerant computing systems, in:Applied Computation Theory: Analysis, Design, Modeling, ed. R.T. Yeh (Prentice-Hall, Englewood Cliffs, 1976) pp. 286–296.

M.W. Roberts and P.K. Lala, An algorithm for the partitioning of logic circuits, IEEE Proc. G 131(1984)113–118.

S.C. Seth, B.B. Bhattacharaya and V.D. Agrawal, An exact analysis for efficient computation of random-pattern testability in combinational circuits,Digest of Papers of the 16th Int. Symp. on Fault-Tolerant Computing Systems (IEEE, 1986) pp. 318–323.

I. Shperling and E.J. McCluskey, Circuit segmentation for pseudo-exhaustive testing via simulated annealing,Proc. Int. Test Conf. (IEEE, 1987) pp. 58–66.

J.G. Udell and E.J. McCluskey, Efficient circuit segmentation for pseudo-exhaustive test,Proc. IEEE Int. Conf. on Computer-Aided Design (IEEE, 1987) pp. 148–151.

L.T. Wang and E.J. McCluskey, Condensed linear feedback shift register (LFSR) testing — A pseudo-exhaustive test technique, IEEE Trans. Computers C-35(1986)367–369.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Andreatta, A.A., Ribeiro, C.C. A graph partitioning heuristic for the parallel pseudo-exhaustive logical test of VLSI combinational circuits. Ann Oper Res 50, 1–36 (1994). https://doi.org/10.1007/BF02085633

Issue Date:

DOI: https://doi.org/10.1007/BF02085633