Abstract

The International Roadmap for Devices and Systems (IRDS) forecasts that, for silicon-based metal–oxide–semiconductor (MOS) field-effect transistors (FETs), the scaling of the gate length will stop at 12 nm and the ultimate supply voltage will not decrease to less than 0.6 V (ref. 1). This defines the final integration density and power consumption at the end of the scaling process for silicon-based chips. In recent years, two-dimensional (2D) layered semiconductors with atom-scale thicknesses have been explored as potential channel materials to support further miniaturization and integrated electronics. However, so far, no 2D semiconductor-based FETs have exhibited performances that can surpass state-of-the-art silicon FETs. Here we report a FET with 2D indium selenide (InSe) with high thermal velocity as channel material that operates at 0.5 V and achieves record high transconductance of 6 mS μm−1 and a room-temperature ballistic ratio in the saturation region of 83%, surpassing those of any reported silicon FETs. An yttrium-doping-induced phase-transition method is developed for making ohmic contacts with InSe and the InSe FET is scaled down to 10 nm in channel length. Our InSe FETs can effectively suppress short-channel effects with a low subthreshold swing (SS) of 75 mV per decade and drain-induced barrier lowering (DIBL) of 22 mV V−1. Furthermore, low contact resistance of 62 Ω μm is reliably extracted in 10-nm ballistic InSe FETs, leading to a smaller intrinsic delay and much lower energy-delay product (EDP) than the predicted silicon limit.

Similar content being viewed by others

Main

In recent years, 2D layered semiconductors with atom-scale thicknesses have been explored as potential channel materials to avoid short-channel effects2,3,4,5,6, and the gate lengths of 2D FETs have even been scaled below 5 nm (refs. 7,8). However, so far, no experimental results have demonstrated that, with the standard supply voltage of 0.7 V (the supply voltage in commercial silicon 10-nm node), the on-state current and transconductance of 2D semiconductors-based FETs can surpass those of state-of-the-art silicon FETs, and experimental results of 2D semiconductors-based FETs still lag far behind that of theoretical predictions and are insufficient to show the ultimate potential of 2D semiconductors9,10,11. This is because of several challenges, such as the low-quality interface between 2D semiconductors and high-k dielectrics12, poor source and drain contacts with considerable Schottky barrier at 2D semiconductor–metal interfaces13,14,15,16 and the inherent shortcomings of 2D semiconductors17.

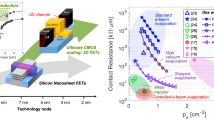

Figure 1a depicts the basic physical rules for designing ultrascaled ballistic transistors with good on and off characteristics by referring to two key material parameters: thermal velocity and scale length18,19. InSe is physically superior to Si for larger thermal velocity (smaller effective mass) and smaller scale length19 (thinner body and smaller dielectric constant20), as suggested in Fig. 1a. Also, small valley degeneracy (gC = 1) for InSe (compared with gC = 2 for ultrathin silicon) is another advantage for achieving smaller delay and lower power consumption (Supplementary Fig. 1). In this work, we use three-layer InSe to construct ultrashort ballistic transistors, aiming to explore the ultimate potential of 2D semiconductors.

a, Thermal velocities and scale lengths in silicon and typical 2D semiconductor materials. b, Schematic of a double-gate InSe FET. c,d, Transmission electron microscopy image and electron energy-loss spectroscopy map showing a cross-section of an InSe FET with double-gate structure; top-gate length about 5 nm, bottom-gate length about 10 nm, channel length about 10 nm, InSe thickness about 2.4 nm, HfO2 thickness about 2.6 nm. Scale bars, 10 nm. e, Calculated formation energy of possible doping or adsorption configurations in the Y-InSe system. The gold, blue and purple spheres represent In, Se and Y atoms, respectively. Adsorption cases: Y atom is absorbed on the surface of InSe on top of a hollow site (ads-H) and on the top of In atom (ads-In). Doping cases: Y atom is trapped interstitially between Se atoms (inter-Se), between In atoms (inter-In) and between InSe atoms (inter-H); Y atom substitute for In atom (sub-In) and for Se atom (sub-Se). f, Calculated band structure for trilayer InSe and yttrium-doping-induced phase-transition contact region (in which Y atoms are substitutionally doped in the top layer of InSe). g, Shift of XPS spectra (all C 1s peak at 284.8 eV) of Y-InSe compared with the standalone InSe. AU, arbitrary units. h, Transfer characteristics of two types of ballistic device at VDS = 0.1 V, including Y-InSe channel (purple curve), pure InSe channel (orange curve) and compared with 1-nm Y channel (grey curve). i, Schematic side view of yttrium-doping-induced phase-transition contact. The band alignment of pure semiconducting InSe with semimetal Y-InSe. CBM, conduction band minimum; VBM, valence band maximum; vdW, van der Waals. j, Output characteristics of a typical 10-nm ballistic InSe FET using Y-doping-induced phase-transition contact and a typical 10-nm InSe FET directly using conventional Ti/Au contact. The total resistance is about 124 Ω μm for our ballistic InSe FET using Y-doping-induced phase-transition contact.

A schematic drawing of the 2D InSe transistor structure used in this work is shown in Fig. 1b and cross-sectional high-resolution scanning transmission electron microscopy (STEM) imaging of a real device with a 10-nm channel length and 2.6-nm-thick HfO2 dielectrics is shown in Fig. 1c. The spatial distributions of indium, hafnium, titanium, gold and yttrium (Y) were observed in the electron energy-loss spectroscopy maps of the FET (Fig. 1d), confirming the locations of the 2D InSe channel, HfO2 dielectrics, electrodes and the existence of a thin layer of yttrium, which was introduced and used to improve the contacts between the source/drain metal and 2D InSe through yttrium-doping-induced phase transition. Details on the fabrication process and a scanning electron microscopy (SEM) image of our devices are included in Extended Data Fig. 1.

The realization of ohmic contacts is of crucial importance for constructing high-performance FETs. Usually, 2D-materials-based devices tend to have large contact resistance between metal electrodes and 2D semiconductors owing to the severe Fermi-pinning effects3. To overcome this problem, here we adopt a phase-transition method in the contact region by using yttrium doping to convert semiconducting InSe into semimetallic Y-InSe. Density functional theory (DFT) is first used to search for the most probable doping lattice structure by calculating the formation energies of different structural configurations for Y atoms doped to InSe layers, including different types of adsorption, interstitial doping and substitutional doping (Fig. 1e). The calculation results show that Y atoms are extremely prone to replacing In atoms because the system energy decreases in this substitutional-doping process and, thus, this Y-InSe configuration has the lowest energy and is the most stable among all potential structures. The band structure of this most stable Y-InSe configuration is then calculated by DFT and the results show that there exists a very small overlap between the bottom of the conduction band and the top of the valence band in Y-InSe, that is, semiconductor InSe has been converted into semimetal Y-InSe through substitutional doping (Fig. 1f and Supplementary Figs. 2 and 3). Experimentally, we developed the following process to achieve Y doping in InSe: the contact area was treated with low-power argon plasma (to induce active sites) after electron-beam exposure and development, followed by rapid evaporation of 1 nm Y and Ti/Au electrode metals in high vacuum (1 × 10−8 torr). When annealing at 230 °C for 30 min in an inert-gas environment, the solid-dopant-source yttrium tends to diffuse into the top-layer InSe (ref. 21), causing the substitutional activation of dopant Y atoms at the active sites (induced by the previous process of plasma) in the top-layer InSe. Furthermore, we carried out detailed characterization to verify the predicted semiconductor to semimetal phase transition. (1) After removing the excess Y by selective wet etching, X-ray photoelectron spectroscopy (XPS) was performed on the surface of the fabricated Y-InSe sample, showing that Y signal (with different binding energy to that of pure Y metal) appears in the treated 2D Y-InSe sample (Fig. 1g, bottom). (2) Both In 3d and Se 3d peaks (Fig. 1g, top and middle) shift towards the lower-energy direction in the XPS spectra, providing strong evidence of Y-doping-induced phase transition from semiconductor to semimetal16,22. (3) Y substitutional doping changes the lattice structure of top-layer InSe and generates new vibrational modes, resulting in two further peaks in the Raman spectrum (Supplementary Fig. 4). (4) As the most direct evidence, the electric-transfer characteristics in Fig. 1h strongly suggest that the FET with the doped Y-InSe as the channel has semimetallic properties with particularly weak gate-field modulation (on/off ratio < 10, purple), which is much lower than that of the pure InSe channel (on/off ratio > 107, orange).

The band alignment between Y-InSe and intrinsic InSe is calculated and shown in Fig. 1i, demonstrating that the Fermi level of the semimetallic Y-InSe is located above the conduction band minimum of pure InSe, meaning that the band alignment is appropriate between the top-layer semimetallic Y-InSe and the lower-layers semiconducting InSe for electron injection from Y-InSe to the conduction band of InSe. Moreover, the internal van der Waals interface between the top-layer semimetallic Y-InSe and lower-layers semiconducting InSe remains clean and, as a result, the source and drain contacts are free of the Fermi-pinning effect14. A typical InSe FET using semimetallic Y-InSe contacts shows a total resistance of 124 Ω μm, which is two orders of magnitude smaller than those using conventional Ti/Au contact, leading to superior on-state performance in output characteristics (Fig. 1j).

Figure 2a shows seven typical saturation output characteristics of our ballistic transistors compared with those of other reported 2D short-channel FETs. As a result of the high injection velocities and excellent ohmic contacts of our 2D InSe FETs, only 0.4 V drain voltage (VDS) is required to saturate the currents and to surmount 1 mA μm−1, which is much lower than those of other short-channel 2D FETs (a VDS of more than 1.2 V is needed to reach 1 mA μm−1)8,12,23,24,25,26,27,28. We benchmark the total resistance (Fig. 2b) and drain current (VDS = 0.5 V) of our ballistic InSe FETs and previous reports when considering the same inversion charge29 (Fig. 2c and Extended Data Fig. 2a). The external metal line resistances in our devices are measured and de-embedded to correct the total resistance as shown in Supplementary Fig. 5. It should be noted that extraction of 2RC is usually done by using a transmission-line method (TLM) (our 2RC by TLM is approximately 83 Ω μm; Extended Data Fig. 2b,c), but the TLM method for extracting RC is strongly affected by resistance fluctuations among long-channel FETs with different lengths3. Because the channel of a ballistic transistor does not suffer from scattering (Fig. 2d), a far more reliable method to extract RC is thus directly from the saturation output characteristics of the ballistic transistor, as we do here. Furthermore, technology computer-aided design (TCAD) simulations are performed for the double-gate structure with a back-gate-to-contact overlap in InSe FETs, as shown in Supplementary Fig. 6.

a,b, Saturation output characteristics (with maximum gate voltage) and total resistance comparison of our ballistic 2D InSe FETs and other 2D short-channel FETs8,12,23,24,25,26,27,28. c, Benchmarking total resistance versus carriers density ns in a few representative reports29. The red stars are the total resistance of our representative 10-nm-channel-length ballistic InSe FET and the dashed line is the theoretical limit of InSe FETs calculated using the Landauer formula. The numbers in parentheses is the channel length (nm). d, Schematic diagrams of temperature-related diffusive and ballistic transport modes in transistors. e, Transfer characteristics of a typical 10-nm ballistic 2D InSe FET at various temperatures ranging from 300 K to 100 K. f, Typical transfer characteristics of our ballistic 2D InSe FET with ohmic contact (Y/Ti/Au, red) and a ballistic 2D InSe FET with unoptimized normal Schottky contact (Ti/Au, yellow). There seem to be two segments in the subthreshold region on the transfer characteristics of the Ti/Au-contact device (yellow), corresponding to thermal emission (TE) and thermal field emission (TFE), which is consistent with the 40-nm WS2 FET in a previous report26. By comparison, our ohmic-contact InSe FET (red) shows only a single thermal-emission process in the whole subthreshold region. g, Schematic band diagrams related to Schottky contact and ohmic contact.

Figure 2e shows that our ohmic-contact ballistic 10-nm 2D InSe FETs have a constant on-state current over a wide temperature range (300 K to 100 K) and this behaviour is similar to that observed previously in carbon nanotube transistors (ballistic, ohmic contact)30, which is strong evidence that ohmic contacts have been achieved in our ballistic transistors (compared with typical Schottky contacts in a non-optimal ballistic InSe FET in Extended Data Fig. 3a–c). In long-channel diffusive FETs, with increasing temperature, the scattering in the channel is increased, leading to reduced on-state current, and this is an opposite temperature-related trend with respect to the Schottky-barrier thermionic emission (Fig. 2d). There exists only a single thermal emission region (lack of thermal field emission region) in the subthreshold transfer characteristics of our InSe FETs in Fig. 2f,g, and this fact serves as direct evidence for the realization of ohmic contact with negligible Schottky barrier in our InSe FETs31. Furthermore, the quantum limit of contact resistance in an InSe ballistic transistor is calculated by the Landauer formula (Extended Data Fig. 3d).

To benchmark the performance of our 2D InSe FETs against those of silicon counterparts, we directly compare five typical transfer characteristics of our 2D InSe FETs (Fig. 3a) to those of 10-nm-node silicon (Intel) and 20-nm-gate InGaAs (IBM) FinFETs with the standard off-state current of 100 nA μm−1 for high-performance integrated circuits (ICs)32,33. The 2D InSe FETs show saturation currents comparable with that of silicon FinFET but at a much lower supply voltage of 0.5 V (versus 0.7 V for silicon Fin) and also exceed those of InGaAs FinFETs. A record peak transconductance of 6 mS μm−1 (at 0.5 V) is realized in our 2D InSe FETs (Fig. 3b), which is also the highest value against all reported low-dimensional nanomaterial-based FETs and is comparable with that of Si 10-nm-node FinFET (Intel) but with a lower voltage of 0.5 V (versus 0.7 V for silicon) and three times larger than that of InGaAs FinFET (IBM). The gate capacitances of our devices are shown in Extended Data Fig. 4. More transconductance values of our devices are presented in Extended Data Fig. 5. The on-state performance parameters of our InSe FETs are compared with those of other short-channel 2D FETs in Fig. 3c,d. Our on-state current ranges from 0.7 to 1.2 mA μm−1 and our transconductance ranges from 3 to 6 mS μm−1 at an ultralow voltage of VDD = 0.5 V, approximately one order of magnitude larger than those of other 2D FETs, even those with a larger supply voltage of VDD = 1 V (refs. 8,23,24,25,26). By fitting our data with the standard ballistic Virtual Source Model (MIT), the ballistic ratios in the saturation region of our 2D FETs were extracted and reached more than 83%, which is the highest recorded value for 2D-based transistors so far and surpassed those of all the previously reported silicon FETs34,35,36 (Fig. 3e and Extended Data Fig. 6).

a, Transfer characteristics comparison of five typical ballistic 2D InSe FETs (coloured dots), 10-nm-node silicon FinFET (Intel, solid black line)32 and 20-nm-LG InGaAs FinFET normalized by state-of-the-art Fin Pitch = 34 nm (IBM, dashed black line)33. Note that all currents are normalized with the same rule. b, Transconductance comparison of five typical ballistic 2D InSe FETs in a, a 10-nm-node silicon FinFET (Intel, solid black line) and an InGaAs FinFET (IBM, dashed black line)32,33. c,d, On-state current (ION) and peak-transconductance comparison of ballistic 2D InSe FETs at VDD = 0.5 V and other 2D FETs with sub-50-nm LG at VDD = 1 V (VDD = VDS = VGS)8,23,24,25,26. The on-state current and peak-transconductance values are extracted from the transfer characteristics across a voltage window of VDD and with a standard off-state current of 100 nA μm−1. e, Benchmark of ballistic ratios of our InSe FETs with those of silicon MOS FETs, including bulk Si FET34, FinFET35 and double-gate (DG) Si FETs36. f–h, Scaling trends of VDD, gate delay and EDP (with parasitic capacitance) of our ballistic 2D InSe FETs compared with those of silicon FETs (the silicon data are from IRDS 2022 and Intel)1,32,37. A low-k spacer structure with a width of 4 nm (in 2037, in IRDS 2022) and different dielectric constants, from 2.5 (in 2037, in IRDS 2022) to 13 (in our work), is assumed to be embedded to evaluate the delay and EDP of overlap-free InSe ballistic transistors, and we also give the non-optimized extrinsic values with bottom gate (BG)/top gate (TG) overlap. Also, we calculated the parasite-contained delay and EDP of silicon FETs (based on the FEOL parasitic capacitance in IRDS 2022) and also the Intel 10 nm and 14 nm as a benchmark.

The power dissipation of a modern IC is strongly dependent on the supply voltage through VDD3. A practical voltage-saving strategy is to improve the transconductance of a conventional MOS FET to save the overdrive voltage. The high thermal velocity and ballistic ratio, ultrathin HfO2 double-gate structure and source/drain ohmic contact in our FETs boost the transconductance up to a record 6 mS μm−1. As a result, the VDD of our InSe FETs is scaled down to 0.5 V while still being able to switch the channel, with the current from 100 nA μm−1 (off state) to over 1 mA μm−1 (on state), which is impossible for Si single-sheet MOS FETs (in which the ultimate VDD predicted by the IRDS is 0.6 V for the 0.5-nm technology node in 2037; Fig. 3f). Furthermore, the gate delay and EDP, two key device parameters proposed by Intel, are used here to assess the potential of our InSe transistors for constructing good logic ICs. Benefitting from the ultralow voltage of 0.5 V and considerable on-state currents exceeding 1 mA μm−1, our InSe FETs exhibit a better scaling trend for the delay and EDPs (overlap-free structure) than that of silicon counterparts. The delay of our best 10-nm-gate-length InSe FET is 0.32 ps (ksp = 2.5) and 0.87 ps (ksp = 13), which is better than the predicted final delay of Si FET (1.32 ps, 12 nm gate length) by IRDS 2022 (Fig. 3g). Moreover, the 10-nm-gate-length InSe FETs exhibit EDPs as low as 4.32 × 10−29 Js μm−1 (ksp = 2.5) and 3.20 × 10−28 Js μm−1 (ksp = 13), which are much smaller than the predicted limit for Si FETs1,32,37 (Fig. 3h). In Extended Data Fig. 7, we propose a self-aligned double-gate structure with the low-k inner spacer that is compatible with the Y-doping ohmic-contact method discussed earlier. On the other hand, a high-k spacer or doping of the ungated extension region could increase the density of the carriers at the extension surfaces and thus decrease the extension resistance. However, for actual applications, the high-k spacer could induce considerable parasitic capacitance.

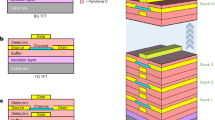

Typical transfer characteristics of our 10-nm InSe FET show ideal switching behaviour (Fig. 4a), including a SS of 75 mV per decade, a DIBL of 22 mV V−1 and a current on/off ratio of more than seven orders of magnitude. The off-state leakage current of the 10-nm InSe FET is less than 1 nA μm−1, which meets the requirement for commercial-standard-performance ICs. The photoluminescence spectrum of the 2D InSe and the gate-leakage currents of devices are shown in Supplementary Figs. 7 and 8. More transfer characteristics of ballistic 2D InSe FETs with 10-nm and 20-nm gate lengths of our device are shown in Extended Data Fig. 8 and a typical hysteresis of our device is shown in Supplementary Fig. 9. The scaling trend of SS and DIBL of our InSe FETs (Fig. 4b,c) are compared with those of the state-of-the-art silicon FETs (brown dots for IBM and aquamarine blue dots for Intel) and the theoretical simulation of silicon FETs (dashed black line)32,37,38. Some of our 10-nm FETs show better SS (75 mV per decade versus more than 90 mV per decade) and DIBL (22 mV V−1 versus more than 100 mV V−1). The larger bottom-Fin width is the bottleneck degrading the electrostatics of silicon FinFETs (Fig. 4c,d). By contrast, three-layer 2D InSe channels with a uniform thickness of 2.4 nm exhibit DIBLs far lower than 50 mV V−1 (red stars in Fig. 4c), even in 10-nm-gate-length FETs (10-nm gate length corresponds to the sub-5-nm nodes defined for silicon FETs). Generally, sub-50-mV-V−1 DIBL is a prerequisite to work at an ultralow voltage of 0.5 V. Furthermore, the simulation predicts that, by thinning the 2D channel from three layers to a single layer, the SS of 10-nm-gate-length 2D FETs could be further reduced to 65 mV per decade and the DIBL to 17 mV V−1 (ref. 39) (dashed pink line in Fig. 4b,c), providing plenty of room for further optimization of the off-state leakage current. It should be noted, however, that monolayer InSe is sensitive to moisture and may degrade to some extent in the air (Extended Data Fig. 8c,d). Besides, the relatively weak relationship between SS and temperature verifies that the direct source-drain tunnelling only slightly affects our ballistic 10-nm InSe FET39 (Fig. 2e and Supplementary Fig. 10). For sub-5-nm FETs, transition-metal dichalcogenides with larger effective carrier masses (for example, MoS2) will be a better choice to suppress direct source-drain tunnelling, but with smaller ballistic injection velocity than that of InSe channels. We further investigated three structures, single back gate, single top gate and double gate (Extended Data Fig. 9), and our results show that the double-gate structure is much more effective at suppressing the short-channel effect than the single-gate structure26. Also, the top-gate stacks of HfO2/Ti/Au in our devices can effectively isolate the InSe channel from moisture (Extended Data Fig. 10), making our devices perform better and be more stable than the previously reported back-gate InSe transistors.

a, Transfer characteristics of a typical 2D InSe FET with 10-nm gate length at drain bias VDS = 0.1 V (purple) and 0.5 V (blue). b,c, Scaling trends of SS and DIBL. The red stars represent our 10-nm-gate-length and 20-nm-gate-length ballistic InSe FETs (five typical devices respectively for each gate length; Extended Data Fig. 8). The aquamarine blue dots represent the Intel 10-nm-node, 14-nm-node and 22-nm-node FinFETs. The brown dots represent the 7-nm-node FinFET developed jointly by GlobalFoundries (GF) and IBM32,37,38. The dashed pink and black lines represent the theoretically calculated performance of monolayer 2D FETs39 and silicon FinFETs, respectively. d, Cross-section schematics of a typical 10-nm-node silicon FinFET and 2D FET. Light blue and gold represent the oxide and gate electrodes, respectively. e, Typical transfer characteristics of three ballistic 2D InSe FETs with 20-nm LG and the reported best-switching sub-50-nm 2D FET8,12,23,24,25,26,28,40. The highest saturation current of our devices is 1.35 mA μm−1 (red). f, SS versus ID of our ballistic 2D InSe FETs compared with other sub-50-nm short-channel 2D FETs. The solid dots denote three typical ballistic 2D InSe FETs, whereas the hollow dots denote other sub-50-nm 2D FETs8,12,23,24,25,26.

Figure 4e shows transfer characteristics for three typical ballistic InSe FETs with LG = 20 nm, exhibiting a large saturation-state current of 1.35 mA μm−1, a large current on/off ratio of 108 and an ideal SS with an average value of nearly 60 mV per decade across more than three orders of current magnitude, and these data are compared with those of the reported best-switching sub-50-nm 2D FETs8,12,23,24,25,26,28,40. Calibrating with 100 nA μm−1 as the off-state current and 1 mA μm−1 as the on-state current, a 0.5-V voltage window across the transfer characteristics is needed for our InSe FETs. This is compared with the supply-voltage window of larger than 3 V for other 2D FETs. Further, our ballistic InSe FETs have a steeper SS at a much larger magnitude of ID compared with other reported 2D FETs8,12,23,24,25,26 (Fig. 4f and Supplementary Fig. 11). The realization of ohmic contact not only contributes to large on-state current and large transconductance but is also an easily overlooked prerequisite to achieving ideal switching characteristics in the near-threshold region.

In summary, extremely scaled high-performance InSe FETs with ohmic contact, high gate efficiency and near-ideal ballistic ratio have been fabricated and shown to work at an ultralow voltage of 0.5 V. This work confirms for the first time that 2D FETs can deliver actual performance close to that of theoretical prediction and are strong competitors for silicon FETs at the Å node of the future.

Methods

Scale length and thermal velocity

Figure 1a shows that transistors with common 1–3 layers 2D materials as the channels all have a scale length smaller than 3 nm (refs. 19,41,42), thereby having better gate controllability than Si FETs (the mobility degradation owing to thickness-fluctuation-induced scattering limits the Si channel thickness scaling at 5 nm (ref. 43), corresponding to a scale length of 4.2 nm and minimum gate length of 12 nm). The second key parameter is thermal velocity, which is defined as44

in which k is the Boltzmann constant, T is temperature and m* is the effective carrier mass and is the only material parameter here. Three-layer indium selenide (InSe, with a lattice structure as shown in Extended Data Fig. 1) has a small theoretically effective mass of 0.17m0 (ref. 45) and thus a large thermal velocity of 1.34 × 107 cm s−1, exceeding that of the intrinsic (non-strained) silicon (m* = 0.19m0, vT = 1.26 × 107 cm s−1).

Device fabrication

A highly doped silicon substrate was cleaned for 20 s with a buffered oxide etch solution to remove oxidized layers and organic contaminants and then rinsed with deionized water. Then, the substrate was quickly taken into a chamber for atomic layer deposition. Atomic layer deposition (BeneQ TFS 200) of 2.6-nm-thick back-gate HfO2 on the substrate was performed at 230 °C with a growth rate of 0.98 Å per cycle. The 5/40-nm-thick Ti/Au mark was made by the process of electron-beam lithography (EBL)/electron-beam evaporation (EBE)/lift-off. Furthermore, few-layer InSe nanosheets (Extended Data Fig. 1) were mechanically exfoliated from bulk InSe single crystals and transferred to the prepared substrates using 3M Scotch Tape2,46,47,48,49, and the substrates were pretreated with low-power oxygen plasma for 2 min. Double EBL/EBE/lift-off was adopted to form the source and drain contacts respectively and to achieve approximately 10-nm gaps to define the channel length50. A 1/5/7-nm-thick Y/Ti/Au film stack was used as a contact for ballistic InSe FETs. Before evaporation, the contact area was treated with a low-power argon plasma to modify the interface, making the solid-dopant source of the reactive metal Y easier to inject. Then, after annealing at 230 °C for 30 min in an inert gas environment, the solid-dopant-source yttrium tends to diffuse into the top-layer InSe, causing the substitution activation of dopant Y atoms at the active sites (induced by the previous process of plasma). The InSe was then etched into a banded structure using a hardmask. Atomic layer deposition of 2.6-nm-thick top-gate HfO2 on the device was performed at 150 °C with a growth rate of 1.21 Å per cycle by first depositing a few layers of Al atoms and then oxidizing it into about 0.3–0.4 nm Al2O3 as the seed layer. Furthermore, EBL/EBE/lift-off was adopted to form the top-gate metal of Ti/Au. Finally, a thin layer of top HfO2 on the pad was etched through a polymethyl methacrylate (PMMA)-defined pattern. Hydrogen silsesquioxane (2%) defined the pattern through EBL and solidified it into 60-nm-thick SiO2, which was placed under the wires and pads to reduce the leakage of the back gate. A 5/70-nm Ti/Au film was used as wires and pads by the EBL/EBE/lift-off process. To avoid oxidation and degradation of the sample, most of the process was carried out under a vacuum or inert gas environment and completed as quickly as possible. The schematic diagram of the preparation process is shown in Extended Data Fig. 1. This self-aligned phase-transition method for fabricating ohmic contacts is also compatible with advanced-node complementary metal–oxide–semiconductor (CMOS) processes.

As an environmentally sensitive 2D semiconductor, the stability of InSe should be given special attention during the processing of FETs. In our InSe FETs fabrication flow, to avoid the degradation of 2D InSe in the environment and the EBL process, we have also made some improvements as follows.

First, the main cause of degradation of atomically thin InSe semiconductors is because of the reaction with moisture and oxygen when exposed to the environment. Fortunately, previous reports give us a guide that the encapsulation isolated from the moisture can effectively slow down the degradation process45,51,52,53. So once the top-gate stack and gate metal are deposited, the channel avoids moisture and oxygen and the device remains stable, as shown by the measured results in Extended Data Fig. 10. Therefore, the process before top-gate preparation is critical for the stability of atomically thin InSe. The high-quality bulk InSe material is rapidly encapsulated and stored in an inert gas environment after growth and the subsequent transfer and positioning processes are also carried out in an inert gas in the glove box.

Second, it is necessary to adopt a method compatible with photo-beam or electron-beam lithography for the fabrication of InSe 2D transistors. We found that the baking PMMA process is critical before the EBL process, which is an important factor for degradation but has been ignored by previous reports because the approximately 170–180 °C baking in the air on the hot plane was usually done. Therefore, to minimize the impact of PMMA and electron-beam exposure on InSe contact, the baking temperature of the PMMA resistance is a key parameter to be set at a lower temperature of 110 °C (conventionally 170–180 °C) at 3 min in a vacuum tube furnace and quickly placed in a high-vacuum environment (1 × 10−8 torr) for 8 h to wait for the solvent to evaporate. EBL (Raith Voyager) is used for patterning, with a system chamber vacuum of 1 × 10−6 mbar. The contact areas are exposed using a minimum beam current of 220 pA in the system to minimize the impact of the electron beam on the InSe electronic contacts. Although the areal dose is fixed to expose a given e-beam resist, the level of resist (PMMA) heating to affect the depolymerization is dependent on the EBL current level54. This heating is greater for higher EBL currents54, resulting in the resist being more likely to produce free radicals that get trapped between the contact and the resist, thus degrading contact resistance and stability. Then, the following electron-beam evaporation deposition of metals is also carried out in a high vacuum of 10−8 torr.

As shown in Extended Data Fig. 10, after the top gate is prepared, the high-k dielectric layer and the metal can be used as a passivation layer to effectively isolate moisture and oxygen from the environment and improve its stability. Moreover, there is only 8.5% performance degradation even after annealing at 250 °C for 1 h (Extended Data Fig. 10).

Characterization and measurements

SEM imaging was performed using a Zeiss Sigma 300 SEM (Extended Data Fig. 1). The thickness of the as-exfoliated few-layer material was determined by atomic force microscopy (Veeco Instruments Inc., Dimension lcon). Atomic force microscopy was carried out in tapping mode and the resonant frequency was about 300 kHz. The cross-section STEM images were obtained using a high-resolution spherical aberration correction transmission electron microscope (JEOL ARM200F). The transmission electron microscopy slice samples with devices are cut from our chips using a dual-beam focused ion beam system and the lamella samples were transferred to a transmission electron microscopy grid by OmniProbe 200 nanomanipulators. Electrical characterization was carried out under a vacuum of about 1.3 × 10−3 mbar in the Lake Shore vacuum low-temperature probe station and using a Keithley 4200A Parameter Analyzer. A wet etching process was used to remove the capping yttrium layer before measuring the Y-InSe channel FET, to eliminate the shunting effect from the yttrium metal layer on top. In Fig. 1h, Y-InSe channel devices show weak gate modulation owing to the semimetallic nature of the channel, which directly confirms that the plasma-assisted Y-doping method can induce phase transition of 2D InSe.

Extraction of contact resistance

In a ballistic FET, the source and drain contacts account for most of the total resistance of the FET, so we directly extract the total resistance as the upper limit of the total contact resistance 2Rc for our InSe FETs from the low-field slopes of the saturation output characteristics, as shown in Fig. 2b. The minimum total resistance extracted from our ballistic devices is 124 Ω μm (corresponding to a Rc lower than 62 Ω μm; Fig. 1j), which is much lower than those of other reported 2D short-channel FETs and, more importantly, this value meets the requirements of 2RC for 2037 proposed by the IRDS. It is worth noting that, as the conduction band approaches the Fermi level, the band movement is slowed down by the quantum capacitance, and it is difficult to accurately extract Schottky-barrier heights using the widely used variable-temperature Arrhenius method, especially when the Schottky-barrier height is below a certain value (for example, lower than 3 kT or 78 meV).

Relation between ballistic on-state current and thermal velocity

In 2D ballistic transistors, the current is generally expressed as

Here W is the channel width, \(q{n}_{{\rm{s}}}={C}_{{\rm{G}}}\left({V}_{{\rm{GS}}}-{V}_{{\rm{T}}}\right)\) is the carrier’s density in the channel, \({\eta }_{{\rm{F}}}=\frac{{E}_{{\rm{FS}}}-{\varepsilon }_{{\rm{top}}}}{kT}\) is the location of the Fermi level, which is determined by the carrier’s density induced by the gate and F1/2(η) and F0(η) are the Fermi–Dirac integrals of 1/2 and 0 orders, respectively. Further, \({v}_{{\rm{T}}0}=\sqrt{\frac{2{k}_{{\rm{B}}}T}{\pi {m}^{* }}}\), is the so-called non-degenerate thermal velocity. When the drain voltage is high enough, the factor in the square brackets becomes unity and the current saturates as

This equation shows that the ballistic on-state current is determined by both the thermal velocity and the gate efficiency55.

Landauer formula

The Landauer formula for the current can be written as

T(E) = 1 when ballistic transport is assumed. The Fermi function of the source and drain reservoir is

For 2D InSe, the number of modes M(E) has the formula

in which W is the width of the device, gv denotes the valley degeneracy, EC is the conduction band minimum, m* (0.17m0) is the effective mass, ħ is the reduced Plank constant and H(E − EC) is the Heaviside step function. Because our devices are fabricated with ohmic contact and 10-nm ballistic channel, the gap between our experimental contact resistance value and the quantum limit is indeed very small and could be attributed to the limited channel scattering (considering that the ballistic ratio is not 100%) and measurement error and noise.

Calculation of the intrinsic delays and EDPs

The intrinsic gate delay and EDP are key parameters commonly used to characterize CMOS and the intrinsic gate delay is defined as56

in which V = VDD is the supplied voltage of operation and I is the on-state current. C is the total gate capacitance57, such that

in which COX is the double-gate capacitance of the dielectric layer, CQ is the quantum capacitance and the quantum capacitance of three-layer InSe FETs is shown in Extended Data Fig. 4.

Limited by the area of mechanically exfoliated thin-layer 2D InSe, the exact capacitance value of the as-prepared metal–oxide 2D structure is extremely difficult to obtain directly (it is beyond the accuracy of our parameter analyser). Instead, we use the metal–insulator–metal structure to measure directly the oxide capacitance COX and the calculated quantum capacitance CQ of 2D InSe to obtain the channel capacitance (C = CQCOX/(CQ + COX)) of our InSe FETs. The intrinsic channel capacitance is calculated in two steps: (1) we fabricated 30 metal–insulator–metal structure samples (as shown in Extended Data Fig. 4a–c) with the same dielectrics stacks structure and the same fabrication process as our InSe double-gate FETs and then performed capacitance–voltage measurements to accurately determine the top-gate and back-gate capacitance values (Extended Data Fig. 4d–k). The variable-frequency capacitance–voltage characteristics show that the back-gate and top-gate capacitances are almost independent of frequency (varying from 10 kHz to 1 MHz), as shown in Extended Data Fig. 4d,h, and the hysteresis-free capacitance–voltage characteristics (Extended Data Fig. 4e,i) confirm the high quality of our gate stacks. Here we use the measured statistical average capacitance density value (3.5 μF cm−2) of 30 top-gate devices and 30 back-gate devices as the gate dielectric capacitance of our InSe FETs. (2) We calculated the quantum capacitance density CQ ≈ 6.6 μF cm−2 in the ballistic saturation region at VDS = 0.5 V as in Extended Data Fig. 4l (which is about half of the quantum capacitance of approximately 12.2 μF cm−2 in the linear region). This quantum capacitance is serial with the dielectric capacitance of 3.5 μF cm−2 in an InSe FET. Therefore, for our 10-nm-channel InSe FET, the top-gate and back-gate capacitances are 0.26 fF μm−1 from TCAD simulation, which contains the fringing field of the top gate and 0.35 fF μm−1 (Cox0,BG × LCH = 3.5 μF cm−2 × 10 nm), respectively, and thus the intrinsic total gate capacitance is calculated as 0.317 fF μm−1 ((CTG + CBG) || (CQ × LCH) = (0.26 fF μm−1 + 0.35 fF μm−1) || (6.6 μF cm−2 × 10 nm), in which || denotes capacitance in series), which is adopted to derive the intrinsic delay and intrinsic EDP. Furthermore, the intrinsic total gate capacitance is similar to that of the silicon FETs (0.44 fF μm−1 for 3-nm node in 2022, 0.37 fF μm−1 for 0.5-nm node in 2037, IRDS 2022). Therefore, Fig. 3 directly shows the potential advantages of 2D materials.

The EDPs formula is as follows56,57

in which V = VDD is the supplied voltage of operation, I is the on-state current and C is the total gate capacitance.

DFT calculations

-

1.

The stability of each doped or adsorption configuration is examined by calculating the formation energy. For doped structures, the formation energy is

$${E}_{{\rm{form}}}={E}_{{\rm{doped-mInSe}}}-{E}_{{\rm{mInSe}}}+\sum {n}_{i}{\mu }_{i}$$(10)Edoped-mInSe and EmInSe are the total energies of the doped-mInSe and the pristine mInSe, respectively, and ni and μi are the number of atoms i removed (+1) or added (−1) and the corresponding chemical potential, respectively. For adsorption structures, the formation energy is

$${E}_{{\rm{form}}}={E}_{{\rm{adsorp-mInSe}}}-{E}_{{\rm{mInSe}}}-{n}_{i}{E}_{{\rm{Y-bulk}}}$$(11)Eadsorp-mInSe and EmInSe are the total energies of the adsorbed-mInSe and the pristine mInSe, respectively, and ni and EY-bulk are the number of atoms i added (+1) and the energy per atom of bulk yttrium. Here we use 2 × 2 × 1 bilayer InSe cell and one yttrium atom in the doped or adsorption systems.

-

2.

We use DFT with the projector augmented wave method built in the Vienna Ab initio Simulation Package to perform geometry optimization and electronic-structure calculations. The k-point mesh for the relaxation and single-point calculation was sampled using the Monkhorst–Pack method with a mesh of 0.04 and 0.02 Å−1 in the Brillouin zone. A plane-wave basis set with a 500-eV cut-off energy is used. The electronic self-consistent iteration is converged until the energy difference is smaller than 10−5 eV and atomic positions optimization is obtained until the forces are lower than 0.01 eV Å−1. We also take van der Waals interactions into consideration, so the DFT-D3 method is adopted. With the periodic boundary condition existing in the vertical direction, the dipole correction is implemented to eliminate the pseudo interaction.

Virtual Source Model

In the Virtual Source Model (MIT)58,59,60,61, the drain current is calculated by a product of the mobile charge density and the carrier average velocity along the channel. The Virtual Source Model uses a gradual channel approximation and calculates the drain current as

in which W is the device width, Qx0 is the charge density at the virtual source, vx0 is the virtual source injection velocity at the top of the barrier, Fsat denotes the empirical transition function and β is a fitting parameter.

When the device is under low VDS, the charge density at the top of the barrier is

in which kB is the Boltzmann constant, T is the temperature, ħ is the reduced Planck’s constant, N2D is the effective density of states of the 2D channel, Efs/fd is the Fermi level at the source/drain contact, which are, under small bias, nearly the same, Ec is the first subband energy of the 2D channel and ψs is the surface potential. The surface potential ψs can be calculated as

in which αG = Cg/CΣ, αD = Cd/CΣ, αS = Cs/CΣ and CΣ = Cg + Cd + Cs. VG, VD and VS represent the voltages of the gate, drain and source terminal, respectively. Cg, Cd and Cs denote the gate capacitance, drain capacitance and source capacitance, respectively.

When the FET operates under a large VDS, the device is in a non-equilibrium state and the charge density becomes

in which TL is the Landauer transmission coefficient and Ns/d is the electron density from the source and drain reservoir, respectively. The intrinsic bias is calculated by

in which Rc is the source/drain contact resistance, VDS (VDS′) and VGS (VGS′) are the intrinsic (extrinsic) drain voltage and the gate voltage, respectively. We can extract the virtual source injection velocity vx0 by fitting Virtual Source Model to the output characteristics of our InSe FETs.

Also, the generalized expression for degenerate thermal velocity vT (considering the carriers’ degeneracy) is

in which \({v}_{{\rm{T}}0}=\sqrt{\frac{2kT}{\pi {m}^{* }}}\) denotes the non-degenerate thermal velocity and F1/2(ηfs) is the Fermi–Dirac integral of order 1/2 (refs. 59,60,61).

The main fitting parameters of the Virtual Source Model for the 10-nm InSe FET are: Cox = 0.07 F m−2, meff = 0.17m0, DIBL = 0.02 V V−1, VT0 = 0.75 V, n0 = 1.2, εch = 6, vx0 = 1.77 × 107 cm s−1 and vT = 2.14 × 107 cm s−1. For the 20-nm-gate-length device, the main fitting results are: Cox = 0.07 F m−2, meff = 0.17m0, DIBL = 0.02 V V−1, VT0 = 0.62 V, n0 = 1.2, εch = 6, vx0 = 1.55 × 107 cm s−1 and vT = 2.07 × 107 cm s−1, in which Cox is the gate insulator capacitance, meff is the effective mass of the InSe channel, VT0 is the threshold voltage, n0 is the SS factor, εch is the dielectric constant, vx0 is the virtual source injection velocity and vT is the degenerate thermal velocity (considering the carriers’ degeneracy). The fitting output curves are shown in Extended Data Fig. 6 and the calculated BSAT = vx0/vT for 10-nm-gate-length and 20-nm-gate-length 2D InSe transistors are 83% and 75%, respectively.

Thermal emission and thermal field emission

Although previous studies on 2D FETs have also shown that they can reach the thermionic limit of 60 mV per decade, the near-60-mV-per-decade region often appears at the deep off-state current region (typically lower than 1 nA μm−1; Fig. 4f), which contributes little to the whole gate-switching range. This may be caused by the insufficient gate efficiency or poor interface in gate stacks of 2D FETs and—most importantly—the existence of large Schottky barriers in some of these contacts. The subthreshold regions on the transfer characteristics of those Schottky FETs can be divided into two segments, corresponding to thermal emission and thermal field emission. When the middle-channel potential is higher than the Schottky barrier, the channel is in deep off state and the leakage current is dominated by thermal emission (usually smaller than 1 nA μm−1), and the corresponding SS is close to 60 mV per decade. On the other hand, when the middle-channel potential is lower than the Schottky barrier, the current is mainly contributed by thermal field emission, and the gate opens the channel by squeezing the width of the Schottky barrier and increasing tunnelling probability62,63, which severely degrades the equivalent gate efficiency and causes a large SS in the near-threshold region.

Three structures of ballistic InSe FETs

We simulated the electrical transport of three structures of a single-back-gate transistor, a single-top-gate transistor and a double-gate transistor, all of which are set with heavy doping ohmic contact (Extended Data Fig. 9). As expected, the double-gate transistor gives the best field modulation with the highest on-state current and smallest SS among the three structures. The single-back-gate FET has slightly better on-state current than that of the single-top-gate FET with the doping contact. On the other hand, the single-back-gate transistor shows a better SS than the single-top-gate transistor. This can be understood that the added spacer width could benefit the actual gate modulation for the back-gate structure.

Second, we fabricated the new InSe FETs in the experiment with the single-top-gate structure and single-back-gate structure and then added the extra top gate to construct the double-gate structure. Our measured electrical characteristics have a similar trend with the simulation results: the double-gate structure has the best on–off state behaviour and the single-back-gate structure has a better off behaviour than that of the single top gate.

To further explore the exact difference between the single-gate and the double-gate structures, during the preparation of new double-gate devices, we add a middle step to measure the characteristic of the single-back-gate structure and the SEM images before or after the top gate are shown in Extended Data Fig. 9d. This classic comparative study method is also used in comparing the on–off behaviour between the double-gate and single-gate WS2 FETs26,64. The transfer characteristics comparison between the single-gate and double-gate devices is shown in Extended Data Fig. 9e–h, corresponding to four sets of devices (including two 10-nm-channel FETs and two 20-nm-channel FETs). Our measurement shows that the double-gate FETs boost by about a third the on-state current compared with the single-back-gate FET, and the SS of the double-gate FETs is pushed close to the theoretical limit (10 nm about 78 mV per decade and 20 nm about 63 mV per decade). This is consistent with the trend of simulation that the double-gate structure is much more effective at suppressing the short-channel effect than the single back gate.

Engineering challenges

Leading industrial semiconductor companies and research institutions, such as Intel65, Taiwan Semiconductor Manufacturing Company66, Samsung Advanced Institute of Technology67 and Interuniversity Microelectronics Centre68, have invested in detailed research on 2D integrated electronics. However, engineering challenges remain and potential solutions are being explored. These include the synthesis of wafer-scale high-quality 2D material (although chemical vapour deposition InSe has been reported69, it remains challenging to realize controlled synthesis of high-quality wafer-scale InSe single crystals), shrinking the contact lengths of 2D FETs to less than 20 nm (different from one-dimension carbon nanotube FETs, 2D FETs have been proved to have better contact-length scaling behaviour and thus smaller contact pitch70), achieving complementary p-type 2D FETs with comparable performance71 (through, for example, the scheme depicted in Supplementary Fig. 12), CMOS-compatible fabrication process for 2D-materials-based 3D-structure transistors (such as multibridge-channel transistors; Supplementary Fig. 13).

Data availability

The data that support the findings of this study are available from the corresponding author on reasonable request.

References

IEEE International Roadmap for Devices and Systems. https://irds.ieee.org/editions (2022).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Radisavljevic, B., Radenovic, A., Brivio, J. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99 (2016).

Quhe, R. et al. Sub-10 nm two-dimensional transistors: theory and experiment. Phys. Rep. 938, 1–72 (2021).

Liu, L., Yang, L. & Guo, J. On monolayer MoS2 field-effect transistors at the scaling limit. IEEE Trans. Electron Devices 60, 4133–4139 (2013).

Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS2 transistors be? Nano Lett. 11, 3768–3773 (2011).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Cho, S. et al. Phase patterning for ohmic homojunction contact in MoTe2. Science 349, 625–628 (2015).

McDonnell, S. et al. Defect-dominated doping and contact resistance in MoS2. ACS Nano 8, 2880–2888 (2014).

Gilardi, C. et al. Extended scale length theory for low-dimensional field-effect transistors. IEEE Trans. Electron Devices 69, 5302–5309 (2022).

Suryavanshi, S. V., English, C. D., Wong, H.-S. P. & Pop, E. Scaling theory of two-dimensional field effect transistors. Preprint at https://arxiv.org/abs/2105.10791 (2021).

Marin, E. G., Marian, D., Iannaccone, G. & Fiori, G. First-principles simulations of FETs based on two-dimensional InSe. IEEE Electron Device Lett. 39, 626–629 (2018).

Schauble, K. et al. Uncovering the effects of metal contacts on monolayer MoS2. ACS Nano 14, 14798–14808 (2020).

Zhu, J. et al. Argon plasma induced phase transition in monolayer MoS2. J. Am. Chem. Soc. 139, 10216–10219 (2017).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Nourbakhsh, A. et al. MoS2 field-effect transistor with sub-10 nm channel length. Nano Lett. 16, 7798–7806 (2016).

Yang, L., Lee, R., Rao, S., Tsai, W. & Ye, P. D. in Proc. 2015 73rd Annual Device Research Conference (DRC) 237–238 (IEEE, 2015).

Pang, C.-S., Wu, P., Appenzeller, J. & Chen, Z. Sub-1nm EOT WS2-FET with IDS > 600 μA/μm at VDS = 1V and SS < 70 mV/dec at LG = 40 nm. IEDM Tech. Digest. 3.4.1–3.4.4 (2020).

Li, X. et al. High-speed black phosphorus field-effect transistors approaching ballistic limit. Sci. Adv. 5, eaau3194 (2019).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Cheng, Z. et al. How to report and benchmark emerging field-effect transistors. Nat. Electron. 5, 416–423 (2022).

Javey, A. et al. Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Auth, C. et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. IEDM Tech. Digest 29.1.1–29.1.4 (2017).

Convertino, C. et al. InGaAs-on-insulator FinFETs with reduced off-current and record performance. IEDM Tech. Digest 39.2.1–39.2.4 (2018).

Jeon, J. et al. The first observation of shot noise characteristics in 10-nm scale MOSFETs. VLSI Tech. Digest 48–49 (2009).

Liow, T. et al. Carrier transport characteristics of sub-30 nm strained N-channel FinFETs featuring silicon-carbon source/drain regions and methods for further performance enhancement. IEDM Tech. Digest 1–4 (2006).

Barral, V. et al. Experimental determination of the channel backscattering coefficient on 10–70 nm-metal-gate double-gate transistors. Solid State Electron. 51, 537–542 (2007).

Natarajan, S. et al. A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. IEDM Tech. Digest 3.7.1–3.7.3 (2014).

Xie, R. et al. A 7nm FinFET technology featuring EUV patterning and dual strained high mobility channels. IEDM Tech. Digest 2.7.1–2.7.4 (2016).

Ahn, Y. & Shin, M. First-principles-based quantum transport simulations of monolayer indium selenide FETs in the ballistic limit. IEEE Trans. Electron Devices 64, 2129–2134 (2017).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Wang, Y. et al. Many-body effect and device performance limit of monolayer InSe. ACS Appl. Mater. Interfaces 10, 23344–23352 (2018).

Xu, L. et al. Computational study of ohmic contact at bilayer InSe-metal interfaces: implications for field-effect transistors. ACS Appl. Nano Mater. 2, 6898–6908 (2019).

Uchida, K., Koga, J. & Takagi, S. Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs - Coulomb scattering, volume inversion, and /spl delta/T/sub SOI/-induced scattering. IEDM Tech. Digest 33.5.1–33.5.4 (2003).

Ahmadi, M. T. et al. Current–voltage characteristics of a silicon nanowire transistor. Microelectron. J. 40, 547–549 (2009).

Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223–227 (2016).

Geim, A. K. Graphene: status and prospects. Science 324, 1530–1534 (2009).

Liu, Y., Huang, Y. & Duan, X. F. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Xie, L. et al. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv. Mater. 29, 1702522 (2017).

Liu, Y., Duan, X., Huang, Y. & Duan, X. Two-dimensional transistors beyond graphene and TMDCs. Chem. Soc. Rev. 47, 6388–6409 (2018).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

Ho, P. et al. High-mobility InSe transistors: the role of surface oxides. ACS Nano 11, 7362–7370 (2017).

Wells, S. A. et al. Suppressing ambient degradation of exfoliated InSe nanosheet devices via seeded atomic layer deposition encapsulation. Nano Lett. 18, 7876–7882 (2018).

Jiang, J. et al. Stable InSe transistors with high-field effect mobility for reliable nerve signal sensing. npj 2D Mater. Appl. 3, 29 (2019).

Kang, S., Movva, H. C. P., Sanne, A., Rai, A. & Banerjee, S. K. Influence of electron-beam lithography exposure current level on the transport characteristics of graphene field effect transistors. J. Appl. Phys. 119, 124502 (2016).

Arora, V. K. et al. High-field distribution and mobility in semiconductors. Jpn. J. Appl. Phys. 24, 537 (1985).

Chau, R. et al. Benchmarking nanotechnology for high-performance and low-power logic transistor applications. IEEE Trans. Nanotechnol. 4, 153–158 (2005).

Zhang, Z. Y. et al. High-performance n-type carbon nanotube field-effect transistors with estimated sub-10-ps gate delay. Appl. Phys. Lett. 92, 133117 (2008).

Khakifirooz, A., Nayfeh, O. M. & Antoniadis, D. A simple semiempirical short-channel MOSFET current–voltage model continuous across all regions of operation and employing only physical parameters. IEEE Trans. Electron Devices 56, 1674–1680 (2009).

Lundstrom, M. S. & Antoniadis, D. A. Compact models and the physics of nanoscale FETs. IEEE Trans. Electron Devices 61, 225–233 (2014).

Liu, Y., Luisier, M., Antoniadis, D., Majumdar, A. & Lundstron, M. S. On the interpretation of the ballistic injection velocity in deeply scaled MOSFETs. IEEE Trans. Electron Devices 59, 994–1001 (2012).

Rahman, A. & Lundstrom, M. S. A compact scattering model for the nanoscale double-gate MOSFET. IEEE Trans. Electron Devices 49, 481–489 (2002).

Knoch, J. & Appenzeller, J. Impact of the channel thickness on the performance of Schottky barrier metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 81, 3082 (2002).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Sun, Z. et al. Statistical assessment of high-performance scaled double-gate transistors from monolayer WS2. ACS Nano 16, 14942–14950 (2022).

O’Brien, K. P. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. IEDM Tech. Digest 7.1.1–7.1.4 (2021).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. IEDM Tech. Digest 7.2.1–7.2.4 (2021).

Sohn, A. et al. Precise layer control and electronic state modulation of a transition metal dichalcogenide via phase-transition-induced growth. Adv. Mater. 34, 2103286 (2022).

Asselberghs, I. et al. Wafer-scale integration of double gated WS2-transistors in 300mm Si CMOS fab. IEDM Tech. Digest 40.2.1–40.2.4 (2020).

Chang, H. et al. Synthesis of large-area InSe monolayers by chemical vapor deposition. Small 14, 1802351 (2018).

Arutchelvan, G. et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 11, 6610 (2021).

Su, S. K. et al. Layered semiconducting 2D materials for future transistor applications. Small Struct. 2, 2000103 (2021).

Smithe, K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS2. Nano Lett. 18, 4516–4522 (2018).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Chou, A. S. et al. High on-state current in chemical vapor deposited monolayer MoS2 nFETs with Sn ohmic contacts. IEEE Electron Device Lett. 42, 272–275 (2020).

Patel, K. A., Grady, R. W., Smithe, K. K. H., Pop, E. & Sordan, R. Ultra-scaled MoS2 transistors and circuits fabricated without nanolithography. 2D Mater. 7, 015018 (2020).

Datta, S. Electronic Transport in Mesoscopic Systems Ch. 2 (Cambridge Univ. Press, 1995).

Xia, F. et al. The origins and limits of metal–graphene junction resistance. Nat. Nanotechnol. 6, 179–184 (2011).

Agarwal, T. et al. Benchmarking of MoS2 FETs with multigate Si-FET options for 5 nm and beyond. IEEE Trans. Electron Devices 62, 4051–4056 (2015).

Acknowledgements

Funding for this work was provided by the National Key Research & Development Program of China (grant no. 2021YFA0717400) and the National Science Foundation of China (grant nos. 61888102, 61971009 and 62122006). We thank L.G. and F.M. (Institute of Physics, Chinese Academy of Sciences) for focused ion beam and STEM technique support.

Author information

Authors and Affiliations

Contributions

C.Q. and L.-M.P. proposed and supervised the project. J.J., C.Q. and L.-M.P. conceived the idea and designed the experiment. J.J. performed InSe material characterization, device fabrication and device characterization. L.X. provided the calculations and simulations based on DFT theory, TCAD models and compact models. J.J., C.Q., L.X. and L.-M.P. analysed the experimental and modelling results. J.J., C.Q., L.-M.P. and L.X. cowrote the manuscript. All authors commented on and discussed this work.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks Peng Wu, Zhixian Zhou and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data figures and tables

Extended Data Fig. 1 Structure characterization and schematic process flow of ballistic InSe FETs.

a, STEM image showing a top view of the atomic structure of few-layer InSe and corresponding selected electron diffraction pattern taken from the same InSe region. Scale bar, 2 nm. Inset, atomic structures of 2D InSe. Our InSe sample has an excellent crystal structure and an expected hexagonal lattice spacing of 3.4 Å without visible defects. b, Top-view SEM images of ballistic InSe FETs. Scale bar, 400 nm. c, Schematic process flow and structure of ballistic InSe FETs.

Extended Data Fig. 2 Benchmarking ID versus ns and TLM.

a, Benchmarking ID versus ns at VDS = 0.5 V (refs. 29,71,72,73,74,75). The numbers in parentheses is the channel length (nm). b, SEM image of a set of devices for TLM. c, Total resistance versus channel length, leading to a minimum value of 83 Ω μm. The fluctuation of resistances between different electrodes in the long channels leads to some inaccuracy in the extracted 2RC.

Extended Data Fig. 3 Comparison of transfer characteristics at various temperatures and Landauer formula.

a, Transfer characteristics of a ballistic non-optimal Schottky-barrier 2D InSe FET at various temperatures ranging from 300 to 100 K. b, Transfer characteristics of a ballistic ohmic-contact 2D InSe FET at various temperatures ranging from 300 to 100 K. c, Comparison of transfer characteristics of a ballistic ohmic-contact InSe FET and a ballistic non-optimal Schottky-barrier InSe FET at VDS = 0.3 V at 100 K. In a ballistic unoptimized Schottky-barrier InSe FET, the transfer curve exhibits two slopes below the threshold at low temperature. The lower part is exclusively thermionic emission (TE) current corresponding to carriers over the potential barrier, which is dominated by the channel. The upper part consists of thermionic emission and tunnelling current, also called thermal field emission (TFE). With an incremental change in VGS, the thermionic emission component changes only slightly owing to the Schottky-barrier effect. Also, the main increase in current is because of the tunnelling enhancement through squeezing the source Schottky barrier width and therefore exhibits a poor SS62,63. d, Experimental and theoretical total resistances in ballistic InSe transistors. The red stars are the experimental total resistance from typical output characteristics (Fig. 1j) and the black line is the calculated total resistance of the quantum limit by Landauer’s approach (related to the number of modes)76,77.

Extended Data Fig. 4 Capacitance–voltage characteristics and CQ simulation.

a,b, Optical and SEM images of our metal–insulator–metal (MIM) structure for capacitance–voltage (C–V) characteristics. c, Schematic diagram of the MIM structure. d, Typical as-measured back-gate multifrequency C–V curves; 19 frequency curves are measured between 10 kHz and 1 MHz. e, Typical back-gate C–V hysteresis curve at a frequency of 1 MHz. f, The back-gate capacitance versus f (10 kHz to 1 MHz) for VGS = 0.1, 0.3, 0.5 and 0.7 V. g, Thirty MIM curves of back-gate capacitance versus f (10 kHz to 1 MHz) at VGS = 0.5 V. h, Typical as-measured top-gate multifrequency C–V curves; 19 frequency curves are measured between 10 kHz and 1 MHz. i, Typical top-gate C–V hysteresis curve at a frequency of 1 MHz. j, The top-gate capacitance versus f (10 kHz to 1 MHz) for VGS = 0.1, 0.3, 0.5 and 0.7 V. k, Thirty MIM curves of top-gate capacitance versus f (10 kHz to 1 MHz) at VGS = 0.5 V. l, Simulated CQ versus VGS − VT, for a 10-nm InSe FET at VDS = 0 V and 0.5 V.

Extended Data Fig. 5 Transconductances of ballistic InSe FETs.

a, Transfer characteristics for ten typical ballistic InSe FETs at VDS = 0.5 V. The dashed line is the theoretically calculated transfer curve39. b, Corresponding transconductance of ten typical ballistic InSe FETs at VDS = 0.5 V. The best transconductance is 6 mS μm−1. Six FETs have transconductances exceeding 4 mS μm−1. The dashed line is the theoretically calculated transconductance39. c,d, Transfer curve and output of a typical ballistic InSe FET (with a transconductance of 6 mS μm−1). e, Transfer characteristics of a typical ballistic 2D InSe FET with 20-nm channel length at VDS = 0.1, 0.3, 0.5 and 0.7 V. f, Transfer characteristics comparison of ballistic 2D InSe FET at VDS = 0.5 and 0.7 V (coloured dots), 10-nm-node silicon FinFET (Intel, solid black line) and 20-nm-LG InGaAs FinFET normalized by state-of-the-art Fin Pitch = 34 nm (IBM, dashed black line). Note that all currents are normalized with the same rule. g, Transconductances comparison of typical ballistic 2D InSe FETs, a 10-nm-node silicon FinFET (Intel, solid black line) and an InGaAs FinFET (IBM, dashed black line). h, Transconductances comparison of ballistic 2D InSe FET at VDS = 0.5 and 0.7 V and other 2D FETs with sub-50-nm LG at VDD = 1 V. It shows that the transconductance of our InSe FETs at VDS = 0.7 V reaches 7 mS µm−1, which is larger than that of silicon FETs at the same bias voltage of VDS = 0.7 V but with slight degraded off-leakage current and subthreshold slope. The large transconductances of our 2D-InSe FETs benefit from several features of our FETs, including the ballistic channel with hardly any scatterings, higher thermal velocity, better source and drain contacts with negligible Schottky barriers and 2.6-nm-thick HfO2 double-gate structure.

Extended Data Fig. 6 Virtual Source Model fitting of output characteristics of InSe FETs.

Comparison of the Virtual Source Model fitting (hollow circles) and measured data (lines) for output characteristics of InSe FETs with LG = 10 nm (a) and LG = 20 nm (b). These results correspond to the red stars in Fig. 3e. To obtain an accurate Virtual Source Model fitting to extract the values of ballistic ratios, here a small gate voltage step of 0.1 V is used during output measurements.

Extended Data Fig. 7 Inner spacer structure and TCAD simulation.

a, Schematic diagram of a proposed process to achieve self-aligned (overlap-free) double-gate structure with low-k inner spacer and the process is compatible with the Y-doping ohmic contact. b,c, TCAD simulation of electron density distribution on the extension surfaces between the gate and the source/drain in ballistic InSe FETs with different k of the spacer. d, Schematic diagram of the ballistic InSe FETs with and without overlap from TCAD. e, The TCAD simulations of transfer curves of ballistic InSe FETs with (red) and without (black) overlap. f, On-state current density versus doping concentration of the ungated region below the spacer.

Extended Data Fig. 8 Transfer characteristics of typical ballistic InSe FETs and InSe thickness dependence of FET characteristics.

a, Transfer characteristics of five typical ballistic InSe FETs with LG = 10 nm, including SS and DIBL. b, Transfer characteristics of five typical ballistic InSe FETs with LG = 20 nm, including SS and DIBL. c, Typical AFM height profile of InSe samples, corresponding to 1, 3, 6, 13 and 22 layers. d, Dependence of the transfer characteristics of FETs on InSe channel thicknesses as in c. The reason for choosing the three-layer InSe channel material is that the monolayer InSe channel material has several basic limitations. (1) Monolayer InSe is more sensitive to the external environment and processing process than the three-layer InSe, so the on-state current and SS of the fabricated monolayer InSe FETs are degraded to some extent (Extended Data Fig. 8d). (2) The intrinsic electrical properties (thermal velocity etc.) of monolayer InSe are lower than those of the three-layer InSe channel (Fig. 1a) and, in addition, quantum-transport simulations also show that the transistors based on few-layer 2D semiconductors have higher on-state currents than those of monolayer 2D counterparts40,78.

Extended Data Fig. 9 Ballistic InSe FETs with single-top-gate, single-back-gate and dual-gate structures.

a,b, TCAD simulations of single-top-gate, single-back-gate and double-gate structures with 2.4-nm-thickness InSe channel and 10-nm gate length. The green transfer curve is the single-top-gate InSe FET, the blue transfer curve is the single-back-gate InSe FET and the red transfer curve is the dual-gate InSe FET. c, The experiment of the single-top-gate, the single-back-gate and the double-gate structures with 2.4-nm-thickness InSe channel and 20-nm channel length. The green transfer curve is the single-top-gate InSe FET, the blue transfer curve is the single-back-gate InSe FET and the red transfer curve is the dual-gate InSe FET. d, Top-view SEM images of ballistic InSe FETs with the single back gate (before top-gate fabrication) and the dual gate (after top-gate fabrication). e,f, The transfer characteristics of the typical ballistic 10-nm-channel-length InSe FETs with the single back gate (before top-gate fabrication, blue curves) and the dual gate (red curves). g,h, The transfer characteristics of the typical ballistic 20-nm-channel-length InSe FETs with the single back gate (before top-gate fabrication, blue curves) and the dual gate (red curves).

Extended Data Fig. 10 Electrical stability of ballistic 2D InSe FETs.

a, Transfer characteristics of a ballistic back-gate InSe FET without encapsulation in ambient conditions. b, Transfer characteristics of a ballistic double-gate InSe FET with top-gate encapsulation in ambient conditions. c, Transfer characteristics of a ballistic double-gate InSe FET before and after annealing at 250 °C for 1 h. LCH = 10 nm and VDS = 0.5 V. d, Output characteristics of the ballistic double-gate InSe FET before and after annealing at 250 °C for 1 h. LCH = 10 nm. Atomic thin InSe semiconductor is sensitive to moisture in the air and will suffer from a certain degree of degradation51,52,53. However, in previous reports, passivated InSe FETs encapsulated with hexagonal boron nitride45, a high-quality dry oxide51, high-k dielectric layer52 or PMMA53 show high stability and can be maintained for a long time. Here we adopt the double-gate structure, including HfO2/Ti/Au top-gate stacks. The high-k dielectric and top-gate metal covered on the InSe surface act as a passivation layer, which can effectively isolate moisture and oxygen in the air and improve the FETs’ stability.

Supplementary information

Supplementary Information

This file contains Supplementary Figures 1–13 and Supplementary References

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jiang, J., Xu, L., Qiu, C. et al. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023). https://doi.org/10.1038/s41586-023-05819-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-023-05819-w

- Springer Nature Limited

This article is cited by

-

3D integration of 2D electronics

Nature Reviews Electrical Engineering (2024)

-

Transistor engineering based on 2D materials in the post-silicon era

Nature Reviews Electrical Engineering (2024)

-

High-throughput approach to explore cold metals for electronic and thermoelectric devices

npj Computational Materials (2024)

-

The future of two-dimensional semiconductors beyond Moore’s law

Nature Nanotechnology (2024)

-

Tunable electronic and photoelectric properties of Janus group-III chalcogenide monolayers and based heterostructures

Scientific Reports (2024)