Abstract

Formation of a single crystalline oxide semiconductor on an insulating film as a channel material capable of three-dimensional (3D) stacking would enable 3D very-large-scale integration circuits. This study presents a technique for forming single-crystalline In2O3 having no grain boundaries in a channel formation region on an insulating film using the (001) plane of c-axis-aligned crystalline indium gallium zinc oxide as a seed. Vertical field-effect transistors using the single-crystalline In2O3 had an off-state current of 10−21 A μm−1 and electrical characteristics were improved compared with those using non-single-crystalline In2O3: the subthreshold slope was improved from 95.7 to 86.7 mV dec.−1, the threshold voltage showing normally-off characteristics (0.10 V) was obtained, the threshold voltage standard deviation was improved from 0.11 to 0.05 V, the on-state current was improved from 22.5 to 28.8 μA, and a 17-digit on/off ratio was obtained at 27 °C.

Similar content being viewed by others

Introduction

With the expansion of generative AI, which is computationally intensive, the hardware used for servers must have higher processing speeds. This raises the problem of large hardware power consumption and the need for power-saving measures1. Thus, hardware in the AI era should satisfy both the requirements concurrently: high processing speed and low power consumption2. To satisfy these requirements or solve a disadvantage of Neumann computing, a technique for shortening the distance between a memory device and an arithmetic unit such as Central Processing Unit (CPU) or Graphics Processing Unit (GPU) is required. In this regard, three-dimensional (3D) stacking using oxide semiconductors is a candidate technique3.

Oxide semiconductors, which can be formed at low temperatures, have been extensively reported as channel materials for displays and very-large-scale integration (VLSI) circuits4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35. In particular, c-axis-aligned crystalline indium gallium zinc oxide (CAAC-IGZO) has proven to be practical in driving transistors of displays for smartphones and augmented reality/virtual reality11. CAAC-IGZO is IGZO having c-axis alignment perpendicular to a formation surface and having no clear grain boundaries4,36,37. We have shown that the off-state current of CAAC-IGZO field-effect transistors (FETs) can be as small as 10−21A μm−1 at room temperature, indicating the potential of oxide semiconductors to meet the recent demand for power saving5,38,39. However, CAAC-IGZO still suffers from lower on-state current (Ion) relative to that of bulk Si and a disadvantage in application to LSI requiring high-speed processing.

Conversely, the Ion of amorphous or polycrystalline In2O3, an oxide semiconductor type, is comparable to that of low-temperature polysilicon-based transistors and is expected to become higher40,41,42,43,44,45,46,47,48. In2O3 is crystallized at low temperature, and the use of In2O3 in thin film transistors has been reported since 200745. In 2011, we proposed the applications of In2O3 to vertical transistors and LSI circuits10. Although polycrystalline In2O3 is expected to have higher Ion, polycrystalline In2O3 has grain boundaries that impede the reduction in characteristic variation compared with CAAC-IGZO. In this paper, we formed a prototype of a high-integration vertical transistor suitable for 3D VLSI using single-crystalline In2O3 in its channel region to reduce the variation in In2O3 characteristics. For the off-state current that is a key to lower power consumption, we examined whether the off-state current of single-crystalline In2O3 is as low as that of CAAC-IGZO. To meet the need for 3D stacking, both high processing speed and low power consumption can be achieved concurrently when characteristics variations and off-state current can be reduced by forming single-crystalline In2O3 on an insulating film.

Results

Challenges for forming single-crystalline In2O3

For single crystallization of In2O3, this involves reducing film impurities and reducing crystal nucleus density. To reduce impurities in films during the atomic layer deposition (ALD) of In2O349,50,51,52,53,54, particularly, the In precursor should be highly purified to a 6 N to 7 N level. To reduce the crystal nucleus density, eliminating crystal nuclei other than those used as In2O3 growth seeds is crucial. Additionally, selecting a seed suitable for bixbyite-type In2O3 growth is important.

Seed for crystallization

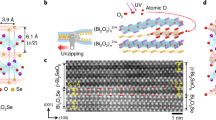

We consider that the use of a seed, which is the starting point of crystallization, with an appropriate orientation can facilitate single crystallization of In2O3. Epitaxial growth is possible55,56 owing to a small lattice mismatch between yttria-stabilized zirconia (YSZ) and In2O355. Figure 1a shows a STEM image of In2O3 formed by ALD on a single-crystalline YSZ (Cubic) (111) substrate, which has the same crystal structure as In2O3. As shown in Fig. 1a, we also successfully achieved single crystallization of In2O3 using a surface of the YSZ (111) substrate as a seed. However, since the method using the YSZ (111) substrate is not suitable for 3D stacking of VLSI, it is necessary to develop a method for forming single-crystalline In2O3 in the desired locations on an insulating film.

a Cross-sectional HAADF-STEM image of a sample where In2O3 is formed on a YSZ (111) substrate by ALD. b Cross-sectional TEM image with length measurements of a sample where In2O3 is formed on CAAC-IGZO by ALD. Both the CAAC-IGZO and In2O3 films were baked for 1 h at 400 °C in N2 atmosphere. A cube on the right side shows the crystal orientation.

In view of this, we examined the use of CAAC-IGZO instead of YSZ. Figure 1b shows a cross-sectional transmission electron microscopy (TEM) image of an In2O3 film formed on a CAAC-IGZO film by ALD, in which single-crystalline In2O3 {222} formed on the (001) plane of CAAC-IGZO can be observed. The interplanar spacing d222 of the In2O3 atomic layers stacked in the direction perpendicular to the (001) plane of CAAC-IGZO is 2.94 Å. The lattice spacing of IGZO in the vertical direction of Fig. 1b is 2.88 Å, which is almost equal to the interplanar spacing d222 of the In2O3 atomic layers. The lattice spacing of IGZO in the horizontal direction is 1.65 Å and the interplanar spacing d440 of the In2O3 atomic layers is 1.76 Å—a difference of approximately 6%.

Then, why the single crystallization on the CAAC-IGZO film can be achieved is described. Figure 2a shows the calculation results of the interface models by geometrical calculation57,58,59. Figure 2a compares the lattice mismatches and the bonding cross-sectional areas of super-cells where an In2O3 (Cubic, Ia\(\bar{3}\)) film is placed on the YSZ (111) substrate and the (001) plane of InGaZnO4 serving as the seeds. The lattice mismatch can be represented using Formula (1):

where \(\Delta\) represents the lattice mismatch (%), Lf represents the thin-film (In2O3) lattice constant, and Lb represents the base layer (YSZ or IGZO) lattice constant. In the case where the lattice mismatch differs depending on the crystal axis, lattice mismatch is shown for each case.

a Calculation of lattice mismatch between In2O3 and base layers, which are single-crystalline YSZ and InGaZnO4 serving as seeds for single crystallization of In2O3. To determine an interface with a high lattice match between different kinds of materials, super-cells having two planes (e.g., a combination of an In2O3 (001) plane and an IGZO (001) plane) forming the interface were newly set. The mismatch degree of lattice constants (a’, b’) and a bonding cross-sectional area at the interface of the super-cells are shown, respectively, as “Lattice mismatch” and “Cross-sectional area.” It is indicated that as the lattice mismatch and the bonding cross-sectional area decrease, the lattice match at the interface between the different kinds of materials increases. b Comparison of the energy of interfaces between amorphous In2O3 and each plane of single crystalline In2O3.

When the (001) or (111) plane of In2O3 is assumed to be formed on the (001) plane of IGZO (in this paper, IGZO belonging to a trigonal system is represented by a hexagonal lattice and denoted by (hkl) for describing lattice match with a cubic lattice), the lattice mismatch is 0.55%, which is lower than that with the YSZ (111) substrate, and the cross-sectional area is 179.3 Å2, which is very close to 184.3 Å2 of an assumed cross-sectional area between the (111) plane of In2O3 and the YSZ (111) substrate.

Figure 2b compares the energy of interfaces between amorphous In2O3 and each plane of single-crystalline In2O3 calculated by molecular dynamics calculation. The lowest interface energy is 1.92 (eV nm−2) at the (111) plane, which indicates that single crystallization of In2O3 is progressed such that the (111) plane surface area becomes the largest.

Figure 3 shows the atomic arrangement of IGZO and In2O3. Figure 3a shows the atomic arrangement of the single-crystalline IGZO seen in the direction perpendicular to the c-axis. IGZO has a natural cleavage plane between the GaZnO planes. Figure 3b shows the atomic arrangement of the single-crystalline IGZO seen in the c-axis direction, in which the nearest metal–metal distance is 3.30 Å. Figure 3c shows the atomic arrangement of the (111) plane of In2O3 seen from [111], in which the In–In distances are 3.34 to 3.36 Å. These distances are almost equal to the In–In distance of 3.30 Å in the single-crystalline IGZO. Furthermore, both single-crystalline IGZO and the (111) plane of In2O3 have three rotation axes and hexagonal atomic arrangements. As shown in Fig. 2a, the lattice mismatch and cross-sectional area between the (001) plane of In2O3 and the single-crystalline IGZO are large. This proves that the (001) plane of CAAC-IGZO has an atomic arrangement that can serve as a seed for the crystallization of the (111) plane of In2O3. Thus, as shown in Fig. 1b, the (111) plane of In2O3 (111) is crystallized on the (001) plane of CAAC-IGZO. This indicates that when In2O3 is crystallized using CAAC-IGZO as a seed, the crystal orientation of In2O3 can be controlled.

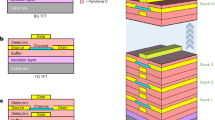

Vertical-channel FET with single-crystalline In2O3 channel

To estimate the electrical characteristics of an FET with a single-crystalline In2O3 channel, a prototype vertical-channel FET (VFET) with an In2O3 channel having no grain boundaries in a channel region was fabricated (Fig. 4a)60,61,62,63,64,65,66. The FET is circular when seen from the above, and the diameter of a cylindrical portion and the interlayer insulator thickness are 60 nmɸ and 95 nm, respectively. In the vertical-channel FET, In2O3 between the upper source and drain (S/D) electrodes and the lower S/D electrodes in the vertical direction serves as a channel region. The vertical-channel FET was fabricated through the following process (Fig. 4b). Lower S/D electrodes, an interlayer insulator film, and upper S/D electrodes were successively formed, and then a channel hole was formed. Next, a 2-nm-thick CAAC-IGZO film serving as a seed layer was formed over the upper S/D electrodes by physical vapor deposition (PVD). A stack of tungsten and silicon-doped indium tin oxide thereover was used for each of the upper and lower S/D electrodes. Then, a 10-nm-thick In2O3 film was formed by ALD over and in the cylindrical portion. The In2O3 film was formed at 200 °C using an In(C2H5)3 precursor and an O3 oxidizer. Different conditions of the oxidation time were set in advance, and the In2O3 film was formed with an oxidation time of 9 s, which is a condition under which In2O3 with a large grain size was obtained. Next, a gate insulator and gate electrodes were formed.

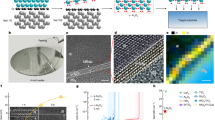

Figure 5 is a cross-sectional TEM image of the prototype VFET using single-crystalline In2O3 in its channel portion. According to the STEM-EDX line analysis, Ga and Zn derived from the IGZO were detected over the upper S/D electrodes, whereas they were hardly detected over the lower S/D electrodes (Figs. 6a to 6d). This is probably because the CAAC-IGZO seed layer, which was formed by PVD, was not formed in the deep and fine channel hole37. This indicates that IGZO might be slightly formed over the lower S/D electrodes but is too thin to be recognized as a film and thus does not function as the CAAC-IGZO seed layer. Figure 6e–g shows the results of Fast Fourier transform (FFT) analysis on the channel region between the upper S/D electrodes and the lower S/D electrodes. As shown in Fig. 5, the crystal orientation of the In2O3 on the top surface of the (001) plane of the IGZO was [111] in an almost perpendicular direction with respect to the substrate. In addition, in the channel region, the uniform FFT pattern was obtained continuously, and the crystal orientation of In2O3 was [111] in the almost perpendicular direction, and was \([\bar{11}2]\) in the almost horizontal direction with respect to the substrate. Furthermore, on the side surface of the upper S/D electrode, the crystal orientation of the crystalline In2O3 was [111] in the perpendicular direction and was \([\bar{11}2]\) toward the electrode. In other words, the In2O3 crystal has a uniform orientation along the side surface of the insulating film and is smoothly curved, even in the edge region. This demonstrates that as long as the (001) plane of the CAAC-IGZO seed is flat and smooth, the In2O3 is single-crystallized in a direction under the influence of the seed without generating grain boundaries even at positions far from the seed or on curved or vertical surfaces with planes that are not necessarily parallel to that of the seed. This single crystallization has reproducibility, and was also observed in a device of another lot.

a Image of the VFET and its surrounding area. b Image of the entire VFET in a green square region denoted by 1 in (a). c, d Enlarged views of a red square region denoted by 2 and a blue squre region denoted by 3 in (b). The channel-hole diameter is 60 nmɸ. The VFETs are arranged at a density of 4.8 μm−2 with an x pitch of 380 nm and a y pitch of 540 nm, which is the density applicable to LSI devices. The seed is a 2-nm-thick CAAC-IGZO film, and a 10-nm-thick In2O3 film formed under the condition where the oxidation time during which O3 flows was 9 s is used for a channel region. The yellow dashed line in (c) indicates a grain boundary, which was not observed in the channel region between the upper S/D electrodes and the lower S/D electrodes. In the channel region, the semiconductor layer that has a crystal orientation in one direction and does not have grain boundaries is a single crystalline layer.

a HAADF-STEM image and (b) STEM-EDX profiles around the upper S/D electrodes. c HAADF-STEM image and (d) STEM-EDX profiles around the lower S/D electrode. e TEM image and (f) Fast Fourier transform (FFT) analysis results of a red square region denoted by 1 in (e). g Enlarged view of a blue square region denoted by 2 in (f). Regarding the STEM-EDX profiles, adequate quantities of Ga and Zn are detected between Upper S/D electrode 2 and ALD-In2O3, whereas only small quantities of Ga and Zn are detected between Lower S/D electrode 2 and ALD-In2O3. The fact that IGZO having crystallinity cannot be formed in a channel hole is consistent with the previously reported formation model of CAAC-IGZO39. Regarding FFT analysis results in the channel region, uniform FFT patterns were obtained continuously. The crystal orientations are aligned throughout the channel region.

To confirm the effect of the seed, Fig. 7 shows a cross-sectional TEM image of the VFET in the case where the 2-nm-thick CAAC-IGZO film is not formed before In2O3 film formation. Unlike in Fig. 5, some grain boundaries are observed in In2O3 in the channel region in Fig. 7.

a, b Images of the entire VFET. c, d Enlarged views of a red square region denoted by 1 and a blue square region denoted by 2 in (a, b). The channel-hole diameter is similar to that of Fig. 5. In the VFET formed without the seed, several crystalline particles with random orientation can be seen. The yellow dashed lines in (c, d) indicate the grain boundaries.

Figure 8a–c show the comparison results of drain current (Id) versus gate–source voltage (Vgs) characteristics of FETs with/without the seed CAAC-IGZO film. The upper S/D electrodes were set to be “Drain”, and threshold voltage (Vth) was defined as Vgs at Id = 1 pA. With the seed, Ion at Vgs = 3 V was 28.8 μA, the standard deviation of Vth was 0.05 V (low), and the subthreshold slope (SS) was 86.7 mV dec.−1 (low). Without the seed, Ion was 22.5 μA, the standard deviation of Vth was 0.11 V, and SS was 95.7 mV dec.−1, which were inferior to those in the case with the seed.

Id–Vgs characteristics of VFETs with the In2O3 channels formed (a) with and (b) without a seed layer, c electrical characteristics list, and (d) measurement results of off-state leakage currents. For each channel region, a 10-nm-thick In2O3 film (Tsub = 200 °C) was formed via ALD under the condition where the oxidation time during which O3 flows was 9 s. The channel length (L) is defined as the interlayer insulator thickness.

Next, we confirmed the off-state current. In the measurement of Id–Vgs characteristics of a single FET, the measurement limit of an off-state current is approximately 1 pA, and thus an off-state current below this value cannot be measured. Thus, we evaluated the off-state current using an evaluation circuit comprising the Device Under Test (DUT), a read circuit, and a write transistor40. For the DUT, 20000 VFETs with W/L = 60 nmɸ/95 nm were connected in parallel. The channel length (L) is defined as the interlayer insulator thickness. Lower S/D electrodes of each of the VFETs were connected to a storage node (SN). The evaluation results revealed that the off-state current of a VFET using single-crystalline In2O3 in its channel portion was 68.4 zA µm−1 at 85 °C, which was lower than that in the case without CAAC-IGZO (Fig. 8d). Evaluation by extrapolation revealed that the off-state current was 2.0 zA µm−1 at 27 °C, which was lower than that of a bulk Si FET67 by approximately 10 digits. That is, the In2O3 VFET also has a favorable off-state current. Figure 8a and d show that Vth showing normally-off characteristics (0.10 V) is obtained, and the on/off ratio with approximately 17 digits can be obtained at 27 °C.

Discussion

In this study, the formation of a single-crystalline In2O3 film was confirmed over an insulating film on an inner wall of a channel hole, which serves as a channel portion of a VFET, by utilizing CAAC-IGZO as a seed layer. We consider the principle of single crystallization of an In2O3 film on the insulating film as follows.

The In arrangement in the (001) plane of the CAAC-IGZO is similar to that in the (111) plane of the bixbyite crystal structure of In2O3. Thus, the lattice mismatch degree when the (111) plane of In2O3 is placed on the (001) plane of IGZO is low (0.55%) (Fig. 2a). Furthermore, the interface energy between the amorphous In2O3 and the (111) plane of the crystalline In2O3 is 1.92 eV nm−2, which is lower than that between the amorphous In2O3 and a plane with another orientation of the crystalline In2O3 (Fig. 2b). Accordingly, single crystallization of the In2O3 film in the channel region occurs in the following process:

(a) An In2O3 film is formed over and in a cylindrical portion of a VFET by ALD.

(b) Single crystallization of the In2O3 film over a CAAC-IGZO film serving as a seed layer occurs owing to solid phase epitaxy ((1) in Fig. 9)68,69,70.

(c) Single crystallization of the In2O3 film progresses in the horizontal direction toward a region away from the CAAC-IGZO film owing to solid phase epitaxy, using the In2O3 film that has been single-crystallized in (b) as a seed layer ((2) in Fig. 9).

(d) After the solid phase epitaxy in the horizontal direction reaches an end portion of the In2O3 film, single crystallization of the In2O3 film progresses in the vertical direction with respect to the substrate plane owing to solid phase epitaxy, using the In2O3 film that has been single-crystallized in (c) as a seed layer ((3) in Fig. 9).

We infer that by single crystallization in such a manner, an In2O3 film having no grain boundaries in a direction where current flows was formed on the insulating film on the inner wall of the channel hole, which serves as a channel portion of the VFET.

In a VFET with an In2O3 channel formed using a CAAC-IGZO film as a seed layer, a current path in a channel portion has a single grain, and thus the same effect as that of an FET formed using a single-crystalline In2O3 can be obtained. TEM analysis confirmed that grain boundaries were not generated in the carrier path of the In2O3-based VFET formed using a CAAC-IGZO film as a seed layer (Fig. 5 and Fig. 6), and we also confirmed that Ion increase, Vth variation reduction, and SS improvement occurred in the VFET, compared to a VFET with an In2O3 channel formed without a seed layer (Figs. 8a and 8c). Accordingly, phenomena such as low Ion, Vth variation, and inferior SS are caused by grain boundaries across the carrier paths, and thus the elimination of grain boundaries in the channel region owing to solid phase epitaxy caused by the seed layer probably induces Ion increase, Vth variation reduction, and SS improvement.

A study of application of crystalline In2O3 to transistors was reported in 200745. In order to realize the application to LSI10, we formed a prototype of a high-integration vertical transistor suitable for 3D VLSI using single-crystalline In2O3 in its channel region. If the on-state characteristics of the single-crystalline In2O3 FETs are improved by, for example, reducing external resistance and on-state characteristics equivalent to those of n-channel Si FETs are obtained in the future, single-crystalline In2O3 FETs can be used in a manner similar to those of n-channel Si FETs used in VLSIs. This advancement can lead to further development in the field of VLSI via 3D integration. A CMOS circuit in which only a PMOS is formed over a Si substrate and an NMOS using single-crystalline In2O3 is stacked over the PMOS is expected to simplify a complicated process such as well separation (Fig. 10).

We believe that a CMOS circuit using single-crystalline In2O3 FETs can achieve considerable power reduction owing to the implementation of 3D integration and their extremely low off-state current. If a CMOS circuit using single-crystalline In2O3 FETs is applied to supercomputers or servers, global power consumption is expected to shrink drastically. This advancement would therefore be a fundamental technique for combating global warming.

Methods

Sample fabrication process

We prepared a single-crystalline YSZ substrate containing Y2O3 at 10 mol% (Shinkosha Co., Ltd). Deposition of In2O3 was performed using a Picosun thermal ALD system (Model: R200). In the ALD process, the substrate was heated in a deposition chamber for 7 min, and the substrate temperature was kept at 200°C. One ALD deposition cycle was a sequence of In precursor (In(C2H5)3) for 0.1 s, a purge for 3 s, O3 + O2 for 9 s, and a purge for 3 s. The O3 concentration was 19 wt%.

Cross-sectional observation

The cross-sectional TEM images were captured with a JEOL JEM-ARM 200 F under conditions of an acceleration voltage of 200 kV, Cs-TEM, and magnification accuracy of ± 3%. HAADF-STEM and STEM-EDX analyses were performed with a JEOL JEM-ARM200F NEOARM. JED-2300T was used as a detector of STEM-EDX.

Simulation

Calculation of lattice mismatch of single-crystalline YSZ or InGaZnO4 (Fig. 2a) was performed in the following manner. We used Ogre 2.058, an open source code capable of generating an interface model between a bulk molecular crystal structure and a surface slab, and input data of a crystallographic information file (CIF), a bonding face, and structure characteristics of each crystal structure to calculate the lattice mismatch and the bonding cross-sectional area of each super-cell having two structures. Calculation of amorphous/crystal planes (Fig. 2b) was performed in the following manner: an interface structure of the amorphous/crystal planes was formed by molecular dynamics (MD) using LAMMPS software. M3Gnet was used in potential setting. A lower half of a cell was fixed, the temperature was raised to 5000 K, and an upper half of the cell was melted. After that, the structure was optimized (minimized). The whole cell was rapidly cooled down to 200 K and the interface energy was calculated from the equilibration energy by NVT ensemble. The interface energy was calculated by the following formula (2) where Eamorphous/crystal is the energy of the interface structure, Ecrystal is the energy of crystal, Eamorphous is the energy of amorphous, and S is the cross-sectional area of the interface.

Evaluation of electric characteristics

The Id–Vgs measurement was performed under atmospheric pressure at room temperature with a semi-automated prober (HiSOL, Inc.). A 4156 C parameter analyzer (Keysight Technologies) was used as a measurement instrument. The Id–Vgs measurement was performed under conditions of Vgs = −4 V to 4 V and drain voltage (Vds) = 0.8 V.

We evaluated the off-state current using an evaluation circuit comprising DUT, a read circuit, and a write transistor38. For the DUT, 20000 VFETs with W/L = 60 nmɸ/95 nm were connected in parallel. The lower S/D electrodes of each of the VFETs were connected to the SN. The evaluation was performed in the following manner: first, the write transistor was turned on, and a potential of 0.8 V was written to the SN; then, a potential of −1.5 V was continuously applied to gates of the DUT and the write transistor to maintain an off state; a change in SN potential (VSN) over time was measured through the read circuit, and the off-state current of the DUT was estimated.

Data availability

The data that support the findings of this study are available from the corresponding authors upon reasonable request.

References

Electricity 2024: analysis and forecast to 2026 (IEA, 2024).

Dayarathna, M. K. et al. Data center energy consumption modeling: a survey. IEEE Commun. Surv. Tutor. 18, 732–794 (2015).

Wu, S. H. et al., Performance boost of crystalline In-Ga-Zn-O material and transistor with extremely low leakage for IoT normally-off CPU application. in Proc. IEEE Symp. on VLSI Tech., 166-167 (2017).

Kimizuka N. and Yamazaki S. Physics and technology of crystalline oxide semiconductor CAAC-IGZO: Fundamentals. (John Wiley & Sons, Ltd, 2017).

Yamazaki, S. et al. C-axis aligned crystalline indium–gallium–zinc oxide ceramics and oxide semiconductor LSI as countermeasures against global warming. Ceram. Int. 49, 24123–24141 (2023).

Suzuki, M. Systematic Survey of Innovation in Transparent Oxide Semiconductor “IGZO” for Next-Generation Thin-Film Transistors. National Museum of Nature and Science, Survey Report on the Systematization of Technology (National Museum of Nature and Science, 2023).

Hosono, H. How we made the IGZO transistor. Nat. Electron 1, 428 (2018).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Kamiya, T. et al. Electron-beam-induced crystallization of amorphous In-Ga-Zn-O thin films fabricated by UHV sputtering. The Int. Display Workshops 478–481 (2013).

Yamazaki S. and Godo H. (2011). US patent 9,209,092.

Kozuma, M. et al. OLED microdisplay with monolithically integrated CAAC-OS FET and Si CMOS achieved by two-dimensionally arranged silicon display drivers. IEEE J. Electron Devices Soc. 12, 187–194 (2024).

Nagatsuka, S. et al. A 3bit/cell nonvolatile memory with crystalline In-Ga-Zn-O TFT. 2013 5th IEEE Int. Memory Workshop 1–4 (2013).

Yamazaki, S. and Tsutsui, T. Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to Displays. (John Wiley & Sons, Ltd, 2017).

Yamazaki, S. and Fujita, M. Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSI. (John Wiley & Sons, Ltd, 2017).

Onuki, T. et al. Embedded memory and ARM cortex-M0 core using 60-nm C-axis aligned crystalline indium–gallium–zinc oxide FET integrated With 65-nm Si CMOS. IEEE J. Solid-State Circuits 52, 925–932 (2017).

Maeda, S. et al. A 20ns-write 45ns-read and 1014-cycle endurance memory module composed of 60nm crystalline oxide semiconductor transistors. 2018 IEEE Int. Solid-State Circuits Conf. 484-485 (2018).

Saito, N. et al. Origin of high mobility in InSnZnO MOSFETs. IEEE J. Electron Devices Soc. 6, 1253–1257 (2018).

Oota, M. et al. 3D-Stacked CAAC-In-Ga-Zn Oxide FETs with Gate Length of 72nm. 2019 IEEE Int. Electron Devices Meeting 50-53 (2019).

Ishizu, T. et al. An energy-efficient normally off microcontroller with 880-nW standby power, 1 clock system backup, and 4.69- μs wakeup featuring 60-nm CAAC-IGZO FETs. IEEE Solid-State Circuits Let. 2, 293–296 (2019).

Saito, D. et al. IGZO-based compute cell for analog in-memory computing—DTCO analysis to enable ultralow-power AI at edge. IEEE Trans. Electron Devices 67, 4616–4620 (2020).

Zou, T. et al. Pixellated perovskite photodiode on IGZO thin film transistor backplane for low dose indirect x-ray detection. IEEE J. Electron Devices Soc. 9, 96–101 (2021).

Chen, M.-C. et al. A > 64 Multiple States and > 210 TOPS/W high efficient computing by monolithic Si/CAAC-IGZO + Super-Lattice ZrO2/Al2 O3/ZrO2 for ultra-low power edge AI Application. 2022 Int. Electron Devices Meeting 423-426 (2022).

Takahashi H. et al. Soft- and Hard-error radiation reliability of 228 KB 3 T + 1 C oxide semiconductor memory. 2023 IEEE International Reliability Physics Symposium 7 C.1-1-7 C.1-6 (2023).

Yakubo Y. et al. Crystalline Oxide Semiconductor-based 3D bank memory system for endpoint artificial intelligence with multiple neural networks facilitating context switching and power gating. 2023 IEEE Int. Solid-State Circuits Conf. 212-213 (2023).

Hao J. et al. 3D NAND Memory Operation of Oxide-Semiconductor Channel FeFETs and the Potential Impact of In-Plane Polarization. 2023 7th IEEE Electron Devices Technology & Manufacturing Conf. (2023).

Huang, W.-C. et al. X-ray detectors based on amorphous InGaZnO thin films. IEEE Trans. Electron Devices 70, 3690–3694 (2023).

Yazaki, N. et al. Effectiveness of c-Axis Aligned Crystalline IGZO FET as selector element and ferroelectric capacitor scaling of 1T1C FeRAM. IEEE J. Electron Devices Soc. 11, 467–472 (2023).

Çeliker, H. et al. Multi-project wafers for flexible thin-film electronics by independent foundries. Nature 629, 335–340 (2024).

Hikake, K. et al. A nanosheet oxide semiconductor FET Using ALD InGaOx channel for 3-D integrated devices. IEEE Trans. Electron Devices 71, 2373–2379 (2024).

Zhuang M. et al. A Full-Oxide CMOS Operational Amplifier Based on n-Type IGZO and p-Type SnO Thin-Film Transistors. IEEE Tran. on Electron Devices Early Access, 1-6 (2024).

Zhang, S. et al. Aging-Aware LTPO DTCO for large-scale integrated circuit-driven flexible intelligent sensing system. IEEE Trans. Electron Devices 71, 3322–3328 (2024).

Chiu, J.-C. et al. Performance Improvement by Double-Layer a-IGZO TFTs With a Top Barrier. IEEE J. Electron Devices Soc. 10, 45–50 (2021).

Watanabe M. et al. Physics-Based Compact Model for CAAC In-Ga-Zn Oxide Multi-Gate FETs with Free Shape of Fin. 2022 6th IEEE Electron Devices Technology & Manufacturing Conf. 357-359 (2022).

Pi, T. et al. High-Performance a-IGZO TFT fabricated with ultralow thermal budget via microwave annealing. IEEE Trans. Electron Devices 69, 156–159 (2022).

Park, J. et al. Floating body effect in indium–gallium–zinc–oxide (IGZO) thin-film transistor (TFT). Sci. Rep. 14, 10067 (2024).

Yamazaki S. et al. (2009) US patent 9,935,202.

Yamazaki, S. et al. Properties of crystalline In–Ga–Zn-oxide semiconductor and its transistor characteristics. J. Appl. Phys. 53, 04ED18 (2014).

Kato, K. et al. Evaluation of off-state current characteristics of transistor using oxide semiconductor material, indium–gallium–zinc oxide. Jpn. J. Appl. Phys. 51, 021201-1-021201–7 (2012).

Belmonte A. et al. Lowest IOFF < 3×10 − 21 A/μm in capacitorless DRAM achieved by Reactive Ion Etch of IGZO-TFT. 2023 IEEE Symp. on VLSI Technology and Circuits 1-2 (2023).

Limpijumnong, S. et al. Hydrogen doping in indium oxide: An ab initio study. Phys. Rev. B 80, 193202 (2009).

Im, Y. et al. Buffer layer engineering of indium oxide based trench TFT for ultra high current driving. IEEE Electron Device Let. 44, 1849–1852 (2023).

Lee, J.-Y. et al. Engineering a solution-processed In2O3 TFT with improved ambient stability via MoO3 doping. IEEE Trans. Electron Devices 71, 1946–1950 (2024).

Choi, S.-H. et al. c Axis Aligned 3 nm Thick In2O3 Crystal Using New Liquid DBADMIn Precursor for Highly Scaled FET Beyond the Mobility−Stability Trade-off. NanoLett 24, 1324–1331 (2024).

Magari, Y. et al. High-mobility hydrogenated polycrystalline In2O3 (In2O3:H) thin-film transistors. Nat. Commun. 13, 1–8 (2022).

Dhananjay & Chu, C.-W. Realization of In2O3 thin film transistors through reactive evaporation process. APPLIED PHYSICS LETTERS 91, 132111 (2007).

Wang X., Furuta M. Rapid thermal crystallization of H-doped InO x for thin film transistors. International Conference on Solid State Devices and Materials, E-5-03, 2023.

Zheng D. et al. Ultrathin atomic-layer-deposited in2o3 radio-frequency transistors with record high fT of 36 GHz and BEOL Compatibility. VLSI, T11-1, 2023.

Lin Z. et al. Enhancement of In2O3 field-effect mobility Up To 152 cm2·V-1·s-1 using HZO-based higher-k linear dielectric. VLSI, T4.3, 2024.

Macco, B. et al. On the solid phase crystallization of In2O3:H transparent conductive oxide films prepared by atomic layer deposition. J. Appl. Phys. 120, 85314 (2016).

Charnas, A., Lin, Z., Zhang, Z. & Ye, P. D. Atomically thin In2O3 field-effect transistors with 1017 current on/off ratio. Appl. Phys. Lett. 119, 263503 (2021).

Hsu, C.-H. et al. Single-crystalline-like indium tin oxide thin films prepared by plasma enhanced atomic layer deposition. J. Mater. Chem. C. 10, 12350 (2022).

Park, J.-H. et al. Atomically thin amorphous indium–oxide semiconductor film developed using a solution process for high-performance oxide transistors. nanomaterials 13, 2568 (2023).

Chen, Z. et al. High-performance fully thermal ALD-processed IGZO thin film transistors. IEEE Trans. Electron Devices 71, 1963–1968 (2024).

Honda, T., Tsubuku, M., Nonaka, Y., Shimazu, T. and Yamazaki, S. (2011) US patent 9, 860.

Koida, T. & Kondo, M. High electron mobility of indium oxide grown on yttria-stabilized zirconia. J. Appl. Phys. 99, 123703 (2006).

Taga, N. et al. Deposition of heteroepitaxial In2O3 thin films by molecular beam epitaxy. Jpn. J. Appl. Phys. 37, 6524 (1998).

Kalaivani, S. et al. Probing the combined additions of Ca2+ and PO43− in the stabilized ZrO2 polymorph: structural, morphological and mechanical analysis. CrystEngComm 20, 6752–6761 (2018).

Saeed, M. et al. Structure prediction of epitaxial inorganic interfaces by lattice and surface matching with Ogre. J. Chem. Phys. 155, 034111 (2021).

Yang, S. et al. Electronic structure of InAs and InSb surfaces: density functional theory and angle-resolved photoemission spectroscopy. Adv. Quantum Technol. 5, 2100033 (2022).

Yamazaki S. and Yoshizumi K.(2012). US patent US10,038,011.

Fujiwara, H. et al. Surrounding gate vertical-channel FET with gate length of 40 nm using BEOL compatible high-thermal-tolerance In-Al-Zn oxide channel. IEEE Trans. Electron Devices 67, 5329–5335 (2020).

Jagannathan H. et al. Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices. 2021 IEEE Int. Electron Devices Meeting 557–560 (2021).

Li, Z. et al. A 3D vertical-channel ferroelectric/anti-ferroelectric FET with indium oxide. IEEE Electron Device Let. 43, 1227–1230 (2022).

Chen, Q. et al. Investigation of asymmetric characteristics of novel vertical channel-all-around (CAA) In-Ga-Zn-O field effect transistors. IEEE Electron Device Let. 43, 894–897 (2022).

Tang, W. et al. 30 Mb/mm2/layer 3D eDRAM Computing-in-Memory with Embedded BEOL Peripherals and Local Layer-wise Calibration based on First-Demonstrated Vertically-stacked CAA-IGZO 4F2 2T0C Cell. 2023 Int. Electron Devices Meeting 1–4 (2023).

Hirose, T. et al. 1-Mbit 3-D DRAM using a monolithically stacked structure of a Si CMOS and heterogeneous IGZO FETs. IEEE J. Electron Devices Soc. 12, 236–242 (2024).

Kunitake H. et al. High-temperature Electrical Characteristics of 60nm CAAC-IGZO FET:Comparison with Si FET. 2018 Int. Conf. on Solid State Devices and Materials 787-788 (2018).

Narayan, J. Interface structures during solid-phase-epitaxial growth in ion-implanted semiconductors and a crystallization model. J. Appl. Phys. 53, 8607–8614 (1982).

Strane, J. W. et al. Metastable SiGeC formation by solid phase epitaxy. Appl. Phys. Lett. 63, 2786–2788 (1993).

Williams, J. S. et al. Dominant influence of beam-induced interface rearrangement on solid-phase epitaxial crystallization of amorphous silicon. Phys. Rev. Lett. 55, 1482–1485 (1985).

Author information

Authors and Affiliations

Contributions

S.Y. developed the theory. F.I., T.Ohno and Y.E. evaluated the basic physical properties of In2O3. S.T., M.K. and H.S. fabricated FETs. R.M., E.A and T.M. conducted the measurement of electrical characteristics. S.S. prepared figures and refined drafts. T.Onuki refined drafts. M.T. contributed to interpreting results and refining drafts.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

: Communications Materials thanks Xiaotian Zhang and the other anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yamazaki, S., Isaka, F., Ohno, T. et al. High-performance single-crystalline In2O3 field effect transistor toward three-dimensional large-scale integration circuits. Commun Mater 5, 184 (2024). https://doi.org/10.1038/s43246-024-00625-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s43246-024-00625-x

- Springer Nature Limited