Abstract

Flexible direct current (DC) grids face a serious challenge in terms of rapidly isolating DC faults. A DC circuit breaker is an effective solution for DC fault isolation. To improve the fault-isolation and reclosing capability of flexible DC systems, a new high voltage direct current (HVDC) circuit breaker topology with adaptive reclosing capability is proposed in this paper. The topology of the circuit breaker is a T-shaped structure, which has the ability to break the current in both directions and effectively reduce the cost of components. Meanwhile, after the fault is cleared, the circuit breaker is controlled to inject a voltage signal into the line. Based on this, to prevent the circuit breaker reclosing in the event of a permanent fault from having an impact on the system, a method for fault identification based on Euclidean distance that uses the voltage signal to identify the fault properties is proposed. Finally, the performance of the circuit breaker is simulated and verified by PSCAD/EMTDC simulation software, and compared with the typical existing circuit breakers to verify the effectiveness of the circuit breaker and reclosing scheme.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

A flexible DC grid has the superior qualities of high reliability and independent control of the active and reactive powers [1], which is of great significance to the development of renewable energy grid-connected technologies. However, its low damping and quick fault development make rapid fault isolation one of the main technical bottlenecks restricting its development [2, 3]. Modular multilevel converters (MMCs) based on full-bridge units can block fault currents, and DC/DC power converters [4] with fault self-clearing capability can clear faults for multi-voltage level systems. However, both methods result in short-term outages of entire multi-terminal direct current (MTDC) grids, which is unacceptable for large-scale power grids. Clearing line faults with a DC circuit breaker (DCCB) is the most promising type of method for fault clearing in DC systems because it isolates the fault while guaranteeing the normal power transmission of the non-faulty lines of the system [5].

Capacitor-commutated DCCBs are based on traditional DC circuit breakers [6], where the insulated gate bipolar transistors (IGBTs) of the transfer branch are replaced by series capacitors and diodes [7, 8]. A novel hybrid circuit breaker was proposed in [8] that isolates line faults by generating reverse current through capacitive and inductive oscillations. However, the control of the circuit breaker is complicated. In [9], a capacitor-commutated DCCB with limited current functionality was proposed, which adopted a bridge-type capacitor-commutation unit to buffer the voltage of the device. However, this method requires a large number of IGBTs in series and parallel, which greatly increased the cost of the DCCB. In [10], a solid-state DC circuit breaker was proposed, which uses a high-temperature superconducting current limiter to limit the current to reduce the cost of the circuit breaker.

In addition, flexible DC transmission lines are mostly overhead lines, and the probability of instantaneous faults is high on overhead lines. Using a DC circuit breaker to identify the fault nature is an economic and promising solution [11,12,13,14,15]. A pre-charged capacitor circuit breaker was proposed in [11]. However, a reclosing strategy is not mentioned. A circuit breaker adaptive reclosing sequence strategy was proposed in [12]. However, it is still a non-selective reclosing method. A DC solid-state circuit breaker with soft reclosing capability was proposed in [13]. However, the scheme does not consider the influence of discharge current amplitude on the system when identifying the fault nature. A soft reclosing scheme for circuit breakers, based on adding mechanical switches and resistors, was proposed in [14]. However, this method makes the IGBTs in the main circuit breaker act frequently, which is not conducive to the service life of the circuit breaker. A method for identifying fault nature through the partial sub-modules (SMs) of the DCCB was proposed in [15]. However, this scheme is susceptible to noise interference. A method for judging fault properties by injecting the characteristic signals of the half-bridge MMC and the circuit breaker was proposed in [16]. However, this method requires a high sampling frequency and is easily affected by fault impedance.

In summary, a capacitor-commutated DC circuit breaker with fault character discrimination capability (FDC-CCCB) is presented in this paper. The circuit breaker structure has bidirectional conduction and current-limiting functionality, which can greatly reduce the cost of the device. The characteristic where the capacitor voltage in the capacitor circuit breaker needs to be released through the energy release branch is used in this paper. The capacitor in the circuit breaker is controlled to discharge to the fault line. Then the nature of the fault is judged to prevent the permanent fault from having a secondary effect on the system.

2 FDA-CCCB principal and analysis

2.1 FDA-CCCB configuration

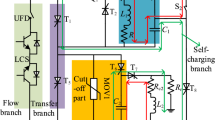

The structure of the FDA-CCCB is shown in Fig. 1. It is mainly composed of four parts: the main branch, the transfer branch, the breaking branch, and the reclosing branch.

-

1)

When the system is under the normal operation condition, current flows through the main branch, which consists of mechanical switches K1,2 and a diode bridge module. T1 is a transfer switch, which is composed of a small number of IGBTs in series, and D1 – D4 form a diode bridge.

-

2)

The transfer branch is composed of diversion diodes (D5,6) and current-limiting inductors (L1,2). L1,2 are used to limit the increase rate of the fault current. After T1 is disconnected, the current is transferred to the breaking branch.

-

3)

The breaking branch is composed of a mechanical switch K and breaking sub-modules (BSMs). When the system is under normal operation, K is in the disconnected state to prevent the open branch of the circuit breaker from being affected by the high voltage. Each BSM consists of three branches: the IGBT branch B1, the capacitor branch B2, and the arrester branch B3. The specific structure is shown in RSMN: T2 ~ Tn (n = 2,3…) are IGBTs, TCN (where N is the number of BSMs, and N = 1,2…) are thyristors, CN is a capacitor, R3N is a bleeder resistor, and a metal-oxide varistor (MOV) is an arrester. The breaking branch is modularized to avoid a large number of IGBTs in B2 to withstand the capacitor charging voltage in series, and to reduce the equipment withstand voltage capability requirements. TCN has the functions of blocking the normal load current and preventing the capacitor from charging when the system is running stably. CN is configured with an energy release branch, where K3N is a mechanical switch and R3N is an energy bleeder resistor. The energy release branch is utilized to release the voltage in the capacitor after the fault is cleared to prevent TCN from being continuously subjected to the reverse voltage of the capacitor, which is not conducive to the restarting of the circuit breaker.

-

4)

The reclosing branch is composed of a thyristor Tre. After the circuit breaker is opened, CN is controlled to inject a voltage signal into the line through the reclosing branch. Then the nature of the fault is judged according to what is between the line voltage signal under the instantaneous fault and the permanent fault.

2.2 Working principle and theoretical analysis

Taking one breaking sub-module as an example, the current conduction paths at each stage based on Fig. 1 are shown in Fig. 2. Assuming that a short-circuit fault occurs at the right end of the circuit breaker at t0, current waveforms of the circuit breaker in each stage are shown in Fig. 3.

Stage a (t0 ~ t1). The fault current rises at t0. However, the circuit breaker does not receive the action signal, and the current flows through K1 and the main branch.

Stage b (t1 ~ t3). The circuit breaker receives the action signal, T2 ~ Tn are turned on, and T1 is turned off. The current is transferred to the B1 branch through D5,6 and L1,2.

The expression for stage b is as follows:

where Udc represents the DC voltage source voltage, Rt represents the equivalent resistance of the B1 branch IGBTs, L' represents the equivalent inductance in the fault circuit at stage b, and Ldc represents the line smoothing reactor.

After T1 is disconnected, idc(0) = idc(t1). Thus,

The time constant is calculated by the following formula:

During stage b, the fault current increasing rate is mainly determined by the value of the current-limiting inductance.

Stage c (t3 ~ t5). TCN is turned on. Then T2 ~ Tn are turned off. The fault current is transferred from B1 to B2, and the capacitor CN is rapidly charged. When the voltage of the breaking branch increases to the rated voltage of the system, the fault current begins to decrease.

The expression for the stage c is as follows:

where C represents the capacitance in the capacitor branch, and RC represents the resistance in the capacitor branch. At this time, the initial current of the line and the initial voltage of the capacitor are as follows:

This yields uc(t) and idc(t) as follows:

where

It can be known from (8)–(10) that the larger the value of C, the longer the capacitor charging time, and the longer the time for the current to transfer from the capacitor branch to the arrester branch. Although RC increases the charging time of the capacitor, it also increases the voltage of the capacitor branch, which is conducive to the rapid operation of the arrester to absorb energy, shortens the fault clearing time, and reduces the energy absorption of the arrester and prolongs its service life.

Stage d (t5~t7). TCN is turned off after being subjected to reverse voltage, the fault current is transferred to the arrester branch, the arrester absorbs the remaining energy in the circuit, and the fault current drops rapidly.

Stage e: After the circuit breaker is opened, the circuit experiences a deionization time of 200 ~300 ms, and then enters the stage of fault identification. Tre is turned on to discharge the bottom CN of the sub-module capacitor to the line, while all K3Ns are turned off to release the energy in the capacitor.

When a permanent fault occurs on the line, the expression of this stage is as follows:

where:

where Rg represents the fault impedance, x represents the distance from the measurement point to the fault point, and r0 represents the line resistance per unit length. The capacitor discharge time is related to the values of CN, RC, R3N, and Rg.

Taking the moment when the injected voltage signal is first detected as t0', and Δts represents the sampling time, the voltage signal detected during (t0', t0' + Δts) is the electrical quantity required to identify the nature of the fault. The fault is judged by comparing the difference between the line voltage signal under the instantaneous fault and the permanent fault in the (t0’, t0’ + Δts). When it is determined that the line has an instantaneous fault, the circuit breaker receives the reclosing command, and K2, K1, and T1 of the circuit breaker are closed at both ends of the line in turn, and the system gradually returns to normal operation.

3 Parameters design

Circuit breakers in a two-terminal flexible DC system with a rated voltage of 320 kV and a rated current of 2 kA are discussed and analyzed in this section. The circuit breaker parameters proposed in this paper are designed as follows: the fault current amplitude is limited to within 8kA, the fault detection is 2 ms, and the fault clearing time is less than 6 ms.

3.1 Parameter design of the current-limiting inductor

It can be seen from (3) that the increase rate of the fault current is mainly related to the value of L1、L2. In addition, when the current is transferred to the breaking branch, the voltage of T1 is the voltage across the current-limiting inductor. In this paper, four groups of different inductance values are selected, and the changes of the fault current and voltage across T1 with the value of L1 are shown in Fig. 4.

It can be seen that the larger the current-limiting inductance, the smaller the secondary increase rate of the fault current, and the lower the requirement for the breaking capacity of the circuit breaker. However, this increases the voltage of T1, which is consistent with the above analysis results. Considering the three aspects of fault current amplitude and rate of increase, and the IGBTs withstand voltage, combined with the current-limiting requirements of the current actual project, a 70 mH current-limiting inductor is used.

3.2 Parameter design of the capacitor

After the fault current is transferred to B2, the capacitor is charged and its voltage increases. In this stage, K2 and T1 share the voltage of the capacitor branch and L1. The voltage of K2 is Uk, and the maximum voltage that T1 can withstand is UT1max. To ensure the safe operation of the circuit breaker, the voltage across it should be lower than Uk + UT1max, which can be expressed as:

The range of the total breaking branch capacitance C value can be calculated by (14). Then the capacitance CN of each breaking sub-module is as follows:

where N represents the number of breaking submodules.

When CN is controlled to inject a voltage signal into the line, if a single-pole grounding fault occurs on the line, coupling occurs between the faulty line and the sound line. If the amplitude of the injected voltage is too large, the normal operation of the sound line is affected, and the power electronic device is impacted. Accordingly, the amplitude of the injected voltage signal is generally 0.1~0.2UdcN [17]. Namely, the capacitor voltage in a single breaking sub-module should be less than 0.1~0.2UdcN.

The action time of the arrester depends on the capacitor branch voltage, and the voltage of CN should meet the arrester action voltage as soon as possible. When the capacitor voltage is charged to the rated voltage of the system, the inductor voltage is zero, and the current begins to decrease. According to the time limit of the circuit breaker clearing fault, it should be less than 1 ms from the current drop to the time when arrester is put into operation. The appropriate capacitor value is selected according to the above constraints and the specific parameters of the system, and the value of CN is taken as 35 µF.

3.3 Parameter design of the bleeder resistor

When the fault impedance is 0, the resistance of the discharge circuit of CN is RC + R3N. When compared with R3N, the value of RC is exceedingly small. Thus, this study mainly designs the value of R3N. When a fault occurs in the line, the capacitor is mainly discharged through the energy release branch (K3N and R3N). According to the process analysis of the circuit breaker fault identification, the capacitor discharge time should be greater than the sampling time Δts. In addition, to limit the CN discharge current peak value, R3N should not be too small. However, if R3N is too large, it increases the discharge time of the capacitor, which is not conducive to the rapid recovery of the circuit breaker. The capacitor discharge time is usually 3~5RC. Thus,

where trmax represents the longest recovery time of the circuit breaker, which is 10 ms. When combined with the value of CN, R3N should be less than 57 Ω. Based on the above analysis, the value of R3N is 20 Ω.

4 FDA-CCCB-based fault property discrimination method

When CN is controlled to inject a voltage signal into the line, K1, K2, and K are invariably disconnected, and the converter station is isolated from the fault point. Assume the fault occurs at point F. A schematic diagram of the voltage signal injected into the fault line is shown in Fig. 5.

4.1 Fault traveling wave characteristic analysis

As shown in Fig. 5, assuming that the voltage signal VC is injected into the fault line and propagates from M to N, according to the principle of traveling wave transmission, refraction and reflection occur at the sudden change of the line wave impedance.

The refractive coefficient α and the reflection coefficient β of the impedance mutation point can be expressed as:

where Z1 represents the line wave impedance, the wave impedance of the overhead line is 300 ~ 500Ω, and Z2 represents the equivalent wave impedance of the reflection and refraction lines. In particular, when the line impedance sudden change is an open circuit, Z2 is ∞, and the corresponding α and β are 2 and 1, respectively. Therefore, the refraction coefficients αM and αN and the reflection coefficients βM and βN at both ends of M and N are 2 and 1, respectively. The impedance mutation of the line is short-circuited, namely Z2 is 0, and the corresponding α and β are 0 and -1, respectively.

A permanent fault occurs at F of the line. At t0', C is controlled to inject a voltage signal with an amplitude of VC into the line. According to the traveling wave transmission principle, it can be concluded that:

where αF and βF represent the refractive coefficient and reflection coefficient of F, respectively. When a single-pole grounding fault occurs at F of the line, Z2 = Z1||Rg; when a pole-to-pole fault occurs at F, Z2 = Z1||(Rg + Z1/2). Therefore, Z2 < Z1, that is, βF < 0.

At this time, the voltage at M can be expressed as:

where ɤ represents the attenuation coefficient of the line, and xMF represents the distance between M and F.

When the fault at F is an instantaneous fault, the voltage at M is:

where βN = 1, αM = 2.

Taking a single-pole metal ground fault at the midpoint of the line as an example, the propagation characteristics of the voltage signal in the line are shown in Fig. 6. It can be seen that when an instantaneous fault occurs in the line, the fault is cleared when the signal is injected. After the signal is injected, the first anti-travel wave measured from M is 2lmn/v, and the amplitude is larger than that of the injected voltage. When a permanent fault occurs in the line, the first voltage inverse traveling wave measured at point M is consistent with the above theoretical analysis.

The capacitors of the circuit breakers at both ends of the faulty line can be controlled to inject voltage signals. However, this scheme still has a weakness in terms of communication between the two ends. Therefore, in this paper, the capacitor of the circuit breaker on one side of the fault line is selected to inject the voltage signal, and the capacitor voltage of the circuit breaker on the other side can discharge through the energy release branch.

4.2 Euclidean distance-based fault property discrimination method

After the capacitor voltage signal is injected into the line, for an instantaneous fault, the voltage measured at M is independent of the fault impedance and fault location. Meanwhile, the voltage measured at point M is significantly different from the instantaneous fault voltage when a permanent fault occurs. In this paper, a voltage waveform at point M during an instantaneous fault is used as the reference voltage, and the Euclidean distance (ED) is used to judge whether the fault has been cleared or not. Let A = {a1,…an} and B = {a1,…an} be two finite sets, and the ED between the point ak in the set A and the point bk in the set B is as follows:

The degree of similarity between the two sets of A and B can be expressed by the ED. The smaller D(ak, bk) is, the higher the similarity between the two sets of A and B. When an instantaneous fault occurs in the line, taking the voltage waveform in Fig. 6a as the reference voltage wave, the voltage waveform measured at M is the measured voltage wave, and the difference between the measured wave and the reference wave is described by D(ak, bk) in ED. An appropriate value of D(ak, bk) is set as the threshold to distinguish the nature of the fault. According to (20) and (21), when a fault occurs at the end of the line and the fault impedance is larger, the permanent fault voltage waveform is closer to the instantaneous fault voltage waveform. Thus, to obtain the minimum value of D(ak, bk). It is necessary to set D(ak, bk)set as:

where kd represents the reliability coefficient (0 ~ 1), which is taken as 0.7. D(ak, bk)min is the minimum ED between the measured voltage waveform and the reference waveform at M under the permanent fault.

After the voltage traveling wave is injected into the line at time t0', the voltage traveling wave is induced at M. For the voltage wave at M, take t0' as the starting point and take n-1 sampling points to form a sampling window of length n. The time length of the sampling window should be greater than twice the time it takes for the voltage traveling wave to propagate throughout the entire line. Therefore, the sampling window time length Δts is:

where ks = 0.5.

To sum up, a flow chart of the fault identification scheme is shown in Fig. 7.

5 Simulation analyses

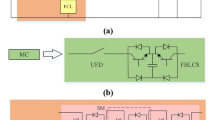

A ± 320 kV double-ended flexible DC transmission system was built in the PSCAD/EMTDC platform as shown in Fig. 8. The FDA-CCCB and system simulation parameters are shown in Table 1 [13].

5.1 Fault isolation process simulation verification

The simulated short-circuit fault occurs at 2 s and the circuit breaker receives the action command in 2.002 s.

Figure 9 shows a voltage waveform of the circuit breaker. After T1 is disconnected, the voltage at both ends of T1 is equal to the voltage at both ends of L1, which is 97.04 kV. When T2–Tn is turned off, the voltage across L1 gradually decreases. When the voltage of the breaking branch reaches the system voltage, the current begins to drop, the voltage of L1 drops to zero and increases in the opposite direction. In addition, the capacitor branch B2 and the peak voltage of a single breaking sub-module IGBT is about 60 kV. After the fault current drops to zero, K and K1 are disconnected, and the voltage of T1 and the IGBT branch B1 drops. Figure 10 shows a current waveform of the circuit breaker. At 2.002 s, K is turned on, T2 ~ Tn is turned on, T1 is turned off, and the current of the main branch is reduced to 0A. The current is transferred to B1 through the current-limiting inductor, the current of B1 increases, and the current transfer is completed after 1 ms. Then a trigger signal is given to the thyristor TCN, T2 ~ Tn is turned off, and the B1 current drops. At this time, the breaking current peak value is 7.35kA, and the peak value of the second rise rate is 1.35kA/ms. Then, the current is transferred to B2, and the capacitor is charged. When the voltage of B2 reaches the arrester operating voltage, the current begins transferring to the arrester branch B3. The arrester absorbs the remaining energy in the circuit, and the fault current is reduced to 0A. The overall fault clearing time of the circuit breaker is 5.4 ms.

Figure 11 shows the energy absorbed by the arrester. The energy absorbed by each of the sub-module arresters is 1.1 MJ. Combined with Fig. 11, the fault current drops to 0A at 2.0074 s, and the arrester maintains the breaking branch voltage within the clamping voltage range.

5.2 Fault nature discrimination simulation verification

At 2.206 s, the capacitor CN discharges to the line through the reclosing branch, and at the same time closes K3. Thus, all of the breaking sub-module capacitors discharge through the energy release branch. In this paper, D(ak,bk)min is set when the fault impedance is 500 Ω [17], D(ak,bk)set is 5.90 when a single-pole grounding fault occurs, and D(ak,bk)set is 5.26 when a pole-pole fault occurs. When an instantaneous fault occurs in the line, the voltage reverse wave amplitude measured at M is the largest. At this time, line current and voltage waveforms are shown in Fig. 12. It can be seen that when compared with the rated current of the line, the inrush current generated by CN injecting signals into the faulty line is extremely small (0.15 kA), and that the voltage amplitude of the faulty line is less than 0.2UdcN. When a single-pole grounding fault occurs in the line, the voltage waveform measured at M is the reference voltage when there is an instantaneous fault at a distance of 60 km from point M. Simulation results of D(ak,bk) under different fault properties are shown in Table 2. When a pole-pole fault occurs in the line, its fault impedance is generally smaller than that of a single-pole fault. Simulation results of D(ak,bk) under different fault properties are shown in Table 3.

The ratio of D(ak,bk) to D(ak,bk)set is used as an index to evaluate the accuracy of the fault nature discrimination method. The index can be expressed as:

In this paper, the impact of noise on the proposed method is also analyzed. The added noise is Gaussian white noise with a signal–noise ratio (SNR) of 20 dB. Tables 4 and 5 show the AC of faults with different fault locations and fault impedances at 20 dB of white noise.

It can be seen from Tables 2, 3, 4, 5 that the simulation results verify the correctness of the theoretical derivation. Using ED can effectively identify the nature of a fault, and the method is not affected by the fault impedance, fault location, or noise.

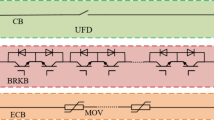

6 Circuit breaker performance comparative analysis

An FDA-CCCB is placed in a 320 kV system at the same time as a traditional circuit breaker (scheme 1) and the circuit breaker in [9] (scheme 2), and they are compared under the same operating conditions. The circuit breaker action is shown in Fig. 13. By comparison, the effectiveness of the FDA-CCCB in current-limiting and reducing the fault clearing time is verified.

Figure 14 shows a comparison of three circuit breakers. In addition, Table 6 shows the differences in the breaking currents, operating times, device withstand voltages, arrester energy absorptions, and number of components for the different circuit breaker schemes. It can be seen that the first scheme adopts a stepping input arrester, which reduces the energy absorption of a single arrester to a certain extent. In addition, the total absorbed energy is 7.5 MJ. There are two capacitor commutation units in scheme 2, where each unit is equipped with a surge arrester, the energy absorbed by the two surge arresters is the same, and the total energy consumption is 8.4 MJ. The FDA-CCCB adopts capacitor commutation, sets the RCN to limit the current flowing into the arrester, reduces the energy absorption requirements of the arrester, and the total energy consumption is 6.6 MJ. In terms of cost, the FDA-CCCB adopts a bridge structure in the main branch, the transfer branch realizes bidirectional breaking, and the current amplitude is the smallest. Thus, the number of IGBTs is greatly reduced, and only 245 IGBTs are required. In the scheme proposed in this paper, thyristors are used in the capacitor branch to prevent the capacitor charging from increasing the fault current during normal operation. In addition, thyristors are used in the closing branch to control capacitor discharge. The number of series–parallel thyristors needs to be considered, and the total number of thyristors used is 257. Although more thyristors are used, when compared with IGBTs, thyristors are cheap and widely used.

In summary, the circuit breaker scheme proposed in this paper meets the requirements of fast interruption while ensuring a low cost.

7 Conclusion

A capacitor-commutated DC circuit breaker with fault character discrimination capability was presented in this paper. Taking a 320 kV double-terminal flexible DC system as background, the circuit breaker model was built by PSCAD for simulation verification. The following conclusions can be drawn:

-

1)

The FDA-CCCB adopted a T-shaped structure, which greatly reduced the number of components and reduced the cost of circuit breakers. The breaking branch of this topology adopted a modular structure to reduce the voltage of the capacitor branch, which effectively reduced the voltage equalization problem of the IGBTs. In addition, the control of this topology is simple. Based on this topology, the parameter design principles and methods of the capacitors, the current-limiting inductors, and the other devices were analyzed. It was found that the current-limiting inductance in the circuit breaker could effectively limit the fault current amplitude to 7.35 kA, which reduced the current stress of the circuit breaker. Finally, the breaking speed of the circuit breaker is comparable to other circuit breakers that do not have current-limiting capability.

-

2)

To avoid the non-selective reclosing of the circuit breaker, this paper proposed the addition of a reclosing branch in the circuit breaker. The voltage of the capacitor was discharged to the fault line, and the injected voltage signal amplitude fluctuation range was between 0.1 and 0.2 times the rated value. Thus, it did not affect the system or health line. According to the refractive reflection characteristics of the injected voltage wave, Euclidean distance was introduced to distinguish between instantaneous and permanent faults. Through simulation verification, it was found that the method proposed in this paper has no dead space, and requires a low sampling rate, has a simple principle, is easy to implement, and possesses good capability in terms of fault impedance and noise interference.

Data availability

All data, models generated or used during the study appear in the manuscript.

References

Zhang, J., Zhang, Y., Zhou, J., Wang, J., Shi, G., Cai, X.: Control of a hybrid modular solid-state transformer for uninterrupted power supply under MVdc short-circuit fault. IEEE Trans. Ind. Electron. 70, 76–87 (2022)

Cha, J.Y., Lee, E.J., Han, B., Lee, K.B.: New thyristor-based hybrid DC circuit breaker with reverse injection of resonant current. J. Power Electron. 22, 1836–1847 (2022)

Diao, X., Liu, F., Song, Y., et al.: A novel fault ride-through topology with high efficiency and fast fault clearing capability for MVdc PV system. IEEE Trans. Ind. Electron. 70, 1404–1413 (2022)

Wu, L., Liu, J., Vazquez, S., et al.: Sliding mode control in power converters and drives: a review. IEEE JAS. 9(3), 392–406 (2019)

Mohammadi, F., Rouzbehi, K., Hajian, M., et al.: HVdc circuit breakers: a comprehensive review. IEEE Trans. Power Electron. 36(12), 13726–13739 (2021)

Derakhshanfar, T.U.J.R., Steiger, M.H.U.: Hybrid HVDC breaker-a solution for future HVDC system, pp. 1–11. Proc. CIGRE, Paris, France (2014)

Gan, W., Cui, T., Pu, X., et al.: Research on fault analysis and isolation technology of flexible DC distribution network. 2022 China International Conference on Electricity Distribution (CICED), 1640–1646 (2022)

Davidson, C. C., Whitehouse, R. S., Barker, C. D., et al.: A new ultra-fast HVDC circuit breaker for meshed DC networks. 11th IET Inter. Conf. on AC and DC Power Transmission., Birmingham, 1–7 (2015)

Wang, J., et al.: Current limiting and capacitor commutated hybrid DC circuit breaker. Power Syst. Protect. Control. 46(24), 180–186 (2018)

Arvin, T., He J., Waters, K.: Solid-state DC circuit breaker based on HTS fault current limiter and SiC MOSFET modules. 2022 IEEE Transportation Electrification Conference & Expo (ITEC), 1111–1116 (2022)

Ma, D., Chen, W., Ye, H., Xue, C., et al.: An assembly high voltage DC circuit breaker based on pre-charged capacitors. 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), 1–4 (2018)

Pei, X., Tang, G., Zhang, S.: Sequential auto-reclosing strategy for hybrid HVDC breakers in VSC-based DC grids. J. Mod. Power Syst. Clean Energy 7(3), 633–643 (2018)

Marwaha, M., et al.: SCR-Based bidirectional circuit breaker for DC system protection with soft reclosing capability. IEEE Trans. Ind. Electron (2022). https://doi.org/10.1109/TIE.2022.3187585

Shu, J., Wang, S, Liu, T.: A soft reclosing model for hybrid DC circuit breaker in VSC-MTDC system. 2018 IEEE 4th Southern Power Electronics Conference (SPEC), 1–5 (2018)

Zhang, S., Zou, G., Xu, C., et al.: A reclosing scheme of hybrid DC circuit breaker for MMC-HVdc systems. IEEE J EM SEL TOP P 9(6), 7126–7137 (2021)

Song, G., Wang, T., Hussain, K.: DC line fault identification based on pulse injection from hybrid HVDC breaker. IEEE Trans. Power Del. 34(1), 271–280 (2019)

Song, G., et al.: Active injection for single-ended protection in DC grid using hybrid MMC. IEEE Trans. Power Del. 36(3), 1651–1662 (2021)

Acknowledgements

This work was supported by Key Research Project of Xinjiang Uygur Autonomous Region Colleges and Universities (XJEDU2021I009) and Excellent Doctoral Research and Innovation Project of Xinjiang University (XJU2022BS094).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sun, Y., Fan, Y. & Hou, J. Capacitor commutation type DC circuit breaker with fault character discrimination capability. J. Power Electron. 23, 1016–1027 (2023). https://doi.org/10.1007/s43236-023-00590-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-023-00590-7