Abstract

In this paper, a phase-shifted full-bridge (PSFB) converter with a coupled-inductor-based rectifier is presented. The proposed PSFB converter alleviates the circulating-current problem of conventional PSFB converters. As a result, it can operate with a larger effective duty-cycle over a wide range of input voltage or output load conditions. The transformer turn-ratio can be better designed in terms of the primary-side conduction loss and the secondary-rectifier voltage stress. Due to the reduced secondary voltage stress, diodes with a lower forward-voltage drop can be used in the rectifier of the proposed converter, which results in s reduction of the secondary-side conduction and snubber losses. With these advantages, the proposed converter can achieve a higher power-conversion efficiency when compared to conventional converters. To verify the effectiveness of the proposed converter, this paper presents the operating principle, dc analysis, and experimental results of a prototype converter built with the specification of a 1.0 kW, 300–400 V input, a 50 V output, and a 100 kHz switching frequency.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Recently, power electronics technology has been focusing on improving power density and power-conversion efficiency. For this, the use of advanced power semiconductor switches like GaNs or SiC MOSFETs has been considered [1,2,3,4]. In addition, new circuits that can improve the performance of existing converters have been developed to enhance power-conversion efficiency while improving or maintaining power density [5,6,7].

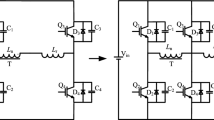

The phase-shifted full-bridge (PSFB) converter with a center-tapped transformer shown in Fig. 1 has many advantages such as zero-voltage switching (ZVS) operation without the help of any auxiliary circuits, clamped voltage stress, small RMS current stress of the primary switches, and low secondary-side conduction loss [8,9,10]. Due to these advantages, it has been one of the most promising topologies for low-voltage and high-current applications such as data-center power supplies, power supplies for communication equipment, and battery chargers for neighborhood electric vehicles [11,12,13]. Although the PSFB converter in Fig. 1 has been widely used in many applications, there exist many challenges when it comes to improving the performance of the converter. First, the ZVS operation of the lagging-leg switches in the PSFB converter fails under light load conditions. Figure 2 shows key waveforms of the PSFB converter in Fig. 1, where the lagging-leg switches are defined as Q3 and Q4 in the converter. The secondary rectifier stage is separated from the transformer primary side before Q3 or Q4 turn-off due to the zero-voltage interval of the voltage Vab, as shown in this figure. Therefore, the resonance between the series inductor Llk and the parasitic capacitors Coss3 and Coss4 occurs at the moment Q3 or Q4 turns off, and the zero-voltage switching of Q3 or Q4 can be achieved by this resonance. However, since the value of Llk is generally very small which makes the characteristic impedance of the resonant circuit become small, ZVS is not achieved as soon as the load drops even under slightly less than full load conditions. Due to this, its conversion efficiency is severely degraded when the load decreases [14,15,16]. Secondly, if the converter is suitable for wide operating ranges due to design considerations such as hold-up time requirements or wide output-voltage ranges like battery chargers, the operating duty-cycle becomes small under normal operating conditions and the freewheeling interval lengthens. As a result, the excessive circulating current appears on the primary side as shown in Fig. 2, which results in increasing the primary-side conduction loss and turn-off switching loss of the lagging-leg switches [17,18,19]. In addition, although the on-state of the switches Q1 and Q3 or Q2 and Q4 form a wide operating-duty in the Vab voltage waveform, the circulating current increases the duty loss Dloss and decreases the effective duty-cycle Deff, which contributes to the power transmission. As a result, the area of the transformer primary voltage Vpri, which is really transmitted to the transformer secondary coils, decreases. Thus, the desired output voltage is not obtained. To overcome this problem, the transformer turn-ratio n should be lower than the case of no circulating current, at which point both the primary-side current and secondary-side voltage stresses significantly increase [20].

Key waveforms of the PSFB converter in Fig. 1

Many PSFB converters have been presented to overcome the abovementioned disadvantages. To reduce the circulating current, the PSFB converters in [16, 20,21,22,23,24,25] require auxiliary circuits consisting of capacitors, diodes, and active switches in the secondary rectification circuit. The PSFB converters in [26, 27] deviate from the problem of circulating current by decreasing the value of a DC (direct current) blocking capacitor in series with a transformer. However, in this case, the voltage drop across the DC blocking capacitor is increased due to its small capacitance. Therefore, the transformer's primary voltage becomes lower. This makes it difficult to regulate the desired output voltage or current without an unfavorable design of the transformer turn-ratio in terms of primary-side current and secondary-side voltage stresses. The PSFB converters in [28,29,30,31,32] are integrated with other DC/DC converters such as half-bridge pulse-width-modulation (PWM) converters or LLC resonant converters to guarantee a wide ZVS range in the presence of load variations without the loss of an effective duty-cycle. As a result, the circulating current is alleviated and the secondary-side voltage stress is significantly reduced. However, they require two or more transformers to highlight their advantages. Although the performance can be improved by replacing the output inductor with a single coupled inductor, this solution is limited to PSFB converters with a full-bridge rectifier that uses four diodes [33].

This paper focuses on the development of new circuits for improving power-conversion efficiency while overcoming the abovementioned challenges of the PSFB converter in Fig. 1. Figure 3 shows the PSFB converter proposed in this paper for improving the performance of the converter in Fig. 1. As can be seen in Fig. 3, the primary-side structure of the proposed converter is the same as that of the conventional PSFB converter. Meanwhile, the rectification circuit is structured by rearranging the secondary circuit shown in Fig. 1, and adding an additional diode Da after replacing the output inductor with a coupled inductor. This structure reduces the circulating current in Fig. 1 and enables the proposed PSFB converter to operate with larger effective duty-cycles over a wide operating range. Due to this, the transformer turn-ratio can be designed better in terms of primary-side conduction loss and secondary-rectifier voltage stress. Due to the reduction in the secondary-side voltage stress, diodes with a lower forward-voltage drop can be used in the proposed converter, which results in an additional reduction of the power loss on the secondary side. With these advantages, the proposed converter can achieve a higher power-conversion efficiency when compared to the conventional converter in Fig. 1.

The remainder of this paper is organized as follows. In Sect. 2, both a description and the operation principle of the proposed converter are presented. Relevant analysis results are given in Sect. 3. In Sect. 4, experimental results and a comparison of the conventional and the proposed converters are presented. Finally, some conclusions are made in Sect. 5.

2 Operation principle

Figure 4 shows key operating waveforms of the proposed converter in the steady-state. The proposed converter has 18 operation modes in one switching cycle. However, only the operation during the first half-switching cycle is analyzed as in Fig. 5 due to symmetry. For analyzing the steady-state operation, the following assumptions are made.

-

The input and output voltages are constant with respect to Vin and Vout.

-

The parasitic capacitors of the switches have the same capacitance as Coss.

-

The coupled inductor has a turn-ratio of 1:1. In addition, it has turns of NCI, a magnetizing inductance of LCI, and a high coupling-coefficient.

-

The influence of parasitic capacitors of rectifier diodes is ignored.

Mode 1 [t0, t1]: In mode 1, the switches Q1 and Q3 are in the on-state. Hence, the primary-winding voltage of the transformer VP is the input voltage Vin, which is transmitted to the secondary windings by the transformer turn-ratio. In addition, the diode D1 is forward-biased and the diodes D2 and Da are reverse-biased. Then, the voltage across the coupled inductor VCI becomes Vin/n − Vout, which linearly increases the current flowing via the magnetizing inductance of the coupled inductor. The primary-side current iP is the sum of the transformer magnetizing currents iLm and iCI flowing through the coupled inductor. The current and voltage equations in this mode are as follows.

Mode 2 [t1, t2]: Mode 2 starts when the switch Q3 is switched off. Then, the parasitic capacitors COSS3 and COSS4 of the leading-leg switches Q3 and Q4 are charged or discharged. The voltages across Q3, Q4 and VP can be expressed as follows.

During this mode, the primary-side voltage VP linearly decreases from the input voltage as in Eq. (5). Under this influence, the coupled inductor voltage VCI linearly decreases toward − Vout/2 and the voltage across Da, VDa also decreases toward 0 V. Then, VDa becomes 0 V at the end of this mode and diode Da turns on.

Mode 3 [t2, t3]: Mode 3 starts with the turn-on of the auxiliary diode Da in the rectifier circuit. At this time, the voltage VP is 0 V and the body diode of Q4 is conducted. Figure 6c shows an equivalent circuit for the analysis of this mode. Assuming that the two leakage inductances in the coupled inductor have the same value, the voltages in the equivalent circuit can be determined as follows:

From Eq. (8), it is noted that since the leakage inductance of the coupled inductor is very small due to its high coupling coefficient design, the transformer leakage inductance voltage VLlkg is nearly 50% of the negative output voltage with a turn-ratio. Then, the transformer primary current iP can be determined as follows:

Equation (9) gives the currents of the coupled inductor as follows:

Mode 4 [t3, t4]: Mode 4 starts when Q4 turns on under zero-voltage switching (ZVS). During this mode, the voltages applied to the leakage inductance of the transformer are the same as the analysis results from Mode 3. Therefore, the currents flowing through the coupled inductor continue to linearly decrease or increase as in Eqs. (10) and (11). The current of the rectifier diode D1 also decreases linearly.

During the interval from time t2 to t4, the primary-side current iP is not transmitted to the transformer secondary-side since VP is 0 V. It only circulates through Q1, Q4, and the transformer. However, due to the negative output voltage applied to the transformer leakage inductance as in Eq. (9), iP continues to decrease until it reaches the transformer magnetizing current iLm as shown in Fig. 4. This mechanism verifies that the proposed converter has smaller circulating currents when compared to the conventional PSFB converter. This fact will be explained in detail in the next section.

Mode 5 [t4, t5]: Mode 5 starts when iP reaches iLm. At this moment, the diode D1 is turned off with zero current and the currents via the coupled inductor become the same. In this mode, the voltage VLm becomes 0 V and iLm only flows in the primary side. The currents of the coupled inductor can be expressed as follows:

Mode 6 [t5, t6]: Mode 6 starts when the switch Q1 is turned off. Then, the parasitic capacitors of the lagging-leg switches Q1 and Q2, COSS1 and COSS2 are charged or discharged. The voltages across Q1 and Q2 can be expressed as follows:

In this mode, the primary voltages VP and VLm linearly decrease from 0 V to a negative input voltage as shown in Eq. (13). When VLm reaches − nVout/2, the rectifier diode D2 voltage becomes 0 V and D2 conducts.

Mode 7 [t6, t7]: Mode 7 starts when the diode D2 conducts in mode 6. Figure 6g shows an equivalent circuit for the analysis of this mode. From this analysis, the voltages and current in this mode can be determined as follows:

From Eqs. (14), (15), and (17), it is noted that the voltages of the lagging-leg switches increase or decrease in sinusoidal form due to the resonance between the transformer leakage inductance and the switch parasitic capacitances. This mode ends when the voltage of Q2 reaches zero.

Mode 8 [t7, t8]: Mode 8 starts when the Q2 voltage becomes 0 V. Figure 6h shows an equivalent circuit for an analysis of mode 8. Analyzing the equivalent circuit gives the voltages in this figure as follows:

In Eq. (19), if the coupling coefficient of the coupled inductor is high and its leakage inductance is exceedingly small, the transformer leakage inductance voltage VLlkg is the sum of the negative input voltage and half of the output voltage with a turn-ratio and is negative. Then, the transformer primary current iP in this mode can be determined as follows:

Equation (9) gives the currents of the coupled inductor as follows:

Mode 9 [t8, t9]: Mode 9 starts when Q2 is turned on under ZVS. Since the equivalent circuit explaining the operation of this mode is the same as that shown in Fig. 6c, the voltage and current equations in this mode are identical to the analysis in mode 8. This mode ends when the auxiliary diode Da reaches zero, and D2 supplies all of the load current.

3 Relevant analysis results

3.1 Circulating current

Figure 7 shows a comparison of operation waveforms of the proposed and conventional converters.

Figure 7a shows the circulating current flowing through the transformer and the switches for an interval with a primary-side voltage VP of 0 V, which is indicated by the shaded areas in the figure. This current, which does not contribute to power transmission, continuously flows through the inverter-stage switches and the transformer primary-winding, which results in additional conduction loss. In addition, this current increases the turn-off switching loss when the lagging-leg switches Q1 and Q2 are turned off.

Figure 7b shows the circulating current in the proposed converter, which is indicated by the shaded area in the figure. From a comparison with the conventional converter, it can be clearly seen that the proposed converter features a smaller circulating current when compared to the conventional converter. Its principle can be explained by the following mechanism. In the mode where the primary-side voltage VP is 0 V, the auxiliary diode Da is in the on-state. Then, the transformer leakage inductance gets a voltage that resets the current flowing to 0A from the output stage due to the coupled-inductor circuit. As a result, the primary current iP is reset to the transformer magnetizing current iLm for an interval of with a primary-side voltage VP of 0 V. This results in a reduced circulating current and lower current stress when compared to the conventional converter.

3.2 Voltage gain analysis

As shown in Fig. 4, the voltage applied to the coupled inductor VCI is Vin/n − Vout during the power transmission mode and − Vout/2 during the freewheeling mode. Then, the voltage gain of the proposed circuit can be obtained with the voltage-second-balance principle as follows:

In Eq. (23), Deff refers to an effective duty-cycle. Figure 8 shows the normalized voltage gain according to the effective duty-cycle. From this analysis, it can be clearly seen that the proposed converter has higher voltage gains when compared to the conventional converter. This advantage enables the proposed converter to have a much better turn-ratio n in terms of primary-side current and secondary-side voltage stresses when compared to the conventional converter.

3.3 Voltage stress analysis

The rectifier diodes in the conventional and proposed converters experience the highest voltage stress in the power transmission mode. In the case of the conventional converter with a center-tap rectifier circuit shown in Fig. 1, the rectifier diode has voltage stress of more than two times the voltage of the secondary-side windings of the transformer when considering that voltage rigging occurred by the parasitic components. This can be expressed as the following equation:

The voltage stress applied to the rectifier diode in the proposed converter is similar to Eq. (25). However, as explained in the previous part, the proposed converter can be designed with a higher transformer turn-ratio n than the conventional converter under the same duty-cycle due to higher voltage gains. As a result, the voltage stress of the rectifier diodes in the proposed circuit is lower than that of the conventional converter. This means that when an RCD snubber circuit with the same time-constant is used, the snubber loss in the proposed circuit is much lower than that in the conventional converter. In addition, diodes with lower forward-voltage drop can be used for the proposed converter due to its lower voltage stress, which can enable an improvement of the conduction loss at the rectifier stage.

3.4 ZVS condition analysis

Zero-voltage switching (ZVS) of the leading-leg switches in the proposed converter can be easily achieved over a wide load variation due to the large magnetizing inductance of the coupled inductor. This principle is similar to that of the leading-leg switches in the conventional converter [16, 28].

The ZVS operation of the lagging-leg switches in the proposed converter was explained in the analysis of mode 7 in the previous section. From Eq. (14) and Fig. 4, the ZVS condition for the lagging-leg switches of the proposed converter can be set up as follows:

The iP(t6) in Eq. (14) can be easily obtained as in Eq. (15) by analyzing Fig. 4.

When assuming the interval of mode 7 with Tdead, which is the dead-time between Q1 and Q2, the ZVS condition of Eq. (25) can be expressed as follows:

By putting Eq. (26) into Eq. (27), the design equation for the transformer magnetizing inductance guaranteeing the ZVS operation of the lagging-leg switches can be obtained as follows:

3.5 Duty-cycle loss

The conventional converter in Fig. 1 requires an additional inductor in series with the transformer to extend the ZVS range of the lagging-leg switches. However, this additional inductor reduces the effective duty-cycle and narrows the power transmission interval. Then, the wanted output voltage or current cannot be achieved. To compensate for this, the transformer turn-ratio n should be lowered, which greatly increases the primary-side current and secondary-side voltage stresses. It also causes an increase in snubber loss and conduction loss.

On the other hand, ZVS of the lagging-leg switches in the proposed converter can be extended by decreasing the transformer magnetizing inductance as in Eq. (28). The transformer magnetizing inductance has the advantage of not generating the problems related to duty-cycle loss since it forms a parallel connection with the output load.

4 Experimental results

To demonstrate the validity of the proposed converter, prototype converters were designed and manufactured with the following specifications. To mitigate voltage overshoots and oscillation, prototype converters were built by adding snubber circuits. The design specifications for the prototypes are as follows:**

-

Input voltage: Vin = 300–400 V

-

Output voltage: Vout = 50 V

-

Maximum output current: Iout(max) = 20 A

-

Switching frequency: ƒs = 100 kHz

Table 1 shows a list of the components used to build the prototypes, and Fig. 9 shows photos of the manufactured converters.

The equation for designing the coupled inductor in the proposed converter can be set up from Fig. 4, Eq. (1) and (2).

For a small core loss, an appropriate current ripple is selected. Then, the magnetizing inductance LCI can be designed with Eq. (29). The size of the core for the coupled inductor can be selected with the required LCI and the magnitude of the current flowing through the coupled inductor. Once the size of the core is determined, the turns of the windings can be determined from Faraday’s law from the effective cross-sectional area of the core and the level of the voltage across the coupled inductor in Fig. 4. The proposed converter needs a coupled inductor with a turn-ratio of 1:1 and a high coupling coefficient. For a high coupling coefficient, the coupled inductor for the proposed converter was made with the bifilar winding method in [34].

The prototype converters were regulated with a TMS320F28335-based controller.

4.1 Waveforms

Figures 10 and 11 show key operating-waveforms of the proposed and conventional converters at a 300 V or 400 V input and 50 V and 20 A outputs. From Figs. 10b and 11b, it is confirmed that all of the measured waveforms follow the operation analyzed in Fig. 4 and Sect. 2 well. It is also confirmed that the proposed converter has a significantly reduced circulating current when compared to the conventional converter. In addition, it is clearly verified from the value of Ip(rms) in the figures that the primary RMS (root-mean-square) current stress is decreased due to the reduction of the circulating current.

Figures 12, 13, and 14 show the inverter output voltage Vp(t), primary current ip(t), and rectifier diode voltages of the proposed converter at input voltages of 300 V and 400 V according to the load currents. These experiments verify that the ZVS of the lagging-leg switches in the proposed converter can be effectively achieved over wide load conditions.

4.2 Diode voltage stress

Figure 15 shows the voltage stress of the rectifier diodes at an input voltage of 400 V and an output of 50 V and 1 kW using the same snubber circuit. The snubber circuit design can be seen in Table 1. As shown by the experimental results in Fig. 15, since the proposed converter is made with a higher transformer turn-ratio n due to higher voltage gains than the conventional converter, it is confirmed that the voltage stress is reduced by more than 39 V. The reduced voltage stress means that the proposed converter has a lower snubber loss when compared to the proposed converter.

4.3 Efficiency

Figure 16 shows the efficiency measured using a power analyzer (WT500, YOKOGAWA) under input voltage 300 V and 100% load conditions. As can be seen from these experimental results, the proposed converter achieves a higher power conversion efficiency. Figure 17 shows an efficiency curve according to the output load conditions. As shown in Fig. 17, the proposed converter has a maximum efficiency of 94.7%, and its efficiency is greatly improved when compared to the conventional converter. This is due to the fact that the conduction loss of the proposed converter is reduced as a result of the reduction in the circulating current and the turn-off switching loss. In addition, the reduction in the snubber loss due to lower voltage stress on the secondary-side rectifier diode also contributes to improved efficiency. Figure 18 shows the loss reduction factor of the proposed converter by analyzing the losses for each of the elements in the proposed and conventional converters.

5 Conclusions

This paper presents a PSFB converter that can improve the performance of a PSFB converter with a center-tap rectifier circuit. To achieve this improvement, the proposed converter relaces the output inductor with a single coupled inductor and adds an auxiliary diode. With these structural changes, the proposed converter achieves the following advantages:

-

(1)

Reductions in the conduction loss and turn-off switching loss due to a reduction in the circulating current.

-

(2)

Reductions in the rectifier diode voltage stress and snubber loss by the feature of a higher voltage gain.

-

(3)

Soft-switching of the lagging-leg switches independent of load conditions due to the transformer magnetizing inductance.

Due to the above advantages, the proposed converter can achieve higher efficiency than the conventional converter. To confirm the superiority of the proposed converter, this paper presents the operating principle, steady-state analysis, and experimental results under a 1.0 kW, 300–400 V input voltage, and a 50 V output voltage. From the theoretical analysis and experimental results, it can be concluded that the proposed converter is applicable to low voltage, high current, and wide input or output operating applications such as data-center power supplies, communication equipment power supplies, and battery chargers for neighborhood electric vehicles.

References

Wang, L., Zhu, Q., Yu, W., Huang, A.Q.: Efficiency and conducted EMI evaluation of a single-phase power factor correction boost converter using stage-of-the-art SiC mosfet and SiC diode. IEEE Trans. Ind. Appl. 55(6), 7745–7756 (2019)

Liu, Z., Li, B., Lee, F.C., Li, Q.: High-efficiency high-density critical mode rectifier/inverter for WBG-device-based on-board charger. IEEE Trans. Ind. Electron. 64(11), 9114–9123 (2017)

Elrajoubi, A.M., Ang, S.S., George, K.: Design and analysis of a new GaN-based AC/DC converter for battery charging application. IEEE Trans. Ind. Appl. 55(4), 4044–4052 (2019)

Whitaker, B., Barkley, A., Cole, Z., Passmore, B., Martin, D., McNutt, T.R., Lostetter, A.B., Lee, J.S., Shiozaki, K.: A high-density, high-efficiency, isolated on-board vehicle battery charger utilizing silicon carbide power devices. IEEE Trans. Power Electron. 29(5), 2606–26177 (2014)

Banaei, M.R., Sani, S.G.: Analysis and implementation of a new SEPIC-based single-switch buck-boost DC-DC converter with continuous input current. IEEE Trans. Power Electron. 33(12), 10317–10325 (2018)

Shi, K., Zhang, D., Zhou, Z., Zhang, M., Zhang, D., Gu, Y.: A novel phase-shift dual full-bridge converter with full soft-switching range and wide conversion range. IEEE Trans. Power Electron. 31(11), 7747–7760 (2016)

Ravi, V., Kanamarlapudi, K., Wang, B., Kandasamy, N.K., So, P.L.: A new ZVS full-bridge DC-DC converter for battery charging with reduced losses over full-load range. IEEE Trans. Ind. Appl. 54(1), 571–579 (2018)

Koo, G.B., Moon, G.W., Youn, M.J.: New zero-voltage-switching phase-shift full-bridge converter with low conduction losses. IEEE Trans. Ind. Electron. 52(1), 228–235 (2005)

Chen, B.Y., Lai, Y.S.: Switching control technique of phase-shift-controlled full-bridge converter to improve efficiency under light-load and standby conditions without additional auxiliary components. IEEE Trans. Power Electron. 25(4), 1001–1012 (2010)

Lin, S.Y., Chen, C.L.: Analysis and design for RCD clamped snubber used in output rectifier of phase-shift full-bridge ZVS converters. IEEE Trans. Ind. Electron. 45(2), 358–359 (1998)

Woo, J., Kim, D., Kim, C., Moon, G.: A simple switching control technique for improving light load efficiency in a phase-shifted full-bridge converter with a server power system. IEEE Trans. Power Electron. 29(4), 1562–1566 (2014)

Kasper, M., Bortis, D., Deboy, G., Kolar, J.W.: Design of a highly efficient (97.7%) and very compact (2.2 kW/dm 3) isolated AC–DC telecom power supply module based on the multicell ISOP converter approach. IEEE Trans. Power Electron 32(10), 7750–7769 (2017)

Kim, Y., Oh, C., Sung, W., Lee, B.: Topology and control scheme of OBC–LDC integrated power unit for electric vehicles. IEEE Trans. Power Electron. 32(3), 1731–1743 (2017)

Dudrik, J., Trip, N.D.: Soft-Switching PS-PWM DC-DC converter for full-load range applications. IEEE Trans. Ind. Electron. 57(8), 2807–2814 (2010)

Mousavi, A., Das, P., Moschopouos, G.: A ZVS pulsewidth modulation full-bridge converter with a low-RMS-current resonant auxiliary circuit. IEEE Trans. Power Electron. 31(6), 4031–4047 (2016)

Lee, I.O., Moon, G.W.: Soft-switching DC/DC converter with a full ZVS range and reduced output filter for high-voltage applications. IEEE Trans. Power Electron. 28(1), 112–122 (2013)

Gu, B., Lai, J., Kees, N., Zheng, C.: Hybrid-switching full-bridge DC–DC converter with minimal voltage stress of bridge rectifier, reduced circulating losses, and filter requirement for electric vehicle battery chargers. IEEE Trans. Power Electron. 28(3), 1132–1144 (2013)

Chen, Z., Chen, Y., Chen, Q.: Isolated series-capacitor-based full-bridge converter with reduced circulating losses and wide soft switching range. IEEE J. Emerg. Sel. Top. Power Electron. 7(2), 1272–1285 (2019)

Wu, X., Xie, X., Zhang, J., Zhao, R., Qian, Z.: Soft switched full bridge DC–DC converter with reduced circulating loss and filter requirement. IEEE Trans. Power Electron. 22(5), 1949–1955 (2007)

Lee, I., Moon, G.: Phase-shifted PWM converter with a wide zvs range and reduced circulating current. IEEE Trans. Power Electron. 28(2), 908–919 (2013)

Song, T.T., Huang, N.: A novel zero-voltage and zero-current-switching full-bridge PWM converter. IEEE Trans. Power Electron. 20(2), 286–291 (2005)

Seok, K., Kwon, B.: An improved zero-voltage and zero-current-switching full-bridge PWM converter using a simple resonant circuit. IEEE Trans. Ind. Electron. 48(6), 1205–1209 (2001)

Kim, E., Kim, Y.: A ZVZCS PWM FB DC/DC converter using a modified energy-recovery snubber. IEEE Trans. Ind. Electron. 49(5), 1120–1127 (2002)

Wu, X., Xie, X., Zhao, C., Qian, Z., Zhao, R.: Low voltage and current stress ZVZCS full bridge DC-DC converter using center tapped rectifier reset. IEEE Trans. Ind. Electron. 55(3), 1470–1477 (2008)

Cha, H., Chen, L., Ding, R., Tang, Q., Peng, F.Z.: An alternative energy recovery clamp circuit for full-bridge PWM converters with wide ranges of input voltage. IEEE Trans. Power Electron. 23(6), 2828–2837 (2008)

Ruan, X., Yan, Y.: A novel zero-voltage and zero-current-switching PWM full-bridge converter using two diodes in series with the lagging leg. IEEE Trans. Ind. Electron. 48(4), 777–785 (2001)

Park, K., Kim, C., Moon, G., Youn, M.: Voltage oscillation reduction technique for phase-shift full-bride converter. IEEE Trans. Ind. Electron. 54(5), 2779–2790 (2007)

Lee, I.O., Moon, G.W.: Half-bridge integrated ZVS full-bridge converter with reduced conduction loss for electric vehicle battery chargers. IEEE Trans. Ind. Electron. 61(8), 3978–3988 (2014)

Ayyanar, R., Mohan, N.: Novel soft-switched DC-DC converter with full ZVS-range and reduced filter requirement–part I: Regulated-output applications. IEEE Trans. Power Electron. 16(2), 184–192 (2001)

Ayyanar, R., Mohan, N.: Novel soft-switched DC-DC converter with Full ZVS-range and reduced filter requirement–part II: constant-input, variable-output applications. IEEE Trans. Power Electron. 16(2), 193–200 (2001)

Lee, I.: Hybrid PWM-resonant converter for electric vehicle on-board battery chargers. IEEE Trans. Power Electron. 31(5), 3639–3649 (2016)

Dao, L.A., Dao, N.D., Lee, D.C.: High-efficiency hybrid LLC resonant converter for on-board chargers of plug-in electric vehicles. IEEE Trans. Power Electron. 35(8), 8324–8334 (2020)

Han, J., Moon, G.: High-efficiency phase-shifted full-bridge converter with a new coupled inductor rectifier (CIR). IEEE Trans. Power Electron. 34(9), 8468–8480 (2019)

Jung, J.H.: Bifilar winding of a center-tapped transformer including integrated resonant inductance of LLC resonant converter. IEEE Trans. Power Electron. 28(2), 615–620 (2013)

Acknowledgements

This paper is the result of a study conducted with the support of the Ministry of Trade, Industry and Energy and the Korea Institute of Trade, Industry and Technology Promotion’s National Innovation Cluster Project (P0015364).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Choi, BG., Lee, WS., Park, JU. et al. Phase-shifted full-bridge converter with coupled-inductor-based rectifier. J. Power Electron. 21, 1585–1599 (2021). https://doi.org/10.1007/s43236-021-00295-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-021-00295-9