Abstract

The present paper proposes a kind of interleaved high step-up converter without the coupled inductor. The converter consists of two basic boost converters and two voltage multiplier cells. The proposed converter has a lower input current rippled by means of the interleaving method. The voltage stress of the switches remains at a low level. The theoretical analysis and operation intervals of the proposed high step-up converter are presented. The voltage gain of the converter is higher than that of the similar converters. The converter is simulated in the OrCAD software. In this converter, the inductors operate in a continuous flow mode CCM. In this topology, the input voltage is 40 V, which is converted to the output 400 V with a power of 200 W and a frequency of 100 kHz. The voltage stress of the switches is 120 V, which is much lower than the output 400 V. Finally, the experimental results are presented to validate the effectiveness of the proposed converter.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The importance of renewable energy sources has been increased recently due to their benefits, such as the lack of limitations and environmental pollution, as well as their high reliability. Sunlight is known as a clean and free renewable energy source (Shimizu et al. 2003). Photovoltaic (PV) cells are utilized to convert solar energy into electrical energy (Scarpa et al. 2009). Since the voltage level generated by the PV cells is small, the DC–DC voltage converters can be used to boost it to the desired level (Salary et al. 2017). Accordingly, the voltage level required by the inverter input to convert the DC voltage to AC voltage can be attained (Figueres et al. 2009).

The DC voltage generated by the PV module is usually enhanced by a DC–DC converter to reach the desired level. Since most electric consumers need AC voltage, the amplified DC voltage is converted to the AC voltage by an inverter. (Figueres et al. 2009; Chen et al. 2018; Liu and Xhang 2019).

Various types of boost converters are employed to increase the voltage level. The conventional boost converter can produce a gain no more than 5 (Lopez et al. 2006). Moreover, it leads to hard switching, which increases converter losses at high frequencies. On the other hand, due to high stress in the diode voltage and the converter switch, the elements that are at reasonable prices have poor quality. In this regard, the conductive and reverse recovery losses of the diodes are also problematic. This requires us to employ optimal interleaved boost converters. These converters are generally divided into several categories. The first one is the conventional interleaved boost converter, which contains a series of auxiliary circuits added to each phase consisting of an active key, a capacitor, and an inductor. The main switches are naturally switched on at zero current, and the output diodes’ reverse voltage problem is reduced due to the performance of the discontinuous flow mode (DCM). The auxiliary commutation circuits provide a transient zero current mode when the main switch is off. However, the variable frequency control is obligatory for this converter, which makes it difficult to design a filter to reduce electromagnetic interference (Jemei et al. 2008). The second category is the interleaved boost converter coupled with an inductor. In these converters, the output diodes’ reverse voltage problem is reduced. In addition, the coupled inductor’s leakage inductor leads to zero current switching (ZCS)of the switches. These switches are switched off rigorously. The circuit current ripple in negatively coupled inductors is high because the circuit operates in a discontinuous mode, and the switching loss is low due to zero switching operation in all switching intervals (Todorovic et al. 2008). The third category is a three-layer boost converter, which can reduce the voltage stress of semiconductor devices by half, which makes it more suitable for high output voltage applications compared with conventional two-layer boost converters. Switching losses and the noise induced by electromagnetic interference (EMI) can be reduced by low voltage stress. The activated switches work well in hard switching and increase the resonance inductor of the voltage stress (Hwu and Yau 2009). The last category contains new DC–DC boost converters with a coupled inductor and multiplier circuits. In this converter, a high voltage gain with appropriate duty factor and low voltage stress in power switches are provided. Furthermore, the stored energy in the inductively coupled inductor’s leakage inductor can be returned to the converter output. The steady-state voltage of the two switches is lower than the output voltage. However, the voltage uplift is observed in the switches when they are switched off (Chang et al. 2017; Franceschini et al. 2008). The interleaved high step-up converters based on diode–capacitor multiplier are presented in Zhou et al. (2014) and Yang et al. (2009). These papers propose transformerless converters to achieve high voltage gain without an extremely high duty ratio. The main drawback of these converters is high voltage stress of the switches and diodes.

The remainder of this study is organized as follows. Section 2 introduces an interleaved boost converter to increase the voltage gain without using coupled inductors. Besides, an enhanced arrangement of the boost converter elements and its auxiliary components are offered to increase the gain and reduce the voltage stress while the input current ripple of the converter is kept low. Also, the operation intervals are demonstrated. Section 3 contains the design of considerations and the formula in detail. In Sect. 4, the results in the OrCAD software are utilized to simulate and evaluate the performance of the proposed converter. Section 5includes the experimental results obtained from an implemented laboratory system. They are also provided to validate the accuracy of this converter. Finally, Sect. 6 offers the conclusion of this study.

2 The Proposed Converter and Its Operating Intervals

2.1 CCM Operation

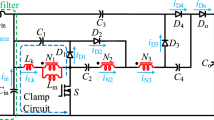

In this section, a new high-gain converter is introduced. Figure 1 shows the circuit of the proposed high-gain interleaved converter. In this converter, the inductor L1, switch S1, diode D3, and capacitor Co1 belong to one of the boost converters, while inductor L2, switch S2, diode D6, and capacitor Co2 belong to the other one. As a result, diodes D1 and D2, capacitors C1 and C2, and inductor La1 form the switching capacitor circuit that increases the employed voltage for one of these converters. On the other hand, diodes D3, D4, capacitors C3, and C4, and inductor La2 form the switching capacitor circuit that increases the employed voltage for the other one. In the proposed converter, the switches are switched according to the desired patterns. In this study, these patterns are considered as two pulses with the same duty factor and 180° phase shift; therefore, the input current ripple and the size of input filter can be effectively reduced (Chen and Lin 2015). Unlike the other switched capacitor-based high-gain interleaved boost converters, there is no limitation on the duty factor in the proposed converter. Moreover, the converter works correctly for all the task coefficients larger or smaller than 0.5.

The converter’s operation is divided into six steps, which are adopted successively in each switching cycle. Figure 2 shows the current and voltage curves of the critical components in the proposed converter.

2.1.1 Interval 1: t 0–t 1

In this step, both switches of the proposed converter are switched on. The voltage is equal to the input voltage of the two-terminal inductors L1 and L2, where their current linearly increases. The C2 capacitor charges the capacitor C1 through C2-D2-La1-C1-S1. The C4 capacitor also charges the capacitor C3 through C4-S2-C3-La2-D5. In this step, the load’s current is also determined by Co2-Vin-Co1-Ro. This situation ends with switching the switch S1off. Now, the converter enters the next step. The equivalent circuit of this interval is presented in the Appendix section. The current equations for the inductors L1, L2, La1, and La2are given as:

The process duration could be considered as (D − 0.5)Tsw.

2.1.2 Interval 2: t 1–t 2

At t1, the switch S1 switches off. Afterward, the inductor L1 switches the diodes D1 and D3 on, charges the capacitor C2 through Vin-L1-D1-C2, and charges the capacitor Co1 through Vin–L1–C1–D3–Co1. The voltage of the capacitor C1 called VC1 is adjusted at the two terminals of the inductor La1 through C1-La1-D2-D1. Accordingly, the currents of inductor La1 and diode D2 linearly decrease with a steep slope until they tend to zero. This leads to switching off the diode D2 under ZCS conditions. The current of the inductor L1 decreases slowly with a slight slope. The same conditions are true for another circuit branch. In this case, the following current equations could be written:

2.1.3 Interval 3: t 2–t 3

At t2, diode D2 is switched off, and the converter enters the third stage of its operation. As shown in Fig. 3, in this stage, the switches S1 and S2 are off and on, respectively. A part of the inductor current L1 charges the capacitor C2 through diode D1, while another part charges the output capacitor through diode D3. The operation of another branch is also similar. Now, the current of inductor L1 linearly decreases with slow slope, while the current of inductor L2 increases. In this case, the current equations are given as the following (consider that the duration process is (1 − D)Tsw):

2.1.4 Interval 4: t 3–t 4

At t3, S1 is switched on, and the converter enters this step. As shown in Figs. 3, 4, and 5, the converter operation is similar to the first step. This means that the input voltage is placed at the two terminals of the inductor L1, which increases the current linearly with a slow slope. Moreover, the voltage shift of the capacitors C2 and C1 is placed at the two terminals of the inductor La1 and leads to an increase in the inductor current with another slow slope. In this case, the essential current equations are given as follows. The converter remains in this state until S2 is switched off. The duration of this process is considered as (1 − D)·Tsw.

2.1.5 Interval 5: t 4–t 5

At t4, the switch S2 in the converter is switched off, and the converter enters this step. In this case, inductor L2 charges the capacitors C4 and Co2 through the diodes D4 and D6, respectively. Since diodes D4 and D5 are switched on, the voltage of the capacitor C3 is positioned at two terminals of the inductor La2. This reduces its current by a steep slope. This phase lasts for a short time. In this case, the operation of the upper branch of the converter is similar to the corresponding one in the previous step. The important equations for the convertor elements are presented as follows:

2.1.6 Interval 6: t 5–t 6

This stage of the converter operation begins when diode D5 is switched off. In this phase of the converter operation in the upper branch, switch S1 is on, and the current of the inductor L1 increases linearly on the path Vin–L1–S1. The current of the inductor La1 also linearly increases on the path C2–D2–La1–C1–S1. Thus, the capacitor C1 will be charged. In the lower branch, a part of the inductor L2 charges the capacitor C4 through Vin–C4–D4–L2, while another part charges the output capacitor through Vin–Co2–D6–C3–L2. The current of the inductor L2 decreases linearly with a slow slope. The main equations for the convertor elements are given as:

Upon the completion of Step 6, the converter accomplishes a full switching cycle, and the mentioned six steps are repeated, subsequently.

2.2 Boundary Operation Between CCM and DCM

If the proposed converter is operated in boundary condition, the minimum value of the inductor currents at CCM condition reaches zero. For inductor L2, the minimum value of current is:

Therefore, the minimum value of inductor that the converter is operated in CCM condition is given as:

2.3 DCM Operation

In this condition, the inductor current iL2 is increased in interval 0 to DT and decreased in interval DT to D1T. This current reached zero at (D + D1)T. The average value of iL2 is computed as:

Therefore, D1 is derived as follows:

By using the volt-second balance principle on La2, the following equation can be obtained:

Substituting (26) into (27), the voltage gain is derived as:

3 Design Considerations

The voltage values of the capacitors C1, C2, C3, C4, Co1, and Co2 are obtained from the volt-sec balance equations for the inductors L1 and L2. The voltage equations for these capacitors are given as follows:

Voltage gain of the DC–DC converter

By applying the KVL law in the cycle Vin–VCo1–Vo–VCo2, the following equation could be obtained:

Replacing VCo1 and VCo2 from (30) in (31), and simplifying it, gives

Considering the converter operation values at the concerned intervals in the previous section and the capacitor voltage equations, the following relations for the voltage stresses across each of the switches could be obtained:

The voltage stresses across each of the diodes are also calculated as:

Figure 3 shows the comparison of the voltage gain of the proposed converter with other converters. As shown in this figure, the converter’s voltage gain is higher than that of the similar converters (Table 1).

The converter’s switches and diodes are selected in accordance with the converter’s power level and their voltage stress equations. The converter’s inductors for the concerned current ripples could be calculated from the following equation:

To obtain the design equations of the converter’s capacitors, the input power equation is considered as:

Given the gain equation of the converter, the following equation could be employed to replace the input voltage in the above equation.

Thus, we have:

The average current in each inductor is equal to the corresponding one in the others. Or

When the switch S1 is off within a period of (1 − D)Tsw, an average current of Iinavg/2 passes through the capacitor C2. According to the capacitor’s voltage load equation, the capacitor C2 for the voltage variation of ΔVC2 over the given interval could be calculated as:

Similarly, the design equations of the capacitors C1, C3, and C4 are given as:

The output capacitors Co1 and Co2 in a switching cycle must supply the output load current over the period (D)·Tsw. Since the output capacitors are in series, each capacitor value for a voltage variation of ΔVo over a given interval could be obtained as:

To design the inductors La1 and La2, it should be noted that when the switch S1 is on, an approximate voltage of 00.5(∆VC1 + ∆VC2) is created at the two terminals of the inductor La1 that increases the current. If the inductor’s increased current value is considered as ∆ILa1, the inductor’s value could be calculated as:

According to the above equation, an appropriate inductor value could be obtained by considering a small current variation in the inductor to prevent a significant increase in the switch stress. It is worth noting that the inductor value is generally in micro-Henry and small due to the small voltage applied to this inductor. Hence, this inductor could not significantly increase the circuit volume. The value of the inductor La2 is determined similar to that mentioned for the inductor La1.

4 Simulation Result

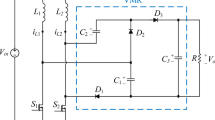

To evaluate the efficiency of the proposed converter and verify its accuracy, it is simulated with the OrCAD software. The converter is designed and simulated for 40 V input voltage, 400 V output voltage, 200 W power level, and 100 kHz frequency. The size and type of the selected components are reported in Table 2. Figure 4 illustrates the scheme of the proposed converter in the OrCAD software.

Figure 5 shows the input and output voltages obtained from the simulation. As shown in Fig. 5, the proposed converter is well managed to convert the 40 V input voltage to the 400 V output voltage. Figure 6 presents the waveforms of the inductors L1 and L2 and the input current Iin. Accordingly, the inductors L1 and L2 operate in a continuous conduction mode (CCM). Moreover, the input current ripple is considerably smaller than the corresponding ones obtained for inductors L1 and L2.

5 Experimental Result

The experimental results of the proposed converter are presented in this section. It could be seen that the converter works appropriately in the simulator environment. Therefore, in order to evaluate the feasibility of the proposed converter, its laboratory sample is constructed. The elements similar to the simulated converter are utilized to construct the convertor. Moreover, a 200 W sample converter with 100 kHz switching frequency is prepared in the laboratory to convert the 40 V input voltage to the 400 V output voltage. Figure 7 shows the input and output voltages of the converter. Based on this figure, the converter is designed for about 67% duty factor. Thus, a high gain could be generated by the sample converter.

The current and voltage waveforms of switch S1in the sample converters are shown in Fig. 8. As could be seen from Fig. 8, the switches’ voltages are 120 V, which are considerably smaller than the 400 V output voltage. Furthermore, this figure illustrates that the switch voltage is limited when the switch is off, and there is no significant voltage fluctuation at its terminals. The voltage waveform and the current of the switch S2 in the simulated converter are similar to the corresponding ones shown in Fig. 9, with only 180° phase shift. The voltage stress of switch S2 is also 120 V.

Figures 10 and 11show the current and voltage waveforms of diodes D2 and D3 in the sample converter, respectively. Accordingly, it could be seen that the diodes’ voltages stress is 120 V that is significantly smaller than the output voltage. In addition, the reverse recovery current in the diodes is negligible. This means that high-speed low-voltage diodes could be employed for these diodes to reduce the converter’s losses.

The current and voltage waveforms of the diodes D4 to D6 are also shown in Figs. 9 and 10. The voltage stresses of these diodes are also about 120 V. Thus, high-speed low-voltage diodes are utilized.

The efficiency of the proposed converter in different loads is calculated in simulation. Figure 12 shows the comparison of efficiency between the proposed converter and converter in Zhou et al. (2014). As shown in this figure, the efficiency of the proposed converter is improved because the voltage stress of switches and diodes is very lower than converter in Zhou et al. (2014) and the conduction loss is reduced. In addition, the diodes of the proposed converter turn off under ZCS condition and the switching loss is reduced. Figure 13 shows the pie chart of component losses in the proposed converter for a 200(W) load. Figure 14 shows the image of implemented setup.

Comparison of efficiency between the proposed converter and converter in Zhou et al. (2014)

6 Conclusion

This paper introduced the proposed converter and describes its operation in detail. After describing its theoretical analysis, the simulation results and construction phases of the proposed converter are also provided. The efficiency of the proposed converter is improved by about 1.5% compared with the converter in Yang et al. (2009). Furthermore, the proposed converter can be implemented via elements with less voltage tolerance levels. Table 1 compares the proposed converter with the converters presented in Chang et al. (2017) and Zhou et al. (2014), which are interleaved boost converters with switched capacitors. According to the results, higher efficiency can be obtained with the converter proposed in this study. Based on the analysis, the simulation results, and the sample converter, the proposed converter can be employed in highly boosting applications with an average power level. Since the planar inductors are employed instead of the coupled inductors in the proposed converter, a superior power density can be attained.

References

Chang C, Cheng H, Chang E (2017) Using the buck-interleaved buck–boost converter to implement a step-up/down inverter. Eng Comput 34(2):272–284

Chen Y, Lin W (2015) An interleaved high step-up DC–DC converter double boost paths. Int J Circuit Theory Appl 43:967–983

Chen S, Yang S, Hwang C (2018) Interleaved high step-up DC-DC converter based on voltage multiplier cell and voltage-stacking techniques for renewable energy applications. Energies 11(1632):1–8

Figueres E, Garcera G, Sandia J, Gonzalez-Espin F, Rubio J (2009) Sensitivity study of the dynamics of three-phase photovoltaic inverters with an LCL grid filter. IEEE Trans Ind Electron 56(3):706–717

Franceschini G, Lorenzani E, Cavatorta M, Bellini A (2008) A boost: a high-power three-phase step-up full-bridge converter for automotive applications. IEEE Trans Ind Electron 55(1):173–183

Ganesan R, Prabhakar M (2014) Non-isolated high step-up interleaved boost converter. Int J Power Electron 6(3):288–296

Hwu K, Yau Y (2009) An interleaved ac–dc converter based on current tracking. IEEE Trans Ind Electron 56(5):1456–1463

Jemei S, Hissel D, Pera M, Kauffmann J (2008) A new modeling approach of embedded fuel-cell power generators based on artificial neural network. IEEE Trans Ind Electron 55(1):437–447

Liu X, Xhang X (2019) Interleaved high step-up converter with coupled inductor and voltage multiplier for renewable energy system. CPSS Trans Power Electron Appl 4(4):299–306

Lopez O, Teodorescu R, Doval-Gandoy J (2006) Multilevel transformerless topologies for single-phase grid-connected converters. In: Proceedings of IEEE IECON, pp 5191–5196

Salary E, Banaei M, Ajami A (2017) Design of novel step-up boost DC/DC converter. Iran J Sci Technol Trans Electr Eng 41:13–22

Scarpa V, Buso S, Spiazzi G (2009) Low-complexity MPPT technique exploiting the PV module MPP locus characterization. IEEE Trans Ind Electron 56(5):1531–1538

Shimizu T, Hashimoto O, Kimura G (2003) A novel high-performance utility-interactive photovoltaic inverter system. IEEE Trans Power Electron 18(2):704–711

Tang Y, Fu D (2015) Hybrid switched-inductor converters for high step-up conversion. IEEE Trans Ind Electron 12:324–330

Todorovic M, Palma L, Enjeti P (2008) Design of a wide input range dc–dc converter with a robust power control scheme suitable for fuel cell power conversion. IEEE Trans Ind Electron 55(3):1247–1255

Yang L, Liang T, Chen J (2009) Transformerless DC-DC converters with high step-up voltage gain. IEEE Trans Ind Electron 56(8):3144–3152

Zhou L, Zhu B-X, Luo Q-M, Chen S (2014) Interleaved non-isolated high step-up dc/dc converter based on the diode-capacitor multiplier. IET Power Electron 7(2):390–397

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

Rights and permissions

About this article

Cite this article

Vafa, M., Ershadi, M.H., Khodadadi, H. et al. An Interleaved High Step-Up DC–DC Converter with Low Voltage Stress. Iran J Sci Technol Trans Electr Eng 45, 573–584 (2021). https://doi.org/10.1007/s40998-020-00366-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40998-020-00366-w