Abstract

His paper presents a new tunable positive and negative active inductor simulator and positive and negative capacitance and resistance multiplier. The proposed designs use only one second-generation voltage-mode conveyor (VCII+), one OTA and two passive elements. Applications to the proposed designs in the design of different types of filters are also presented. The functionality of the designs is confirmed using simulation and experimentally.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Active inductors simulator and impedance scaling circuits play essential role in many applications. This include but not limited to active filters, oscillators, phase shifters, etc. [1,2,3]. Simulated inductors offers some advantages such as integration, low area, and high quality factor. There are many designs available in the literature. The recent design in [1] used a single second-generation voltage-mode conveyor and three passive components. The drawback of this design is that it requires two identical resistors to obtain a lossless active inductor and not suitable for very low frequency applications. The design in [2] is complex because it uses three CFOA and four passive elements. In [3], a CFOA based design is used with three passive elements and the capacitor is floating which is not preferable. The drawback of this design is that it is lossy inductor.Other applications, required impedance multiplier to scale up a capacitance or resistance for very low frequency applications such as filters for biomedical systems where large capacitance or resistance are needed [4]. There are many designs in the open literature. The design in [5] used three OTAs to design a capacitance multiplier. In [6], a MOSFET-based impedance multiplier is presented. The drawback of this design is that it is not tunable. A three current-controlled current amplifier approach is presented in [7]. The design is limited to capacitance and resistance multiplier. The design in [8] used current mirror aspect ratio for capacitance multiplier and hence no tunability. A universal immittance simulator is presented in [9] where three CCIIs are used with three to four passive elements. A current-Conveyor based approach for R and C multiplier only is presented in [10]. The design in [11] uses three OTAs and two equal values capacitors to implement capacitance multiplier only. In [12], a differential amplifier-based capacitance multiplier only is presented. The design in [13] is a capacitance multiplier only. References [14, 15] present current mirror-based capacitance multipliers in which the tunability is not possible. The design in [16] used CCII and OTA to implement capacitor and resistor multiplier only. In [17], a grounded inductor simulator is presented. The design used two CFOA and four passive elements. The design in [18] used VCII to implement capacitance multiplier only and it uses floating capacitor. In [19], one INIC and one IVIC and three passive elements were used to simulate grounded active inductor. The design in [20], used two inverting buffers and one CCII and three passive element one of them is a floating capacitor to simulate grounded inductor. A modified MD VCC and three passive element were used to implement a lossy active inductor is presented in [21].

This paper presents a novel, tunable positive and negative active inductor simulator and positive and negative capacitance and resistance multiplier. The rest of the paper is organized as a follows: The proposed design is presented in Sect. 2. Simulation and experimental results are presented in Sect. 3. The paper conclusion is presented in Sect. 4.

2 Proposed Design

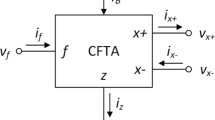

The proposed design is shown in Fig. 1. It consists of a second-generation voltage-mode conveyor (VCII+), operational transconductance amplifier (OTA) and only two passive components.

The relationship between voltage and currents terminals of VCII are represented as:

where \(\beta\) and \(\alpha\) are current gain.

The terminal characteristic of the VCII are: high impedance at X node and low impedance at Y and Z nodes (Fig. 2).

with reference to Fig. 1, the input impedance is given by:

But, \(i_{y} = V_{s} /Z_{1}\), then the input impedance is written as:

where, \(g_{m} = { }20 \times I_{{\text{B}}}\) is the OTA transconductance and \(I_{{\text{B}}}\) is the OTA bias current.

From Eq. (4), the circuit can be used to implement a tunable grounded active inductor and capacitance multiplier as follows:

-

1.

Active inductor simulator

If \(Z_{1} = R_{1}\), and \(Z_{2} = \frac{1}{{sC_{2} }}\), the input impedance is given by:

where \(L = C_{2} \frac{{R_{1} }}{{20 \times I_{{\text{B}}} }}\) Eq. (5) implements a tunable inductor and the value of the inductance is controlled using \(R_{1}\) and \(I_{{\text{B}}}\).

-

2.

Capacitance multiplier

If \(Z_{1} = \frac{1}{{sC_{1} }}\) and \(Z_{2} = R_{2}\), then the input impedance is given by:

The original capacitance is multiplied by (\(1 + 20 \times R_{2} I_{{\text{B}}}\)) and can be tuned using \(R_{2}\) and \(I_{{\text{B}}}\). The modified circuit in Fig. 1 is shown in Fig. 3 and used to implement a tunable positive and negative resistance multiplier, negative active inductor simulator and negative capacitance multiplier as follows:

With reference to Fig. 3, the input impedance Zin is given by:

-

3.

Resistance multiplier

From (7), if Z2gm < 1, then Z1 will be scaled up.

If Z1 = R1 (the resistance to be scaled up), Z2 = R2, then the input impedance is given by:

And \(0 \le 20 \times R_{2} I_{{\text{B}}} < 1\).

-

4.

Negative resistance

From Eq. 7, if \(Z_{2} g_{m} > 1\), then a negative tunable resistance multiplier is obtained:

If \(Z_{1} = R_{1}\) (the resistance to be scaled up),\(Z_{2} = R_{2}\), then the input impedance is given by:

-

5.

Negative active inductor simulator

If \(Z_{1} = R_{1}\) and, \(Z_{2} = \frac{1}{{sC_{2} }}\), \(Z_{2} g_{m} > 1\), then a negative active inductor is obtained and is given by:

-

6.

Negative capacitance multiplier

If \(Z_{1} = \frac{1}{{sC_{1} }}\), and \(Z_{2} = R_{2} , Z_{2} g_{m} > 1,\) then the input impedance is given by:

3 Simulation and Experimental Results

3.1 Simulation Results

To confirm the functionality of the proposed designs, the active inductor and the capacitor multiplier are used in the design of high pass, low pass filters, respectively. The resistance multiplier is used in the design of high pass filter as shown in Fig. 4. Multisim professional is used where AD844 is configured as VCII + and LM13700 (OTA). The circuit is powered with VCC = − VSS = 5 V.

-

a.

Active inductor

For the active inductor, the high pass filter circuits shown in Fig. 4a is simulated with \(R\) = 1 kΩ and the active impedance parameters are \(R_{1}\) = 10 kΩ, C2 = 1 nF. The OTA bias current was varied from 0.2 to 2 mA. The inductance will vary from 0.5mH to 5 m. Plots of the frequency response of the filter are shown in Fig. 5. It is evident from the plot that the active inductor is functioning properly.

The transient analysis was carried out using 300 kHz input signal with 1 V amplitude and a bias current of 1 mA. The simulation results shown in Fig. 6 confirm that the active inductor is working properly.

The active inductor will work properly in the range of 100 Hz to 1 MHz as shown in Fig. 7. The frequency range can be changed by varying the value of the capacitance used.

-

b.

Capacitance multiplier

To test the functionality of the proposed capacitance multiplier, the proposed C-multiplier is used in the design of an RC low pass filter with \(R\) = 1 kΩ, \(R_{1}\) = 10 kΩ and C = 1 nF. The bias current of the OTA is varied from 0.2 to 2 mA. Plots of the frequency response of the filter are shown in Fig. 8. It is evident from the plots that the filter is working properly with tunable − 3 dB frequency.

The transient analysis for the low pass filter is carried out using the same components. The simulation results shown in Fig. 9 indicates that the circuit is working properly.

-

c.

Resistance multiplier

The proposed resistance multiplier is used in the design of an RC high pass filter. In this design, \(Z_{1}\) = \(R_{1}\) = 100 Ω, is the resistor to be scaled up and Z2 = R2 = 100 Ω and \(I_{{\text{B}}}\) can be varied such that the denominator is not zero. The frequency response shown in Fig. 10 confirms the functionality of the design.

3.2 Experimental Results

To verify the functionality of the proposed design experimentally, the proposed active inductor is used in the design of a tunable high pass filter with \(R\) = 1 kΩ and the active impedance parameters \(R_{1}\) = 10 kΩ and C2 = 1 nF(measured 1.2 nF). Plots of the transient response for different bias currents using 15 mV signal at the − 3 dB frequency are shown in Fig. 11.

It is clear from the plots that the active inductor is working properly.

The high pass filter circuit using AI was simulated for THD using different bias current and (\(I_{{\text{B}}}\) = 0.2 mA, 1 mA, and 2 mA). The THD is, respectively, 0.484%, 0.019%, and 0.005%) which is within the acceptable range.

The frequency response is also carried out for the bias current of 0.2mA. Plots of the frequency response are shown in Fig. 12. It is cleSar that the experimental results are in a good agreement with theory with small deviation as expected due to parasitic.

Comparison of the proposed AIS design with previous art is summarize in Table 1. It is clear from the table that the proposed design is better in terms of tunability, the number of functions, the number of passive components and the frequency range.

4 Conclusion

A new compact and tunable positive and negative active inductor simulator and impedance multiplier circuits are developed. The design is novel as it implement positive and negative inductor and simulate positive and negative capacitance and resistance multiplier. The functionality of the designs were confirmed using and simulation and experimental test using the commercially available ICs. The developed designs can be used as core bock in many analog signal-processing applications.

References

Yuce, E.: A new simulated inductor with reduced series resistors using a single VCII+. Electronics 10, 1–15 (2021)

Yuce, E.; Minaei, S.: On the realization of simulated inductors with reduced parasitic impedance effects. Circuits Syst. Signal Process 28, 451–465 (2009)

Youci, E.: Novel lossless and lossy grounded inductor simulators consisting of a canonical number of components. Analog Integr. Circ. Sig. Process 59, 77–82 (2009)

Padilla- Cantoya, I.; Rizo-Dominguez, L.; Mlinar-Solis, J.: Capacitance multiplier with large multiplication factor high accuracy and low power and silicon area for floating applications. IEICE Electron. Express (2018).

Ahmed, M.T.; Khan, I.A.; Minhah, N.: Novel electronically tunable C-multiplier. Electron. Lett. 31(1), 9–11 (1995)

Silva Martinez, J.; Vazquez-Gonzalez, A.: Impedance scalers for IC active filters. IEEE international symposium on circuits and systems, pp.51–154 (1998)

Abuelma’Atti, M.T.; Tasadduq, N.A.: Electronically tunable capacitance multiplier and frequency-dependent negative resistance simulator using the current-controlled current conveyor. Microelectron. J. 30(9), 869–873 (1999)

Solis-Bustos, S.; Silva, H.; Sanches, E.: A 60-dB dynamic-range CMOS sixth-order 2.4-Hz low-pass filter for medical applications. IEEE Trans. Circuits Syst. Analog Digit. Signal Process. 47(12), 1391–1398 (2000)

Cicekoglu, O.; Toker, A.; Kuntman, H.: Universal immitance function simulators using current conveyors. Comput. Electr. Eng. 27(3), 227–238 (2001)

Khan, A.; Bimal, S.; Dey, K.; Roy, S.: Current conveyor based R- and C-multiplier circuits. Int. J. Electron. Commun. 56(5), 312–316 (2002)

Kulej, T.: Regulated capacitance multiplier in CMOS technology. In: International conference on mixed design of integrated circuits and systems, pp. 316–319 (2009)

Padilla, I.; Furth, P.: Enhanced grounded capacitor multiplier and its floating implementation for analog filter. IEEE Trans. Circuits Syst. II Express Briefs 62(10), 962–966 (2015)

Al-Absi, M.; Al-Suhaibani, E.; Abuelma’Atti, M.: A new controllable CMOS impedance scaler. In: International multi-conference on systems, signals & devices, vol. 21-24, pp. 695-698. Leipzig (2016)

Germanovix, W.; Bonizzoni, E.; Maloberti, F.: Capacitance super multiplier for sub-Hertz low-pass integrated filters. IEEE Trans. Circuits Syst II Express Briefs 65(3), 301305 (2018)

Solís-Bustos, S.; Silva-Martínez, J.; Maloberti, F.; Sánchez-Sinencio, E.: A 60-dB dynamic-range CMOS sixth-order 2.4-Hz low-pass filter for medical applications. IEEE Trans. Circuits Syst. II Analog Dig. Signal Process. 47(12), 1391–1398 (2000)

Al-Absi, M.A.; Taher Abuelmaatti, M.: A novel tunable grounded positive and negative impedance multiplier. IEEE Trans. Circuits Syst. II Express Briefs 66(6), 924–927 (2019)

Yuce, E.; Minaei, S.: Commercially available active device based grounded inductor simulator and universal filter with improved low frequency performances. J. Circuits Syst. Comput. 26(04), 1750052 (2017)

Stornelli, V.; Safari, L.; Barile, G.; Ferri, G.: A new extremely low power temperature insensitive electronically tunable VCII-based grounded capacitance multiplier. IEEE Trans. Circuits Syst. II Express Briefs 68, 72–76 (2021)

Yuce, E.; Alpaslan, H.; Minaei, S.; Ayten, U.E.: A new simulated grounded inductor based on two NICs, two resistors and a grounded capacitor. Circuits Syst. Signal Process 40, 5847–5863 (2021)

Yesil, A.; Yuce, E.; Minaei, S.: Inverting voltage buffer based lossless grounded inductor simulators. AEU Int. J. Electron. Commun. 83, 131–137 (2018)

Abaci, A.; Yuce, E.: Modified DVCC based quadrature oscillator and lossless grounded inductor simulator using grounded capacitor(s). AEU Int. J. Electron. Commun. 76, 86–96 (2017)

Acknowledgements

The authors acknowledge the support of King Fahd university of Petroleum & minerals.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Al-Absi, M.A., Al-Khulaifi, A. A Novel Tunable Grounded Positive and Negative Active Inductor Simulator and Impedance Multiplier. Arab J Sci Eng 47, 14983–14988 (2022). https://doi.org/10.1007/s13369-022-07338-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-022-07338-8