Abstract

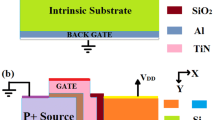

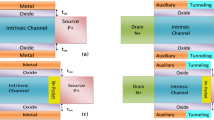

This paper extensively sheds light on the performance of an Asymmetrical-gate Tunnel FET (A-TFET) under cryogenic temperatures (< 78 K) in terms of DC, Analog, and RF metrics. SILVACO ATLAS TCAD is implemented to invoke the device physics and subsequently characterize the lattice temperature parameters for facilitating the carrier transport in terms of device transfer characteristics, ION/IOFF ratio, subthreshold swing (SS). Steep profiles for ION/IOFF ratio and SS are observed at cryogenic temperatures representing superior device performance. Furthermore, the transconductance (gm) and transconductance generation factor (TGF) profiles are thoroughly investigated as a part of analog analysis while RF metrics like the transistor parasitic capacitances and cut-off frequency are investigated as well. The real-time fabrication complexity in terms of presence of interface traps for a damaged device has been compared with a fresh device with absence of interface traps in terms of transfer characteristics and gm at cryogenic and ambient temperatures thereby ensuring the CMOS compatibility of the A-TFET for quantum computing.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Data Availability

No datasets were generated or analysed during the current study.

References

Avci UE, Rios R, Kuhn K, Young IA (2011) Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic. In 2011 Symposium on VLSI Technology-Digest of Technical Papers. IEEE, Kyoto, pp 124–125

Reddy NN, Panda DK (2021) A comprehensive review on tunnel field-effect transistor (TFET) based biosensors: recent advances and future prospects on device structure and sensitivity. SILICON 13(9):3085–3100

Narang R, Saxena M, Gupta RS, Gupta M (2012) Assessment of ambipolar behavior of a tunnel FET and influence of structural modifications. Journal of Semiconductor Technology and Science 12(4):482–491

Alper C, De Michielis L, Dağtekin N, Lattanzio L, Bouvet D, Ionescu AM (2013) Tunnel FET with non-uniform gate capacitance for improved device and circuit level performance. Solid-State Electron 84:205–210

Appenzeller J, Lin YM, Knoch J, Chen Z, Avouris P (2005) Comparing carbon nanotube transistors-the ideal choice: a novel tunneling device design. IEEE Trans Electron Devices 52(12):2568–2576

Der Agopian PG, Martino JA, Vandooren A, Rooyackers R, Simoen E, Thean A, Claeys C (2017) Study of line-TFET analog performance comparing with other TFET and MOSFET architectures. Solid-State Electron 128:43–47

Sahoo S, Dash S, Routray SR, Mishra GP (2021) Z-shaped gate TFET with horizontal pocket for improvement of electrostatic behavior. Int J Numer Model Electron Networks Devices Fields 34(1):e2808

Yan Z, Li C, Guo J, Zhuang Y (2019) A GaAs0. 5Sb0. 5/In0. 53Ga0. 47As heterojunction Z-gate TFET with hetero-gate-dielectric. Superlattices Microstruct 129:282–293

Kavangary A, Graf P, Azazoglu H, Flebbe M, Huba K, Nienhaus H, Möller R (2019) Temperature dependent electrical characteristics of a junction field effect transistor for cryogenic sub-attoampere charge detection. AIP Advances 9(2):025104

Tracy LA, Luhman DR, Carr SM, Bishop NC, Ten Eyck GA, Pluym T, Carroll MS (2016) Single shot spin readout using a cryogenic high-electron-mobility transistor amplifier at sub-Kelvin temperatures. Appl Phys Lett 108(6):063101

Ekanayake SR, Lehmann T, Dzurak AS, Clark RG, Brawley A (2010) Characterization of SOS-CMOS FETs at low temperatures for the design of integrated circuits for quantum bit control and readout. IEEE Trans Electron Devices 57(2):539–547

Degenhardt C, Geck L, Kruth A, Vliex P, van Waasen S (2017) CMOS based scalable cryogenic control electronics for qubits. In 2017 IEEE International Conference on Rebooting Computing (ICRC). IEEE, Washington, DC, pp 1–4. https://doi.org/10.1109/ICRC.2017.8123682

Veldhorst M, Eenink HGJ, Yang CH, Dzurak AS (2017) Silicon CMOS architecture for a spin-based quantum computer. Nat Commun 8(1):1766

Karmakar A, Ghosh R, Saha P (2022) Investigating the linearity behavior of dual gate junction less MOSFET with high-K gate stack at cryogenic Temperatures. In 2022 IEEE International Conference of Electron Devices Society Kolkata Chapter (EDKCON) IEEE, Kolkata, pp 576–579. https://doi.org/10.1109/EDKCON56221.2022.10032911

Madadi D (2022) Investigation of junctionless fin-FET characterization in deep cryogenic temperature: DC and RF analysis. IEEE Access 10:130293–130301

Manual AU (2000) Silvaco International. Santa Clara, CA 95054:23

Ghosh R, Sarkhel S, Saha P (2023) Design and analysis of Z shaped InGa0. 5As0. 5/Si tunnel FET using non-equilibrium Green’s function model for hydrogen gas sensing application. Micro and Nanostructures 182:207651

Chander S, Sinha SK (2022) Effect of Raised Buried Oxide on Characteristics of Tunnel Field Effect Transistor. SILICON 14(14):8805–8813

Ghosh R, Nelapati RP (2024) Impact of Deep Cryogenic Temperatures on High-k Stacked Dual Gate Junctionless MOSFET Performance: Analog and RF analysis. SILICON 16(2):615–623

Sinha SK, Chander S, Chaudhary R (2022) Investigation of noise characteristics in gate-source overlap tunnel field-effect transistor. SILICON 14(16):10661–10668

Chander S, Sinha SK (2023) Performance Analysis of Electrical Characteristics Hetero-junction LTFET at Different Temperatures for IoT Applications. Nanoelectronics Devices: Design, Materials, and Applications (Part I) 250(2.12):105

Ghosh R (2023) Performance investigation of dual trench split-control-gate MOSFET as hydrogen gas sensor: A catalytic metal gate approach. IEEE Sens Lett 7(5):1–4.

Wang PF, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Hansch W (2004) Complementary tunneling transistor for low power application. Solid-State Electronics 48(12):2281–2286

Beckers A, Jazaeri F, Enz C (2019) Theoretical limit of low temperature subthreshold swing in field-effect transistors. IEEE Electron Device Lett 41(2):276–279

Chander S, Sinha SK, Chaudhury R, Singh A (2021) Ge-Source Based L-shaped Tunnel Field Effect Transistor for Low Power Switching Application. Springer, Silicon 14:7435–7448

Anam A, Amin SI, Prasad D, Kumar N, Anand S (2023) Charge-plasma-based inverted T-shaped source-metal dual-line tunneling FET with improved performance at 0.5 V operation. Physica Scripta 98(9):095918

Shreya S, Kumar N, Anand S, Amin I (2020) Performance analysis of a charge plasma junctionless nanotube tunnel FET including the negative capacitance effect. J Electron Mater 49(4):2349–2357

Singh A, Kumar N, Amin SI, Anand S (2020) Implementation of negative capacitance over SiGe sourced Doping-less Tunnel FET. Superlattices Microstruct 145:106580

Madadi D, Orouji AA (2020) New high-voltage and high-speed β-Ga2O3 MESFET with amended electric field distribution by an insulator layer. The European Physical Journal Plus 135(7):1–12

Sen D, De A, Goswami B, Shee S, Sarkar SK (2021) Noise immune dielectric modulated dual trench transparent gate engineered MOSFET as a label free biosensor: proposal and investigation. J Comput Electron 20:2594–2603

Beckers A, Jazaeri F, Grill A, Narasimhamoorthy S, Parvais B, Enz C (2020) Physical model of low-temperature to cryogenic threshold voltage in MOSFETs. IEEE Journal of the Electron Devices Society 8:780–788

Ghosh R, Nelapati RP (2023) Design and investigation of InAs source dual metal stacked gate-oxide heterostructure tunnel FET based label-free biosensor. Micro and Nanostructures 174:207444

Talukdar J, Rawat G, Singh K, Mummaneni K (2021) Low frequency noise analysis of single gate extended source tunnel FET. SILICON 13:3971–3980

Rout SP, Dutta P (2020) Impact of high mobility III-V compound material of a short channel thin-film SiGe double gate junctionless MOSFET as a source. Engineering Reports 2(1):e12086

Chakraborty W, Ni K, Smith J, Raychowdhury A, Datta S (2019) An empirically validated virtual source FET model for deeply scaled cool CMOS. In 2019 IEEE International Electron Devices Meeting (IEDM). IEEE, pp 39–4. https://doi.org/10.1109/IEDM19573.2019.8993666

Chiang HL, Chen TC, Wang JF, Mukhopadhyay S, Lee WK, Chen CL, Cai J (2020) Cold CMOS as a power-performance-reliability booster for advanced FinFETs. In 2020 IEEE Symposium on VLSI Technology. IEEE, Honolulu, pp 1–2. https://doi.org/10.1109/VLSITechnology18217.2020.9265065

Beckers A, Jazaeri F, Ruffino A, Bruschini C, Baschirotto A, Enz C (2017) Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing. In 2017 47th European Solid-State Device Research Conference (ESSDERC). IEEE, Leuven, pp 62–65. https://doi.org/10.1109/ESSDERC.2017.8066592

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Sinjini Misra: Formal analysis, methodology, software, validation. Chandreyee Bose: Methodology, software, validation. Rittik Ghosh: Conceptualization, formal analysis, interpretation of results and writing the original draft. Priyanka Saha: Conceptualization, interpretation of results, review, editing, and supervision. All authors reviewed the results and approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Ethics Approval

The authors of this paper announce that they have no known competing financial interests or personal associations that may have influenced the work presented in this document. The authors also confirm that this manuscript has not been published elsewhere and is not under consideration by another journal. All the authors have approved the manuscript and agree with its submission to Silicon journal.

Consent to Participate

The authors of this paper voluntarily agree to contribute in this work.

Consent for Publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Misra, S., Bose, C., Ghosh, R. et al. Investigation of Analog/RF behaviour of Asymmetrical Gate Tunnel FET at Cryogenic temperatures. Silicon 16, 4753–4762 (2024). https://doi.org/10.1007/s12633-024-03049-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-024-03049-x