Abstract

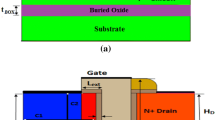

In this proposed work, a novel single gate F-shaped channel tunnel field effect transistor (SG-FC-TFET) is proposed and investigated. The impact of thickness of the source region and lateral tunneling length between the gate oxide and edge of the source region on analog and radio frequency parameters are investigated with appropriate source and drain lateral length through the 2D-TCAD tool. The slender shape of the source enhanced the electric field crowding effect at the corners of the source region which reflect in terms of high ON-current (Ion). The Ion of the proposed device is increased up to 10− 4 A/μm with reduced sub-threshold swing (SS) is 7.3 mV/decade and minimum turn-ON voltage (Von = 0.28 V). The analog/RF parameters of SG-FC-TFET are optimized.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Availability of Data and Material

All relevant data has been included in manuscript.

References

Villalon A, Le Carval G, Martinie S, Le Royer C, Jaud M-A, Cristoloveanu S (2014) Further insights in TFET operation. IEEE Trans Electron Dev 61(8):2893–2898. https://doi.org/10.1109/TED.2014.2325600

Jhaveri R, Nagavarapu V, Woo JCS (2009) Asymmetric Schottky tunneling source SOI MOSFET design for mixed-mode applications. IEEE Trans Electron Dev 56(1):93–99. https://doi.org/10.1109/TED.2008.2008161

Kale S, Kondekar PN (2016) Ferroelectric Schottky barrier tunnel FET with gate-drain underlap: Proposal and investigation. Superlattice Microst 89:225–230. https://doi.org/10.1016/j.spmi.2015.11.019

Bagga N, Kumar A, Dasgupta S (2017) Demonstration of a novel two source region tunnel FET. IEEE Trans Electron Dev 64(12):5256–5262. https://doi.org/10.1109/TED.2017.2759898

Kale S, Chandu MS (2021) Dual metal gate dielectric engineered dopant segregated Schottky barrier Mosfet with reduction in Ambipolar current. Silicon. https://doi.org/10.1007/s12633-020-00921-4

Nagavarapu V, Jhaveri R, Woo JCS (2008) The tunnel source (PNPN) n-MOSFET: A novel high performance transistor. IEEE Trans Electron Dev 55(4):1013–1019. https://doi.org/10.1109/TED.2008.916711

Latha NKH, Kale S (2020) Dielectric modulated Schottky barrier TFET for the application as label-free biosensor. Silicon 12:2673–2679. https://doi.org/10.1007/s12633-019-00363-7

Kim SW, Kim JH, Liu Tsu-Jae K., Choi WY, Park Byung-Gook (2016) Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans Electron Dev 63(4):1774–1778. https://doi.org/10.1109/TED.2015.2472496

Yang Z (2016) Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Dev Lett 37 (7):839–842. https://doi.org/10.1109/LED.2016.2574821

Seunghyun Y, Oh J, Kang S, Kim Y, Kim JH, Kim G, Kim S (2019) F-shaped tunnel field-effect transistor (TFET) for the low-power application. Micromachines 10(11):760–761. https://doi.org/10.3390/mi10110760

Ahmed W, Ahmed E (1993) Ion implantation and in situ doping of silicon. Mater Chem Phys 37(3):289–294. https://doi.org/10.1016/0254-0584(94)90166-X

Gedam A, Acharya B, Mishra GP (2021) An analysis of interface trap charges to improve the reliability of a charge-plasma-based nanotube tunnel FET. J Comput Electron 1–12. https://doi.org/10.1007/s10825-021-01696-6

Zhang M, Guo Y, Zhang J, Yao J, Chen J (2020) Simulation study of the double-gate tunnel field-effect transistor with step channel thickness. Nanoscale Res Lett 15(1):1–9. https://doi.org/10.1186/s11671-020-03360-7

Kim JH, Kim SW, Kim HW, Park B-G (April 2015) Vertical type double gate tunnelling FETs with thin tunnel barrier. Electron Lett 51(9):718–720. https://doi.org/10.1049/el.2014.3864

Morita Y, Takahiro M, Shinji M, Wataru M, Akihito T, Koichi F, Takashi M (2014) Performance enhancement of tunnel field-effect transistors by synthetic electric field effect. IEEE Electron Dev Lett 35(7):792–794. https://doi.org/10.1109/LED.2014.2323337

Yeqing L, Zhou G, Li R, Liu Q, Zhang Q, Vasen T, Chae SD, Kosel T, Wistey M (2012) Performance of AlGaSb/InAs TFETs with gate electric field and tunneling direction aligned. IEEE Electron Dev Lett 33(5):655–657. https://doi.org/10.1109/LED.2012.2186554

Shivendra Y, Madhukar R, Sharma D, Aslam M, Soni D, Sharma N (2018) A new structure of electrically doped TFET for improving electronic characteristics. Appl Phys A 124(7):1–9. https://doi.org/10.1007/s00339-018-1930-9

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98(12):2095–2110. https://doi.org/10.1109/JPROC.2010.2070470

Yadav DS, Sharma D, Raad BR, Bajaj V (2016) Impactful study of dual work function, underlap and hetero gate dielectric on TFET with different drain doping profile for high frequency performance estimation and optimization. Superlattices Microstruct 96:36–46. https://doi.org/10.1016/j.spmi.2016.04.027

Yadav DS, Raad BR, Sharma D (2016) A novel gate and drain engineered charge plasma tunnel field-effect transistor for low sub-threshold swing and ambipolar nature. Superlattices Microstruct 100:266–273. https://doi.org/10.1016/j.spmi.2016.09.029

Sedighi B, Hu XS, Liu H, Nahas JJ, Niemier M (2015) Analog circuit design using tunnel-FETs. IEEE Trans Circuits Syst I Regul Papers 62(1):39–48. https://doi.org/10.1109/TCSI.2014.2342371

Acknowledgments

The authors would like to thank Dr. Dip Prakash Samajdar from Department of Electronics and Communication Engineering, PDPM Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, Madhya Pradesh, India for providing valuable suggestions and support to carry out this research work.

Author information

Authors and Affiliations

Contributions

– Prabhat Singh: Conceptualization, data curation, formal analysis, methodology, investigation, writing – original draft.

– Dharmendra Singh Yadav: Supervision, validation, visualization, writing – review & editing

Corresponding author

Ethics declarations

The manuscript follows all the ethical standards, including plagiarism.

Consent to Participate

We are giving consent to participate.

Consent for Publication

We are giving consent to publish.

Conflict of Interests

No conflicts of interest

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, P., Yadav, D.S. Impactful Study of F-shaped Tunnel FET. Silicon 14, 5359–5365 (2022). https://doi.org/10.1007/s12633-021-01319-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01319-6