Abstract

This article presents a study on the subthreshold swing (SS) and the ON–OFF current ratio of a negative capacitance source pocket double-gate tunnel field-effect transistor (NC-SP-DGTFET). In this analysis, a novel device is developed that integrates gate and channel engineering techniques. The combination of the ferroelectric material hafnium zirconium oxide (HZO) with the dielectric material SiO2 generates a negative capacitance (NC) effect. Additionally, the incorporation of a totally depleted source pocket into the DGTFET reduces the tunneling width. The addition of NC has the potential to improve the SS through the amplification of the electric field at the tunnel junction. Moreover, it has been observed that a fully depleted source pocket within the source/channel region significantly enhances the ION current when compared to the double-gate tunnel field-effect transistor (DGTFET). Following thorough device optimization, there has been a notable enhancement in the ION/IOFF current ratio, SS, and transconductance (gm) by a factor of 1.54 × 1013, 20.8 mV/dec, and 5.102 × 10−4 S/µm, respectively. These improvements signify superior energy efficiency and enhanced performance when compared to both DGTFET and source pocket based DGTFET (SP-DGTFET) configurations. Furthermore, substantial research has been conducted on the variation in electrical properties in relation to the thickness of ferroelectric materials. The findings indicate that the proposed device exhibits considerable potential as a viable option for applications requiring both low power consumption and high operational speed.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

The scaling of metal–oxide–semiconductor field-effect transistor (MOSFET) devices has been driven by the growing demand for smaller and more efficient integrated circuits (ICs) due to advancements in technology.1 The enhancement of switching speed and MOSFET density in an IC leads to a diminution in device performance as a result of short-channel effects (SCEs).2,3,4 These SCEs include drain-induced barrier lowering (DIBL), threshold voltage roll-off, subthreshold leakage current, subthreshold swing (SS), punch through, and hot carrier effect. The tunnel field-effect transistor (TFET) is emerging as a highly promising and energy-efficient alternative to conventional MOSFETs for low-power applications.5,6,7 The band-to-band tunneling (BTBT) mechanism8 has become increasingly popular because of its advantageous characteristics, including minimal OFF-state leakage current, an SS value of less than 60 mV/decade at ambient temperature,9 and reduced SCEs. Nevertheless, it is important to acknowledge that there are several limits associated with TFET design. One of the primary challenges faced by TFET designers is the relatively low on-state current. Furthermore, it has been observed that TFETs exhibit ambipolar behavior.10 By incorporating the tunneling width and barrier engineering techniques, the ON current can be increased in TFETs. Barrier height may decrease by using III–V material compounds, whereas barrier width can increase by integrating pocket doping engineering in multi-gate TFET structures. The double-gate structure is highly effective in mitigating SCEs due to its superior gate control and drain current characteristics. To enhance the ON-state current of the device, it is necessary to introduce a pocket at the source/channel junction.11 Simultaneously, it should be noted that the asymmetry of the device suppresses ambipolar conduction, which distinguishes it from conventional TFET architectures.12 Further, to enhance the device characteristics a ferroelectric (FE) layer13 is added to the TFET structure. The FE layer has shown an internal voltage amplification with steeper subthreshold characteristics and improved ION/IOFF ratio without necessitating any alterations to the fundamental physics of the transistor.14 The study conducted by Guha et al.15 examined a TFET including a heterojunction negative capacitance. It was observed that the utilization of this technology was feasible in inverters, ring oscillators, and entire adder circuits, with an SS of 27 mV/dec. Singh et al.16 introduced a source overlapped negative capacitance tunnel field-effect transistor (NCTFET). The SS was measured to be 34.7 mV/dec, while the ON current was determined to be 1.45 µA/µm. In their study, Kim and Kwon17 conducted an analysis on an NCTFET with channel engineering where the tunneling direction is normal to the gate. By refining the doping concentration in the channel the SS is improved by 43.9 mV/decade and the ON current is increased by 3.5 times as compared with that of the conventional TFET. The utilization of an FE layer represents a feasible alternative for enhancing the device’s characteristics, resulting in improved performance characterized by reduced power consumption and enhanced switching speed. In order to enhance the drain current and SS of TFETs,18 an FE insulator layer is integrated within the gate stack. In this particular scenario, the TFETs hold the negative capacitance (NC) property exhibited by FE materials in order to enhance the ON current.19 Consequently, the width of tunneling will decrease as a result of the amplified band bending, and a narrower tunneling width leads to an increased probability of tunneling with higher ON current. The studies published in the literature have looked at the gate-length-dependent SCEs of the double-gate tunnel field-effect transistor (DGTFETs) with different channel engineering techniques.20,21 However, to the best of our knowledge, there is no existing literature on DGTFETs utilizing the NC as a gate stack along with the source pocket (SP) as a channel engineering technique. The remaining part of this paper is organized as follows: The proposed device parameters, along with the simulation models, are described in the “Device Simulation Setup and Models” section. The results and discussions are discussed in the “Results and Discussion” section, and the conclusions are drawn in the final section.

Device Simulation Setup and Models

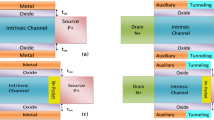

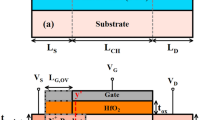

Figure 1 depicts a schematic illustration of an NC-SP-DGTFET. The source and drain are asymmetrically doped with doping concentrations of 1 × 1020 cm−3 and 1 × 1018 cm−3, respectively. The proposed device has a silicon channel with a length of 25 nm and it is doped with acceptor concentration of 1 × 1015 cm−3. The thickness of the gate oxide (TOX) is 1 nm, while the active silicon body (TSi) has a thickness of 10 nm.22,23,24 The decrease in channel length has minimal impact on the tunneling current due to the dominant influence of the electric field and band configuration in the vicinity of the tunneling junction on the drain current. The optimization of the ION/IOFF ratio is achieved through the incorporation of a source-side n-type pocket layer with a high doping concentration of 1 × 1019 cm−3 and a pocket length (LP) of 3 nm.

The fabrication process for the proposed NC-SP-DGTFET closely resembles that of conventional double-gate MOSFETs,25 as illustrated in Fig. 2. Initially, precise mask patterning and selection of photoresist facilitate the creation of p-type source, n-type drain, and channel regions on a silicon wafer via ion-implantation. An n-type pocket at the source/channel junction is introduced through an in-situ doping process. Subsequently, a SiO2 layer is grown utilizing chemical vapor deposition (CVD), followed by the deposition of FE material via atomic layer deposition (ALD). Finally, appropriate gate metals are deposited to complete the fabrication process.

Numerical simulations were performed with the Sentaurus TCAD (technology computer-aided design) simulator26 using the nonlocal BTBT model to include tunneling of electrons from source to drain. Generation and recombination models were used to include the charge carrier effects, and Fermi–Dirac statistics and bandgap narrowing models were activated for highly doped source and drain regions. The TCAD simulation models were meticulously calibrated with experimental data, as demonstrated by Biswas et al.8 and shown in Fig. 3, where the BTBT model tunneling mass has been tuned as 0.037 × m0 and the tunneling constants are calculated as A = 2.84 × 1014 and B = 1.73 × 107. Notably, the simulation results closely align with the experimental findings, indicating a strong agreement between the two.

Calibration of simulation model with the reported data (Ref. 8).

Existence of Negative Capacitance in Proposed Device

The use of NC27 in the gate oxide stack of TFETs can enhance drain current and SS. The use of FE material in its NC mode leads to an increase in the surface potential and an enhancement of the electric field in TFETs. Negative capacitance may be seen when an FE capacitor is connected in series with a normal capacitor in metal–ferroelectric–insulator–semiconductor (MFIS) and metal–ferroelectric–metal–insulator–semiconductor (MFMIS) configurations. The MFMIS exhibits an increased leakage current under equivalent applied voltages, largely influenced by the presence of an internal electrode. This electrode leads to polarization screening and destabilizes the NC effect. Conversely, the absence of such an electrode in the MFIS structure reduces the leakage current, minimizes charge exchange between domains, mitigates polarization compensation, and consequently diminishes hysteresis behavior.28 However, in the MFIS configuration, the NC effect is observed across a broader range of electric field and polarization. This broader range facilitates the provision of differential bias amplification within the necessary bias range for achieving the desired transfer characteristics of conventional FETs. Additionally, the FE parameters utilized in this study are derived from MFIS capacitor characteristics, rather than the polarization-electric field (PE) loop of the metal-ferroelectric-metal (MFM) configuration. These extracted FE parameters are experimentally obtainable and suitable for MFIS NC-SP-DGTFET implementation.

Ferroelectric materials like barium titanate (BaTiO3) and lead zirconate titanate (PZT) have long been utilized for their NC effect. However, their compatibility issues with CMOS fabrication and limited scalability pose challenges.29,30 Recently, doped hafnium oxide (HfO2) has emerged as a promising alternative, boasting strong FE properties. Doped HfO2, especially Zr-doped HfO2 (HZO), offers significant advantages over traditional perovskites, such as excellent scalability and seamless integration with CMOS processes.31 Additionally, HZO requires low annealing temperatures, further enhancing its appeal for advanced electronic applications. When comparing with PZT, HZO exhibits, we see a more pronounced NC effect, resulting in a higher electrical potential for thinner FE layers. The MFIS32 structure exhibits a stable state in total energy when a gate bias is applied, resulting in negative curvature in the Landau energy of the FE. The analytical description of the polarization charge density and electric field in a FE film is provided by the Landau equation. The NC-SP-DGTFET is simulated by activating the Landau–Khalatnikov (LK model) model33 to represent the polarization behavior of the FE material, and the poisons equation are calculated. The device parameters used for the simulation are shown in Table I.

The electric field of an FE material is given by the LK equation (Eq. 1)

where α, β and γ are Landau parameters. According to the Landau–Khalatnikov equation, the relationship between FE polarization and electric field properties exhibits an area with an unstable negative slope (dP/dE < 0), as depicted in Fig. 4. This instability in FE materials can be mitigated in a heterogeneous system, such as a ferroelectric-dielectric (FE-DE) stack, where polarization suppression (P = 0) can be achieved by minimizing depolarization energy. To achieve this, the LK model is calibrated with the fabricated TIN/HZO/TIN capacitor34 as illustrated in Fig. 4. The parameters of HZO material α = −1.35 × 10−11 cm/F, β = 5.509 × 1020 cm5/FC2 and γ = 0 cm9/FC4 are extracted with corresponding coercive filed (EC) 1 MV/cm and remanent polarization (Pr) 11.1 C/cm2.

Calibration of LK model with the experimental data (Ref. 34).

Results and Discussion

Energy profiles of NC-SP-DGTFET, SP-DGTFET and DGTFET are shown in Fig. 5a and b for the OFF and ON states, respectively. It is noticed that at VGS = 0 V, the tunneling probability from the source’s valence band to the channel’s conduction band is virtually insignificant due to the greater tunneling barrier width at the source-channel junction. In the ON state (VGS = 1 V), the gate voltage lowers the channel’s conduction band below the source’s valence band, allowing electrons to tunnel from source to channel and record a BTBT current. The tunneling width of the NC-SP-DGTFET is very small compared to SP-DGTFET and DGTFET due to the presence of pocket and FE material as gate dielectric. In the ON state (i.e at VGS = 1 V) of the NC-SP-DGTFET, polarization gets induced in the FE material, which results in the reduction in gate capacitance value. This amplifies the voltage across the gate oxide, leading to an enhancement in the electric field of the channel region and promoting BTBT. Further, the amplification effectively reduces the tunneling barrier width, facilitating electron tunneling from the source to the channel. Additionally, integrating a n+ pocket near source/channel region reduces the energy barrier height, causes increase in carrier concentration and enhances tunneling probability, which leads to higher ON-state current and improved device performance.

A comparison of the surface potential of the NC-SP-DGTFET, SP-DGTFET, and DGTFET is shown in Fig. 6. The surface potential is increased for the proposed device as compared to the SP-DGTFET and DGTFET owing to the existence of the NC effect attributable to the FE material. The NC leads to an internal voltage amplification and an enhancement of the electric field in the proposed device.

In addition, a comparison of the electric fields produced by the three distinct devices, NC-SP-DGTFET, SP-DGTFET, and DGTFET, is shown in Fig. 7. The proposed structure has the largest spike at the channel/source contact, indicating the greatest amount of tunneling of carriers. It is possible that the NC material utilized as the gate stack in the proposed device is responsible for the largest spike. The total gate capacitance will be increased beyond its standard value by incorporating NC material in the gate stack, resulting in a lower gate voltage being needed to achieve the same surface potential. As a result, the proposed device has a greater electric field.

Figure 8 shows the BTBT rate for the proposed device as a function of channel location. The tunneling width has a significant impact on the BTBT rate. When compared to a DGTFET, SP-DGTFET, the tunneling width of the NC-SP-DGTFET is much smaller. As a result, the electrons will tunnel very rapidly from source valance band to channel conduction band, which increases the BTBT rate.

DC Analysis

Figure 9 shows a comparison of the IDS–VGS characteristics of the three different structures (NC-SP-DGTFET, SP-DGTFET, and DGTFET). The effect of NC caused by the FE material is supported by the fact that NC-SP-DGTFET generates lower OFF current than the other two configurations. When comparing the NC-SP-DGTFET to the other two designs, a considerable drop in Vth is shown, along with an improvement in ION because of the higher drain current caused by the voltage amplification due to NC effect in the FE material used as a gate stack. SS and ION/IOFF ratio are both significantly enhanced in the NC-SP-DGTFET, which significantly influences the device performance. As can be seen in Fig. 10, the NC-SP-DGTFET has an impressive ION/IOFF ratio of 1013 while maintaining an SS of 20.8 mV/decade, while DGTFET and SP-DGTFET have ION/IOFF ratio and SS values of 4.17 × 1010, 0.622 × 1011, 34 mV/dec and 35 mV/dec, respectively.

Impact of Ferroelectric Thickness on Proposed Device

A large quantity of polarized charge with the smallest feasible TFE is needed to increase the device’s ON current. Because of the NC effect, the device’s positive capacitance (baseline device capacitance, Cdevice > 0) becomes smaller by increasing the gate capacitance, which is the inverse of the FE’s differential capacitance (CFE).

CFE can be varied by adjusting the FE thickness (TFE) and it should be matched to Cdevice (|CFE| ≥ Cdevice) to ensure maximal capacitance enhancement. Thus, at optimal TFE, there is a rise in drain current because total gate capacitance (CT) is maximized. The IDS–VGS curve of the NC-SP-DGTFET is shown in Fig. 11, plotted against varying TFE. As TFE rises, the drain current for NC-SP-DGTFET does as well, and the resulting steepening of the SS can be seen.

When the TFE increases, NC effects come into play, causing the voltage of the underlying SP-DGTFET to surpass the applied gate voltage. Additionally, hysteresis occurs when the FE thickness exceeds a critical value. This critical thickness is the point at which the FE capacitance equals the total gate capacitance connected with the underlying SP-DGFET. Therefore, it’s advisable to maintain TFE below this critical value. As the thickness increases, the drain current abruptly transitions from the OFF state to the ON state due to improved capacitance matching. This is evident from Fig. 11, which shows that increasing TFE enhances the ON current. It has also been determined that the “4 nm” TFE, where the maximum drain current and steep slope of the device has been attained, is the optimal TFE.

For NC-SP-DGTFET, Fig. 12 plots the SS and ION/IOFF ratio versus TFE variation. It can be observed that the ratio of ION to IOFF (ION/IOFF) reaches its maximum at TFE = 4 nm. Our device design benefits from the assumption, supported by the increase in ION/IOFF with TFE, that the effect of NC at IOFF is negligible. For the device to function at low power, the SS is crucial. The device’s speed is also determined by SS. Further, SS should be lower to facilitate quicker changeover from the OFF to ON state. Variation in SS versus TFE is shown in Fig. 12. It is clear that with a TFE of 4 nm, SS is 20.8 mV/dec. This means that the surface potential is amplified by including the FE layer as the gate stack, which in turn causes the value of SS to drop below the 60 mV/dec.

Figure 13 depicts the transconductance (gm) curve as a function of gate voltage with and without the influence of NC. Transconductance is an electrical property related to both the output current and the input voltage.

Increasing the current results in a higher transconductance, revealing the device’s gain, since transconductance is proportional to current. From Fig. 13a, the gm of the NC-SP-DGTFET is 5.102 × 10−4 S/µm, which is much higher than the gm of SP-DGTFET (1.13 × 10−5 S/µm) and DGTFET (5.94 × 10−6 S/µm) as shown in Fig. 13b. The variation in transconductance versus gate voltage with different TFE is depicted in Fig. 14. The gain of the MOSFET is directly proportional to gm.35 From Fig. 14, it can be visualized that the increase in gate voltage improves the transconductance, further leading to higher gain. Since the proposed NC-SP-DGTFET is optimized at TFE = 4 nm, the gm is also noticed maximum at the same TFE as shown in Fig. 14.

A comparison of the obtained results with those available in the existing literature is illustrated in Table II. It is observed that the proposed device demonstrates superior performance over the other devices, which indicates that the proposed device is a promising candidate for high-speed applications.

Conclusion

This work analyses three tunnel field-effect transistor (TFET) structures: DGTFET, SP-DGTFET, and NC-SP-DGTFET. The ION/IOFF and SS are improved in NC-SP-DGTFET as compared with SP-DGTFET and DGTFET by 96%, 99% and 64%, 63% respectively. These enhancements are noticed due to the incorporation of SP and FE material in DGTFET. The pocket at the junction of the source and channel has been used to enhance the ON current as well as the FE material exhibits the improved electric field within the channel. The impact of varying the thickness of the FE material on the transfer characteristics, gm, and SS are also examined. The proposed device has lower SS, higher gm and better ION/IOFF ratio at TFE = 4 nm, rendering it an optimal selection for applications that prioritize both high speed and low power consumption.

References

R. Dennard, F. Gaensslen, W.-N. Yu, L. Rideout, E. Bassous, and A. Le Blanc, Design of ion-implanted small MOSFET’S dimensions with very. IEEE J. Solid State Circuits 9(5), 257 (1974).

A. Chaudhry and M.J. Kumar, Controlling short-channel effects in deep-submicron SOI MOSFETs for improved reliability: a review. IEEE Trans. Device Mater. Reliab.Reliab. 4(1), 99 (2004). https://doi.org/10.1109/TDMR.2004.824359.

K. Singh, S. Kumar, E. Goel, B. Singh, S. Dubey, and S. Jit, Effects of elevated source/drain and side spacer dielectric on the drivability optimization of non-abrupt ultra shallow junction gate underlap DG MOSFETs. J. Electron. Mater. 46, 520 (2017). https://doi.org/10.1007/s11664-016-4912-8.

Q. Xie, J. Xu, and Y. Taur, Review and critique of analytic models of MOSFET short-channel effects in subthreshold. IEEE Trans. Electron Devices 59(6), 1569 (2012). https://doi.org/10.1109/TED.2012.2191556.

Malvika, B. Choudhuri, and K. Mummaneni, A review on a negative capacitance field-effect transistor for low-power applications. J. Electron. Mater. 51, 923 (2022). https://doi.org/10.1007/s11664-021-09384-8.

D. Hisamoto, W. Lee, K. Jakub, H. Takeuchi, K. Asano, C. Kao, E. Anderson, T. King, J. Bokor, and C. Hu, FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47(12), 2320 (2000). https://doi.org/10.1109/16.887014.

P.M. Solomon, K.W. Guarini, Y. Zhang, K. Chan, E.C. Jones, G.M. Cohen, A. Krasnoperova, M. Ronay, O. Dokumaci, H.J. Hovel, J.J. Bucchignano Jr., C. Cabral, C. Lavoie, V. Ku, D.C. Boyd, K.S. Petrarca, J.H. Yoon, and H.S.P. Wong, Two gates are better than one. IEEE Circuits Devices Mag. 19(1), 48 (2003). https://doi.org/10.1109/MCD.2003.1175108.

A. Biswas, S.S. Dan, C. Le Royer, W. Grabinski, and A.M. Ionescu, TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron. Eng.. Eng. 98, 334 (2012). https://doi.org/10.1016/j.mee.2012.07.077.

K.M.C. Babu and E. Goel, Evolution of tunnel field effect transistor for low power and high speed applications: a review. SILICON 14(17), 11051 (2022). https://doi.org/10.1007/s12633-022-01826-0.

M.R. Uddin Shaikh, and S.A. Loan, Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628 (2019). https://doi.org/10.1109/TED.2019.2896674.

W. Li and J.C.S. Woo, Optimization and scaling of Ge-pocket TFET. IEEE Trans. Electron Devices 65(12), 5289 (2018). https://doi.org/10.1109/TED.2018.2874047.

D.B. Abdi and M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187 (2014). https://doi.org/10.1109/JEDS.2014.2327626.

T. Mikolajick, U. Schroeder, and S. Slesazeck, The past, the present, and the future of ferroelectric memories. IEEE Trans. Electron Devices 67(4), 1434 (2020). https://doi.org/10.1109/TED.2020.2976148.

N. Bagga, N. Chauhan, A. Bulusu, and S. Dasgupta, Demonstration of a novel ferroelectric-dielectric negative capacitance tunnel FET, in 2019 IEEE International Conference on Modeling of Systems and Circuits Devices, MOS-AK India 2019, pp. 102–105, (2019) https://doi.org/10.1109/MOS-AK.2019.8902381.

S. Guha and P. Pachal, Heterojunction negative-capacitance tunnel-FET as a promising candidate for Sub-0.4V VDDDigital logic circuits. IEEE Trans. Nanotechnol.Nanotechnol. 20, 576 (2021). https://doi.org/10.1109/TNANO.2021.3096252.

A. Singh, S.K. Sinha, and S. Chander, Impact of Fe material thickness on performance of raised source overlapped negative capacitance tunnel field effect transistor (NCTFET). SILICON 14(14), 9083 (2022). https://doi.org/10.1007/s12633-022-01696-6.

H.W. Kim and D. Kwon, Gate-Normal negative capacitance tunnel field-effect transistor (TFET) with channel doping engineering. IEEE Trans. Nanotechnol.Nanotechnol. 20, 278 (2021). https://doi.org/10.1109/TNANO.2021.3068572.

M. Kobayashi, K. Jang, N. Ueyama, and T. Hiramoto, Negative capacitance for boosting tunnel FET performance. IEEE Trans. Nanotechnol.Nanotechnol. 16(2), 253 (2017). https://doi.org/10.1109/TNANO.2017.2658688.

Y. Zhao, Z. Liang, Q. Huang, C. Chen, M. Yang, Z. Sun, K. Zhu, H. Wang, S. Liu, T. Liu, P. Yue, G. Han, and R. Huang, A novel negative capacitance tunnel FET with improved subthreshold swing and nearly non-hysteresis through hybrid modulation. IEEE Electron Device Lett. 40(6), 989 (2019). https://doi.org/10.1109/LED.2019.2909410.

G. Rasheed and S. Sridevi, Design and analysis of a dual gate tunnel FET with InGaAs source pockets for improved performance. Microelectron. J. 129, 105587 (2022). https://doi.org/10.1016/j.mejo.2022.105587.

A. Singh, N. Kumar, S.I. Amin, and S. Anand, Implementation of negative capacitance over SiGe sourced doping-less tunnel FET. Superlattices Microstruct. Microstruct. 145, 106580 (2020). https://doi.org/10.1016/j.spmi.2020.106580.

S. Dash, S.K. Mohanty, and G.P. Mishra, Segmented drain engineered tunnel field effect transistor for suppression of ambipolarity. SILICON 14, 1671 (2022). https://doi.org/10.1007/s12633-021-00973-0.

G.D. Das, S. Dash, and G.P. Mishra, Impact of hetero-dielectric engineering on the performance of single gate tunnel FET, in 2018 International Conference on Control, Power, Communication and Computing Technologies (ICCPCCT), Kannur, India, pp. 114–117, (2018) https://doi.org/10.1109/ICCPCCT.2018.8574222.

H. Bennett, International technology roadmap for semiconductors 2015 edition outside system connectivity, ITRS, https://tsapps.nist.gov/publication/get_pdf.cfm?pub_id=919731, http://www.itrs2.net/401/login.php?redirect=/ircfocus-teamsitwg-information.html. Accessed 27 Feb 2024.

H.S.P. Wong, D.J. Frank, P.M. Solomon, C.H.J. Wann, and J.J. Welser, Nanoscale CMOS. Proc. IEEE 87(4), 537 (1999). https://doi.org/10.1109/5.752515.

Sentaurus Device User Guide, Version t-2022,03, Synopsys.inc. (Mountain View, CA, USA, 2022).

J. Gomez, S. Dutta, K. Ni, J.A. Smith, B. Grisafe, A. Khan, and S. Datta, Hysteresis-free negative capacitance in the multi-domain scenario for logic applications, in Technical Digest—International Electron Devices Meeting, IEDM, vol. 2019, no. i, pp. 138–141, (2019) https://doi.org/10.1109/IEDM19573.2019.8993638

C. Gastaldi, M. Cavalieri, A. Saeidi, E. O’Connor, F. Bellando, I. Stolichnov, and A.M. Ionescu, Negative capacitance in HfO2 gate stack structures with and without metal interlayer. IEEE Trans. Electron Devices 69(5), 2680 (2022). https://doi.org/10.1109/TED.2022.3157579.

L. Wang, M.R. Cho, Y.J. Shin, J.R. Kim, S. Das, J.G. Yoon, J.S. Chung, and T.W. Noh, Overcoming the fundamental barrier thickness limits of ferroelectric tunnel junctions through BaTiO3/SrTiO3 composite barriers. Nano Lett. 16(6), 3911 (2016).

C. Yoon, J.H. Lee, S. Lee, J.H. Jeon, J.T. Jang, D.H. Kim, Y.H. Kim, and B.H. Park, Synaptic plasticity selectively activated by polarization-dependent energy-efficient ion migration in an ultrathin ferroelectric tunnel junction. Nano Lett. 17(3), 1949 (2017).

K. Toprasertpong, K. Tahara, Y. Hikosaka, K. Nakamura, H. Saito, M. Takenaka, and S. Takagi, Low operating voltage, improved breakdown tolerance, and high endurance in Hf0.5Zr0.5O2 ferroelectric capacitors achieved by thickness scaling down to 4 nm for embedded ferroelectric memory. ACS Appl. Mater. Interfaces 14, 51137 (2022). https://doi.org/10.1021/acsami.2c15369.

C.I. Lin, A.I. Khan, S. Salahuddin, and C. Hu, Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans. Electron Devices 63(5), 2197 (2016). https://doi.org/10.1109/TED.2016.2514783.

B. Awadhiya, P.N. Kondekar, and A.D. Meshram, Effect of ferroelectric thickness variation in undoped HfO2-based negative-capacitance field-effect transistor. J. Electron. Mater. 48, 6762 (2019). https://doi.org/10.1007/s11664-019-07483-1.

K. Toprasertpong, K. Tahara, M. Takenaka, and S. Takagi, Evaluation of polarization characteristics in metal/ferroelectric/semiconductor capacitors and ferroelectric field-effect transistors. Appl. Phys. Lett. 116(24), 3 (2020). https://doi.org/10.1063/5.0008060.

P.K. Mudidhe and B.R. Nistala, An analytical drain current modelling of DMGC CGAA FET: a circuit level implementation. Phys. Scr. 98(11), 115008 (2023). https://doi.org/10.1088/1402-4896/acfcec.

A. Singh, S. Chaudhary, S.M. Sharma et al., Improved drive capability of silicon nano tube tunnel FET using halo implantation. SILICON 12, 2555 (2020). https://doi.org/10.1007/s12633-019-00350-y.

S. Yadav, R. Madhukar, D. Sharma et al., A new structure of electrically doped TFET for improving electronic characteristics. Appl. Phys. A 124, 517 (2018). https://doi.org/10.1007/s00339-018-1930-9.

A.N. Hanna and M.M. Hussain, Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 117, 1 (2015). https://doi.org/10.1063/1.4905423.

D. Shekhar and A. Raman, Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl. Phys. A 126, 441 (2020). https://doi.org/10.1007/s00339-020-03615-1.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Babu, K.M.C., Goel, E. Analysis of Negative Capacitance Source Pocket Double-Gate TFET with Steep Subthreshold and High ON–OFF Ratio. J. Electron. Mater. 53, 3861–3869 (2024). https://doi.org/10.1007/s11664-024-11102-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-024-11102-z