Abstract

Power efficiency and performance requirements are driving the trend towards smaller interconnects in 3D packaging. Also, significant ongoing effort is aimed at finding alternatives to SnAgCu (SAC) solder alloys, either for low-temperature reflow or high reliability. Therefore, there is a need to characterize such alloys at dimensions relevant to their applications. Typically, such characterization involves testing the devices, followed by cross-sectioning and polishing to observe failure mechanisms. The drawback of this method is that the material removal due to polishing may reduce the amount of data that can be obtained. Also, cross-sectioning the devices renders them unusable for further testing, thus creating a discontinuity in the experiments. In this study, a procedure is outlined for fabricating devices termed in-line microjoints, featuring multiple Cu–solder–Cu junctions in either a straight line or a serpentine arrangement, enabling non-destructive characterization of the solder. Using this procedure, devices can be made with any commercially available solder paste, which enables testing of various alloys. The electromigration of Bi in SnBi low-temperature solder is characterized non-destructively and the diffusivity of Bi is reported at 75°C, 90°C, and 105°C. The reported diffusivity values align with the existing literature on Bi diffusivity. We also report a transient phenomenon in SnBi solder joints, where the initial rate of resistance change is non-linear, followed by a transition to a linear rate. Lastly, tests on the serpentine structures show lower Bi accumulation in regions where current crowding is expected, which is counter-intuitive.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Advanced packaging through 2.5D and 3D integration has gained significant popularity due to the cost advantage and enablement of heterogeneous integration, all without significant loss of performance or area.1 The selection of solder materials for advanced packaging relies on critical factors, including melting point, mechanical properties, thermal cycling behavior, and overall reliability, among others. For instance, SnBi low-temperature solders (LTS) find application in scenarios where concerns regarding processing temperatures, warpage, and energy consumption exist.2,3 SnAg solders are preferred for microbumps to enhance interconnect reliability.4 As interconnect dimensions shrink, novel reliability challenges emerge. One such example is the occurrence of voiding within SnAg microbumps induced by electromigration or thermal aging.5,6 Another instance of reliability challenges stemming from scaling down is the segregation and accumulation of Bi at the anode when SnBi the LTS is subjected to electromigration.7,8

Typically, characterization of interconnects is carried out by cross-sectioning and polishing of the interconnects after testing, making further testing of solder bumps infeasible, and potentially leading to information loss due to polishing. In contrast, a non-destructive characterization technique allows for continued testing on the device after imaging, thus requiring less time and fewer test devices. Previous studies have demonstrated non-destructive characterization of intermetallic compound growth using V-shaped grooves.9,10 The V-shaped devices do not mimic the structure of a solder joint, but can be effectively used to study intermetallic growth. Test devices with electroplated Sn channels in Cu lines have also been previously fabricated.5 However, achieving accurate solder composition and ensuring effective solder adhesion to copper was challenging in these devices. These challenges were later addressed by using a fabrication process with solder paste instead of electroplating, but this resulted in excess solder seeping beyond the intended area, affecting the current path in the device.11 Inspired by Prasad et al.,5 recently, other authors have begun to explore in-line test structures for electromigration.12 However, their work did not use Si fabrication techniques and is therefore not scalable to smaller length scales.

In this paper, we describe a fabrication procedure for in-line microjoints with Cu–solder junctions which can use any commercially available solder alloy. We demonstrate this fabrication process for both SnAgCu solder and SnBi microbumps in straight line and serpentine configurations. We perform electromigration characterization of SnBi LTS under elevated current densities. The devices can be used to concurrently track both the thickness of Bi accumulation at the anode and the resistance change. We describe a simple methodology to estimate the growth rate of Bi using resistance growth. The diffusivities obtained from resistance growth and Bi accumulation are compared with each other and with values found in the literature. Additionally, we also report a transient phenomenon where the initial rate of resistance change is non-linear, followed by a transition to a linear rate. Furthermore, tests on the serpentine structures show lower Bi accumulation in regions where current crowding is expected, which is counter-intuitive.

Methods

This section outlines the test device design, device fabrication process, and experimental procedure for characterizing Bi phase accumulation under electromigration.

In-Line Microjoint Design and Experimental Setup

The in-line microjoint design, depicted in Fig. 1a and b, closely follows the Cu–solder lines developed in prior studies.5,11 The base layer comprises Ti (20 nm), Ni (80 nm), and Au (20 nm) to enable electroplating. Each Cu–solder–Cu segment is representative of a single interconnect. The ‘+’ shape of the Cu line secures the plated copper structures during the spin-coating process, while the four pads correspond to the contact points for Kelvin 4-wire measurements. Devices can be fabricated with varying lengths of Cu and solder lines to study the effect of line length. In this work, the line segment length \(L_\text{sol}=100\) \(\mu \hbox {m}\), and the width w is either 50 \(\mu \hbox {m}\) or 80 \(\mu \hbox {m}\) depending on the required current density. The thickness of all the devices in this study is 15 \(\mu \hbox {m}\).

The experimental setup in Fig. 1c and d has been previously used to characterize the effect of adhesion of capping layers on resistance to voiding in a Cu line during electromigration.13 It includes an HTS24 24-W resistive ceramic heater from Thor Labs used to heat the sample to the required temperature. The temperature was regulated using a 5R7-388 proportional–integral–derivative controller from Oven Industries with input from a Type-T thermocouple attached to the base of the ceramic heater.

The design can also be modified to include serpentine lines to study the effect of current crowding on Bi accumulation and voiding, as shown in Fig. 2. The serpentine structure has line segment length \(L_\text{sol} = 100\) \(\mu \hbox {m}\) and width \(w = 80\) \(\mu \hbox {m}\). Such devices enable the study of regions with current crowding which are in general the initial location of fracture and/or voiding.

Tests were conducted in four experimental conditions, varying temperature, T, and current density, j, as shown in Table I. Bi thickness was measured for each of the conditions using scanning electron microcopy (SEM) and back-scatter electron (BSE) imaging. Each test consisted of multiple runs. For each of the runs, the sample was first heated to the testing temperature and then the current was applied using a Keithley 2450 Sourcemeter. The resistance was logged throughout each of the runs using a custom-designed LABVIEW program. Following the completion of each run, the current was stopped and the sample was brought to room temperature. The samples were imaged in between the runs to obtain the Bi thickness.

Test device design schematic showing (a) top view and (b) cross-section view, \(L_\text{sol}=100\) \(\mu \hbox {m}\), and w is either 50 \(\mu \hbox {m}\) or 80 \(\mu \hbox {m}\). (c) 4-probe experimental setup showing ceramic heater and thermocouple. (d) Optical microscope image of the test device and the probes.

Fabrication Procedure

The fabrication process is detailed in Fig. 3. AZ 15nXT, a high-temperature negative photoresist, was used for all the steps. The base layer was deposited on a Si wafer using E-Beam evaporation without breaking vacuum. The Ti in the base layer serves as an adhesion layer, while Ni serves as a seed layer for electroplating. A final layer of Au prevents oxidation of the Ni layer. An additional layer of Ti is required on top of the Au in the base layer to prevent the solder from seeping between the photoresist and the base layer.11 This is crucial as Ti has better adhesion with photoresists compared to Ni or Au. However, while the photoresist has good adhesion with Ti, solder does not. The Ti film might oxidize and pose difficulty for Cu electroplating. To address these issues, Ti was not deposited in regions where Cu or solder was to be deposited. This was enabled by protecting the regions that do not need Ti using a sacrificial layer of photoresist and performing a liftoff.

The Ti liftoff was followed by lithography for the Cu mask, and then Cu electroplating was carried out. After Cu electroplating, the base layer was etched to isolate the test structures electrically. The etching was carried out in three steps. First, buffered oxide etch (BOE) was used to etch the top Ti layer, which was followed by aqua regia (3:1 HCl:HNO3) for the Au and Ni layers. Finally, another round of etching using BOE was performed for the bottom Ti base layer. Following the etching, a photoresist coat was applied for solder deposition. Solder paste was then squeegeed into the solder channel. Prior to reflow, the deposition of the solder paste was confirmed using an optical microscope. This ensured that all the channels were filled with solder to form a complete interconnect. After reflow, the resist was stripped using Dynastrip 7700 resist remover. SEM images of samples fabricated with SnBiAg LTS (42% Sn, 57.6% Bi, 0.4% Ag) and SnAgCu (SAC) solder (96.5% Sn, 3% Ag, 0.5% Cu) are shown in Fig. 4a and b, respectively. Figure 4c and d show the corresponding BSE images. The eutectic SnBi structure i clearlys visible in the BSE image (Fig. 4c) with Bi being the lighter phase and Sn being the darker phase. The typical scallop-shaped Cu\(_6\)Sn\(_5\) intermetallic compound is visible in the BSE image of the Sn-Ag solder without polishing (Fig. 4d).14,15 The SnBiAg LTS solder was reflowed at 185°C for 1 min and the Sn-Ag solder was reflowed at 280°C for 1 min.

Results

In our study, we used electron microscopy imaging and resistance growth measurements to characterize electromigration in SnBi LTS. This section gives a brief overview of the results obtained from the experiments.

Bi Accumulation Observations

During electromigration testing, the solder undergoes voiding at the cathode and Bi accumulation at the anode. SEM images after 3 h, 9 h, and 15 h of testing of a bump tested at 105°C and 62.5 kA/\(\hbox {cm}^{2}\) are shown in the top row of Fig. 5a. Voiding is visible at the cathode in the SEM images, while the growth of the Bi layer at the anode towards the right is visible in the BSE images in the bottom row of Fig. 5a.

(a) SEM (top row) and BSE (bottom row) images of samples tested at 105°C and 62.5 kA/\(\hbox {cm}^{2}\) (experiment 4) for 3 h, 9 h, and 15 h. In the BSE images, Bi is the lighter phase. (b) Schematic of Bi segregation in solder where Bi is accumulating at the anode. (c) Average Bi thickness versus time. Refer to Table I for legend.

The Bi thickness was measured at 10 different locations and averaged. The thickness was measured at the same 10 locations for a particular bump after each run. BSE images in Fig. 5a (bottom row) show an example measurement where \(x_i\) is the thickness of the Bi layer at location I at each time interval. Figure 5b shows a simplified schematic of Bi accumulation with average thickness x. The thickness of Bi shows linear growth with time,. as shown in Fig. 5c. As intuitively expected, for tests at 105°C , the rate of growth of the Bi layer is more at higher current density (Test 4) compared to the lower current density (Test 3). Also, for tests at the same current density, the rate of growth of Bi is more at higher temperature (Test 4) compared to the test at the lower temperature (Test 2).

In some of the bumps, the Bi accumulates at the middle of the bump, as shown in Fig. 6a. This is due to the presence of a large Bi phase region at the bump’s center, either following the reflow process or during electromigration testing. If the thickness is measured at the middle, it forms a straight line, which is demonstrated in Fig. 6b for an experiment at 75°C and 100 kA/\(\hbox {cm}^{2}\). The rate of Bi growth is 0.38 \(\mu \hbox {m}\)/h, which is similar to the 0.44 \(\mu \hbox {m}\)/h obtained for Experiment 1 from the Bi growth at the anode shown in Fig. 5c. Bumps with accumulation at the center were not included in characterizing the average growth of Bi. Such Bi accumulation can occur in SnBi bumps with diameters smaller than 80 \(\mu \hbox {m}\). If the distribution of Bi phase is even after reflow, then Bi accumulates only at the anode.

Serpentine devices were also tested at 90°C and 62.5 kA/\(\hbox {cm}^{2}\). The Bi accumulation for bump 3 and bump 5 (refer to Fig. 2 for bump numbering) are shown in Fig. 7a and b, respectively. The change in direction of the electrons is also marked in Fig. 7a and b. Counter-intuitively, instead of Bi accumulation occurring at the corner where current crowding is expected, Bi tends to accumulate away from the corner. This may be due to the Bi accumulation affecting the current path, but the exact reason for this phenomenon is yet to be determined.

Bi Accumulation in serpentine devices tested at 90°C and 62.5 kA/\(\hbox {cm}^{2}\) (a) bump 3 and (b) bump 5 (refer Fig. 2 for bump numbers). The flow of electrons is marked by the arrows.

Resistance Growth

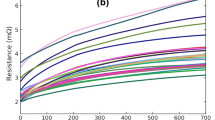

The resistance increase of the solder during electromigration can be attributed to the accumulation of Bi at the anode. Bi has a higher resistivity of \(107 \times 10^{-8}\) \(\Omega \; \hbox {m}\) compared to SnBi solder with resistivity \(30 \times 10^{-8}\) \(\Omega \; \hbox {m}\).16,17 Therefore, when Bi accumulates at the anode, it increases the resistance of the whole bump. The evolution of the resistance R with time for each of the experimental conditions tested is shown in Fig. 8a.

The jumps in the resistance correspond to the end of one run and the beginning of the next. The longer breaks, for example, the interruptions in Test 2, were due to data logging lapse in the LABVIEW program. From the second/third runs onwards, the resistance shows an initial region at the beginning marked by a steep increase in the resistance before settling into a linear growth trend. Also, the starting resistance of a run is considerably lower than the resistance at the end of a previous run. This phenomenon was observed in all the experimental conditions to a varying extent. The transient growth of resistance occurs over time spans in the range of 30–90 min. This is much longer than expected from joule heating.18,19 Transient resistance change in SnBi solder during interrupted testing has not been reported in earlier studies and the cause for such an increase is yet to be determined.

Linear fits to the resistance growth curves are plotted in Fig. 8b. The first two runs of each test were not considered for the fits due to the large slopes compared to the other runs. Furthermore, the initial transient segments of the runs were removed before fitting since they were not due to Bi accumulation. Due to voltage measurement errors in the power supply during tests at 105°C and 62.5 kA/\(\hbox {cm}^{2}\), the slope of its resistance was lower than expected. Therefore, this test was not used for the diffusivity calculation discussed in the following section.

(a) Resistance, R, versus time, t, plot of all the experiments. Each test is comprised of multiple runs; the jumps in the resistance correspond to the end of one run and the beginning of the next. Refer to Table I for experimental parameters. (b) Linear fits for resistance growth; the first two runs and the initial transient region of each of the runs were not considered for the fit.

Discussion

Obtaining Bi Accumulation Rate from Resistance Growth Rate

The amount of Bi accumulated at the anode can be measured from the BSE images. From Fig. 5b, the resistance of the device can be approximated as:

where \(R_\text{Cu}\) is the resistance of the Cu line, \(R_\text{sol}\) is the resistance of solder region not part of the accumulated Bi, and the \(R_\text{Bi}\) is the resistance of the Bi layer. Using the resistivities of solder and Bi, it can be further expanded as:

where \(\rho _\text{sol} = 62 \times 10^{-8}\) \(\Omega \; \hbox {m}\) is the resistivity of the solder, \(\rho _\text{Bi} = 107 \times 10^{-8} \) \(\Omega \; \hbox {m}\) is the resistivity of Bi, and A is the cross sectional area. Since the resistivity of Cu is known, \(\rho _\text{sol}\) is obtained from the initial resistance and by assuming the Cu and the solder are resistances in series with known lengths and cross-sectional areas.

Since the resistance of the Cu line does not change:

where b is the slope of the linear fit for resistance in Fig. 8b. This gives:

Note that it is assumed that the voids at the cathode do not change the cross-section area, and that the voids and Bi depletion in the solder do not change the resistivity of the solder.

Diffusivity Calculation

The diffusive flux due to electromigration is written as:

where \(J_\text{Bi}\) is flux of Bi in kg cm\(^{-2}\) s\(^{-1}\), c is concentration of Bi in kg cm\(^{-3}\), \(k=1.38 \times 10^{-23}\) J/K is Boltzmann constant, \(e=1.6 \times 10^{-23}\) C is charge of an electron, D is diffusivity, \(Z^*\) is effective valence of electromigration, T is temperature, and j is current density. The rate of electromigration in SnBi solder depends on the concentration of Bi20. Therefore, the concentration c is chosen according to the initial composition of the solder, which is 0.57 \(\times \) \(d_\text{sol}\), where \(d_\text{sol}=8.2 \times 10^3\) kg/m\(^3\). It is assumed that all the Bi in the solder migrates towards the anode and that all the Bi that reaches the anode accumulates as a layer. Since 57.6% of the Bi is already present in the solder, the remaining portion accumulated at the anode is due to electromigration. Therefore, \(J_\text{Bi}\) can be written as \(0.424 \times d_\text{Bi}\frac{\text{d}x}{\text{d}t}\), where \(d_\text{Bi}\) is the density of bismuth.21 This gives

The value of \(DZ^*\) can be calculated independently by using \(\frac{\text{d}x}{\text{d}t}\) values obtained from BSE images (Fig. 5c), and from the slope of the resistance linear fits. The variation of \(DZ^*\) obtained from both methods with temperature is plotted in Fig. 9. The values obtained from the resistance growth rate and the Bi growth rate are in good agreement with each other. The diffusivity calculated from the resistance growth rate can be particularly useful in scenarios where Bi accumulation rate cannot be easily measured. Additionally, in serpentine structures or structures with complicated geometry, the resistance growth rate can be used to obtain an average diffusivity.

\(DZ^*\) calculated from resistance, Bi thickness measurement, and literature-derived values plotted against 1/T.7

Conclusions

Test devices capable of non-destructive characterization of microbumps were designed and fabricated. The fabrication procedure allows deposition of solder pastes to form in-line joints, which enables testing of any commercially available solder alloy. As an application, the accumulation of Bi at the anode due to electromigration was characterized. The diffusivity of the Bi due to electromigration was calculated by two methods, using Bi thickness from BSE imaging and using the resistance growth rate. The values of diffusivity obtained are in good agreement with each other and with values found in the literature. This application demonstrates the effectiveness of the non-destructive testing methodology. The devices can serve as test vehicles to compare solder alloys for different applications and allow for rapid testing.

A phenomenon of transient resistance growth was observed at the beginning of each experimental run. The duration of the transient growth was significantly longer than expected from joule heating but the specific cause for such behavior is yet to be determined. Additionally, tests were conducted on serpentine test devices to study the effect of current crowding. The Bi was observed to accumulate at regions away from expected current crowding. The cause for such behavior also needs further study.

References

K. Tu, Reliability challenges in 3D IC packaging technology. Microelectron. Reliab. 51(3), 517–523 (2011). https://doi.org/10.1016/j.microrel.2010.09.031.

F. Hua, Z. Mei, and J. Glazer, in 1998 Proceedings. 48th Electronic Components and Technology Conference (Cat. No.98CH36206) (1998), pp. 277–283. https://doi.org/10.1109/ECTC.1998.678706

Z. Mei and J.W. Morris, Characterization of eutectic Sn–Bi solder joints. J. Electron. Mater. 21(6), 599–607 (1992). https://doi.org/10.1007/bf02655427.

K. Tu, H.Y. Hsiao, and C. Chen, Transition from flip chip solder joint to 3D IC microbump: its effect on microstructure anisotropy. Microelectron. Reliab. 53(1), 2–6 (2013). https://doi.org/10.1016/j.microrel.2012.07.029.

S.P. Prasad, C. Jois, and G. Subbarayan, in 2022 21st IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm) (2022), pp. 1–8. https://doi.org/10.1109/iTherm54085.2022.9899684

Y.W. Chang, C. Hu, H.Y. Peng, Y.C. Liang, C. Chen, T. Chang, C.J. Zhan, and J.Y. Juang, A new failure mechanism of electromigration by surface diffusion of Sn on Ni and cu metallization in microbumps. Sci. Rep. (2018).https://doi.org/10.1038/s41598-018-23809-1.

X. Gu and Y. Chan, Electromigration in line-type Cu/Sn–Bi/Cu solder joints. J. Electron. Mater. 37(11), 1721–1726 (2008). https://doi.org/10.1007/s11664-008-0539-8.

Q.L. Yang and J.K. Shang, Interfacial segregation of bi during current stressing of Sn–Bi/Cu solder interconnect. J. Electron. Mater. 34(11), 1363–1367 (2005). https://doi.org/10.1007/s11664-005-0191-5.

H. Gan and K.N. Tu, Polarity effect of electromigration on kinetics of intermetallic compound formation in Pb-free solder v-groove samples. J. Appl. Phys. 97(6), 063514 (2005). https://doi.org/10.1063/1.1861151.

J.C. Mertens, A. Kirubanandham, and N. Chawla, In situ fixture for multi-modal characterization during electromigration and thermal testing of wire-like microscale specimens. Microelectron. Reliab. 55(11), 2345–2353 (2015). https://doi.org/10.1016/j.microrel.2015.07.158.

C. Jois, P.E. Chou, S.P. Prasad, C. Handwerker, and G. Subbarayan, in 2023 22nd IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm) (2023), pp. 1–5. https://doi.org/10.1109/ITherm55368.2023.10177512

P. Singh, L. Palmer, M. Hamid, T. Wassick, R.F. Aspandiar, B. Franco, H. Fu, R. Coyle, F. Hadian, V. Vasudevan, et al., Electromigration in tin–bismuth planar solder joints, in 2023 International Conference on Electronics Packaging (ICEP) (2023). https://doi.org/10.23919/icep58572.2023.10129714

S.P. Prasad, Y. Singh, P.K. Vaitheeswaran, and G. Subbarayan, The connection between electromigration resistance and thin-film adhesion and their degradation with temperature. IEEE Trans. Compon. Packag. Manuf. Technol. 13(3), 426–443 (2023). https://doi.org/10.1109/TCPMT.2023.3259299.

J.O. Suh, K.N. Tu, and N. Tamura, Preferred orientation relationship between Cu6Sn5 scallop-type grains and Cu substrate in reactions between molten Sn-based solders and Cu. J. Appl. Phys. 102(6), 063511 (2007). https://doi.org/10.1063/1.2776002.

W.J. Boettinger, C.A. Handwerker, and U.R. Kattner, Reactive Wetting and Intermetallic Formation (Springer US, Boston, 1993), pp. 103–140. https://doi.org/10.1007/978-1-4684-1440-0_4.

J.R. Rumble (ed.), Electrical Resistivity of Pure Elemental Metals, 104th edn. (CRC Press/Taylor & Francis, 2023)

A. Gain and L. Zhang, Interfacial microstructure, wettability and material properties of nickel (Ni) nanoparticle doped tin–bismuth–silver (Sn–Bi–Ag) solder on copper (Cu) substrate. J. Mater. Sci. Mater. Electron. (2016).https://doi.org/10.1007/s10854-015-4252-0.

Y. Hou and C.M. Tan, in 2008 10th Electronics Packaging Technology Conference (2008), pp. 1148–1153. https://doi.org/10.1109/EPTC.2008.4763584

B. Wu, M. Alam, Y. Chan, and H. Zhong, Joule heating enhanced phase coarsening in Sn37Pb and Sn3.5Ag0.5Cu solder joints during current stressing. J. Electron. Mater. 37(4), 469–476 (2008). https://doi.org/10.1007/s11664-006-0014-3.

K. Murayama, M. Aizawa, K. Oi, in 2021 IEEE 71st Electronic Components and Technology Conference (ECTC) (2021), pp. 1888–1893. https://doi.org/10.1109/ECTC32696.2021.00298

L. Chen and C. Chen, Electromigration study in the eutectic SnBi solder joint on the Ni/Au metallization. J. Mater. Res. 21(4), 962–969 (2006) . https://doi.org/10.1557/jmr.2006.0113.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors of the paper declare that there is no Conflict of interest regarding the publication of this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jois, C., Chou, PE. & Subbarayan, G. In-Line Test Structures and Non-destructive Characterization of Electromigration-Driven Phase Evolution in Microscale Solder Joints. J. Electron. Mater. 53, 3070–3077 (2024). https://doi.org/10.1007/s11664-024-11043-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-024-11043-7