Abstract

Some of the vital problems around the conventional CMOS technology are leakage-power consumption, physical-scalability limits, and short-channel effects. These deficiencies have led to many studies about nano-scale designs. Quantum dot cellular automata (QCA) is a potential answer in nanotechnology. Scholars have considered the four-dot squared cell as the main factor in the QCA. Also, a full-adder is a fundamental unit in every digital system. However, the importance of cell and area consumption limitation in circuit designing has been completely ignored in most of the related studies. Therefore, in this paper, we have offered a one-bit multi-layer full-adder cell. The practical accuracy of the proposed circuits has been assessed using QCADesigner. According to the obtained results and the design, the presented design has efficient cell usage against all the prior designs regarding cell counts and area occupation, leading to around 7% improvement in cell number than the common full-adder design. The simulation outcomes have also shown that the introduced design has excellent efficiency regarding cell and area aspects.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

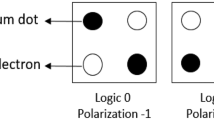

The present silicon-based technology encounters many important challenges and problems, reducing its ability as a low-power method for the future [1, 2]. High energy consumption, large-parametric variations, and decreased-gate control are the main problems, noticeably limiting the design of low-power and robust systems [3]. Hence, the researchers are investigating many new technologies such as nanowire transistors [4], single-electron transistors (SET) [5], and quantum dot cellular automata (QCA) [6,7,8,9] as the possible substitutions for the conventional silicon-based technologies [10]. The QCA, as newly emerging nanotechnology, is very interesting for performing the future energy-efficient digital systems, leading to low-power consumption, high-speed operation, and a dense structure [11,12,13]. This technology provides a nano-scale answer and suggests a new high-speed computation technique [14,15,16,17]. It has four quantum dots (made of ordinary semiconductive materials [18]), each of which has two free electrons [19,20,21]. Logic operations are accomplished via the QCA. The flow of data occurs in the circuit through the Coulombic interaction of the electrons [22]. Its structure is an array of quantum cells [23,24,25]. Instead of ordinary charge flow, the polarization effect has been used [26,27,28]. A three-input majority gate, wire, and inverter are the three key components commonly applied to the QCA [29,30,31].

Up to now, many QCA-based designs have been offered, but arithmetic circuits could be more attractive among all of them because of their extensive use in numerous applications [32,33,34]. The performance of the full-adder directly influences the performance of the whole system because it is the main element of arithmetic circuits [35]. Enhancing the efficiency of the adder is vital for improving the performance of the entire system [36, 37]. Therefore, designing QCA-based adder circuits with less complexity, a small area, and less delay is going to be a highly needed desire in the future [38]. Also, making QCA gates having low-power consumption has recently become more vital [39].

The main purpose of this research is to suggest a QCA-based full-adder design based on three-level cell placement. A new QCA-based full-adder has been proposed for outperforming the previously presented adders regarding the area, cell count, and delay. Concisely, the goals are as follows:

-

Offering a three-level design for one-bit QCA-based full-adder;

-

Decreasing the cell number in one-bit QCA-based full-adder;

-

Decreasing the consumption area of one-bit QCA-based full-adder;

-

Comparing the complexity of the presented design with other recently proposed designs.

The structure of the article is as follows: Part 2 provides an overview of the QCA technology and the related works. Part 3 presents a new model for the full-adder and its basic structures plus the operation of the preceding ones. Part 4 presents the simulation results. Finally, the last section provides conclusions and future work.

2 Background and related work

Here, we have reviewed the previous studies to better comprehend QCA technology's architecture and its impact on designing the full-adder.

2.1 Fundamentals of QCA

Lent, et al. [19] presented the QCA as a possible nano-scale technology to design logical devices. Various researchers have worked on developing new ideas for this technology. The QCA cell is a container with a limited number of dots distributed along the cell perimeter, where two charged particles can occupy these dots [40]. The arrangement of cell dots is such that the cell identifier can only have two stable states (or mechanical ground states) [41]. The cell has two polarizations to signify logic “0” and logic “1.” Figure 1a shows the switching between two states, performed by mechanically enabling the charged particles to tunnel among the dots. Figure 1b indicates that the QCA cells can have two different statuses (+1 and −1). Information is exchanged between one cell and its neighboring cells as a result of the Coulombic interaction. It is just needed to force the input cell to a specific polarization, and the cell will force the adjacent cell to the same polarization. The information is carried across a wire of adjacent cells, as shown in Figs. 1c and 2 [42].

The QCA cells; a functional diagram, b available cell types, and c QCA wire types [42]

The QCA inverter gates [43]

A major logic gate in the QCA is a three-input majority gate shown in Fig. 3a. As a result of electrostatic repulsion, the majority gate’s central cells stabilize the polarization of the output.

a Three-input majority gate, b two-input OR gate, and c two-input AND gates [44]

We can attain an AND/OR gate by setting the polarization of one input of the majority gate to logic “1” or “0.” When “0” is assigned to one input, the majority gate runs similar to the AND of the 2 other inputs. At the same time, if “1” is assigned to one input, the majority gate runs similar to the OR of the 2 other inputs. For instance, if the output is “1,” then at least two inputs with logic “1” are needed. We can configure a majority gate to operate as an AND/OR gate. To reach this aim, we have set one input to p = \(- {1}\) or p = \(+ {1}\) to have an AND or an OR, correspondingly. Figure 3b indicates the majority gate's function as a two-input OR gate, and Fig. 3c shows its function as a two-input AND gate.

In addition, the scientists have theorized an ideal and reduced organization for the five-input majority gate [45] to improve the area in the QCA-based 3-input majority gate compared to silicon-based technologies. The ideal design for a full-adder cell based on the 5-input majority gate has five gates: 3-input majority gates and two inverters. Up to now, many executions of a 5-input majority gate have been described [32, 46]. Figure 4a shows that it is not possible to access the input cells (B and C) through a solo level in the 1st QCA layout. Figure 4b shows another structure that other cells surround the output cell. Furthermore, the creators of 2 new architectures (Fig. 4c, which is presented in [47], and Fig. 4d, which is given in [46]) have tried to solve the mentioned shortcomings by suggesting a new device.

In QCA technology, there are four phases for the clock signal in the QCA circuit to ensure that the state switching is not abrupt but adiabatic. Due to the fact that in the sudden switching, the input is suddenly changed and attempted to relax in a ground mode using dissipating energy, the relaxation is uncontrolled and inelastic. So, it is probable that the circuit enters a metastable state determined by the local ground mode, not by the global one. The Landauer [50] and Bennet [51] clocking signals are two types of clocking signals commonly used for clocking the QCA circuits. Magnetic cellular automata (MCA) is a kind of QCA, where neighboring single-domain nanomagnets are responsible for the process and propagate the information through mutual interaction. Kumari and Bhanja [50] have proposed a spatially moving Landauer clocking design for MCA arrays. Figure 5 shows the Landauer clock waveform. Each clock signal has 4 steps: Switch, Hold, Release, and Relax. The Switch phase lasts until the full polarization of the cell. When the clock gets to the Hold step, the cell preserves its polarization. Finally, the cell becomes un-polarized at the low level of the clock (the Relax step).

The Landauer clock waveform [50]

Finally, in the QCA structures, making connections between components should be done efficiently to have better stability. Wire crossing is an essential factor in the QCA design to reach the mentioned goal. So far, three crossing methods have been suggested, having single-layer (Fig. 6a), multi-layer (Fig. 6b), and logical crossing (Fig. 6c) [42], respectively.

The wire crossing. a Single-layer, b Multi-layer wire, and c Logical crossing [42]

2.2 Related work

Up to now, great attempts have been made in different studies to show an efficient and simple model for one-bit full-adder cell; most of them have used a 3-input majority gate. The latest models have been studied in the following.

Navi, et al. [6] have introduced a five-input majority gate model, needing only two majority gates and two inverters implemented through diagonal cells. The full-adder design has been contrasted to the previous one based on complexity, area, and latency. The suggested adder has a good architecture, helping the upcoming arithmetic QCA-oriented circuit models. The suggested device has decreased cell counts and area, using a traditional type of QCA cells. The proposed design has a more straightforward structure and requires fewer cell counts and area than the previous designs, though it has an equal latency. Also, the proposed design of majority gates and full-adder has improved the designing of logical circuits.

Also, Molahosseini, et al. [32] have presented a simple 5-input majority gate for QCA full-adder. It is powerful regarding the implementation of digital functions. We can decrease the hardware request for a QCA model using gates like those. The circuit optimizes the number of gates, and clock steps, too. The challenge with this approach is the coupling problem among cells with other circuits. Some physical evidence has been presented to confirm the performance of the suggested device. QCADesigner has been applied to check the thorough functionality of the full-adder via computer simulations. The simulation results and physical relations have confirmed the usefulness of the design.

Also, Sayedsalehi, et al. [52] have proposed a model for the QCA-oriented full-adder. The increase of the carry signal through full-adder cells has been considered as the key cause of delay in the adder circuits. The full-adders have been suggested with the purpose of limiting the effect of the carry dissemination delay. This method has some benefits over some other methods: simple and efficient outline leading to very few gates, small zone, and less delay. QCADesigner tool has been employed to simulate the circuits for checking their functionality. We have shown the advantage of the introduced design compared to the current adders regarding gate counts, area, and latency.

Also, Navi, et al. [53] have proposed a configurable QCA circuit to do numerous logic functions like the AND and OR. The consumed hardware for a QCA model can be decreased, and numerous functions can be achieved through these kinds of circuits. Also, an efficient QCA design has been proposed as a full-adder, according to the designed circuits. They have also juxtaposed the proposed model with the preceding ones. The adder has excellent efficiency in terms of complexity, latency, and size.

Abedi, et al. [54] have presented a coplanar QCA-based crossover architecture for full-adders to decrease QCA cells and area consumption. The crossover has employed non-adjacent clock areas for 2 crossing wires. According to the obtained results, the enhancement is 23% and 48% for cell counts and the area, respectively, compared with that of the presented QCA-based design. The suggested QCA-oriented full-adder has been employed in designing QCA-based ripple carry adders, in which 17–41% advance in cell numbers and 22–69% in area occupation have been obtained compared with those of the previous ripple carry adder. The design cost is lower than that of the preceding QCA-oriented adders, according to the QCA-specific cost measurement, counting those with carry accelerating techniques.

Finally, Sarmadi, et al. [55] have suggested an improved one-bit full-adder relying on the QCA technology with six active layers. All the previous designs can be affected by the presented one-bit full-adder regarding cell numbers and area consumption. Six active layers in a creative approach have been employed to offer the correct functionality and the least viable occupation area using this circuit, resulting in keeping the suggested full-adder’s size equal to a five-input majority gate. The complexity of the top layer and the cost of insinuation are the disadvantages of the proposed technique.

3 Proposed design

Here, we have introduced a novel QCA-oriented full-adder with a five-input majority gate [5, 15]. The structure of its cells follows the schematic design of Fig. 7. The operation of the design is shown in Fig. 8, which can be represented by:

The suggested full-adder design has been structured for proposing a high-speed adder to decrease the carry dissemination delay in bigger models. The proposed full-adder has 2 separate blocks, according to Fig. 8. The first block is a 3-input majority gate and produces the \({\text{C}}_{{{\text{out}}}}\) signal. The other block contains a five-input majority gate and an inverter and produces the \(Sum\) signal. Each block has been managed at a different level. So, in the upper layer, \(C_{out}\) has been generated and transferred to the primary layer. The Sum signal has been generated by feeding the inputs and \(C_{out}\) to a 5-input majority gate.

Figure 9 shows the final layout views of the full-adder, according to the 5-input majority gate. This design has been managed in three layers to optimize the hardware requirements, the number of cells, and area occupation. The n-bit adders can also be implemented simply using this block.

Figure 10 shows the design, cell outline, and clock phases of the proposed adder. The first level has 3 inputs (A, B, C) and 1 output (Carry). The carry has been generated by means of three-input majority gate and directly sent to the output (Carry). As SUM has been fed into the 5-input majority gate, we have needed an added clock step to have a steady throughput. Therefore, three clock phases are needed for producing the outputs, as shown in Fig. 11. Also, Table 1 shows the truth table of the one-bit full-adder circuit.

4 Simulation results

The introduced full-adder has been simulated via QCADesigner 2.0.3 [57]. This section provides a brief discussion about the simulation tools, accuracy analysis, and the simulation results.

4.1 Simulation tool and parameters

Circuit creators need a swift and exact tool for simulating and designing to explain the performance of the QCA circuits. They can design a QCA circuit using QCADesigner among a set of CAD tools. QCADesigner is helpful in generating a fast and exact simulation and outline tool for QCA. The simulation of the QCA circuits has been done by QCADesigner [57]. The proposed full-adder and 3-input majority gate are simulated using the QCADesigner 2.0.3. The simulation engines are set to “Bistable Approximation” type as shown in Table 2. Also, the applied coherence vector parameters are shown in Table 3 [57].

4.2 Accuracy analysis

The simulation outcomes for the suggested one-bit full-adder are depicted in Fig. 12. The results for all combinations of the inputs (marked with the blue rectangle) are shown in Fig. 12. Based on the results, the suggested design is accurate, and the introduced QCA-oriented full-adder design outperforms the other ones. The first CARRY and SUM signals (marked with the red rectangle) waveforms have been obtained after 0.25 and 0.75 clocking cycles (marked with the black rectangle), correspondingly.

4.3 Comparisons

Table. 4 shows four parameters of full-adders designs introduced in the related studies alongside the proposed design. The progress of the design is significant concerning the number of cells (intricacy) and the area. We have used 28 QCA cells in the introduced model. The area of the total plan has also been decreased in the proposed design. The delay is three in the proposed design, which is the minimum clock phase. Therefore, the introduced design has improved the area consumption and delay. Also, the configuration of the QCA cells is important for effectiveness and performance. This design provides nearby more than 7% enhancement in cell numbers.

5 Conclusion

We have suggested a 3-level full-adder based on QCA arithmetic units. We have examined the average leakage and switching power dissipations by using a precise QCA power dissipation design. We have employed three active layers, in an innovative approach, to provide the proper functionality and the least occupation area with this circuit, leading to keeping the size of the introduced full-adder cell equal to that of a 5-input majority gate. After completing the administration and verification processes using the QCADesigner environment, we have reached an effective circuit optimization compared with the current models regarding the number of cells and area occupation.

The introduced optimal structure can help design the future QCA-based nano-scale circuits. We have designed a new full-adder, and it will be helpful for the designing of bigger units. Also, we have considered the offered model as a good answer for designing with the least count of QCA-based cells with fewer crossovers.

References

Bolhassani, A., Haghparast, M.: Optimized designs of reversible arithmetic logic unit. Turk. J. Electr. Eng. Comput. Sci. 25(2), 1137–1146 (2017)

Seyedi, S., Darbandi, M., and Navimipour, N. J.: Designing an efficient fault tolerance D-latch based on quantum-dot cellular automata nanotechnology. Optik 185, 827–837 (2019)

Roy, K., Mukhopadhyay, S., Mahmoodi-Meimand, H.: Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 91(2), 305–327 (2003)

Schmidt, V., Riel, H., Senz, S., Karg, S., Riess, W., Gösele, U.: Realization of a silicon nanowire vertical surround-gate field-effect transistor. Small 2(1), 85–88 (2006)

Abu El-Seoud, A., El-Banna, M., Hakim, M.: On modelling and characterization of single electron transistor. Int. J. Electron. 94(6), 573–585 (2007)

Navi, K., Sayedsalehi, S., Farazkish, R., Azghadi, M.R.: Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010)

Seyedi, S., Darbandi, M., Navimipour, N.J.: Designing an efficient fault tolerance D-latch based on quantum-dot cellular automata nanotechnology. Optik 185, 827–837 (2019)

Seyedi, S., Ghanbari, A., Navimipour, N.J.: New design of a 4-bit ripple carry adder on a nano-scale quantum-dot cellular automata. Mosc. Univ. Phys. Bull. 74(5), 494–501 (2019)

Mosleh, M.: A novel design of multiplexer based on nano-scale quantum-dot cellular automata. Concurrency Computat. Pract. Exper. 31(13), e5070 (2019)

Mohammadi, Z., Mohammadi, M.: Implementing a one-bit reversible full adder using quantum-dot cellular automata. Quantum Inf. Process. 13(9), 2127–2147 (2014)

Andrecut, M., Ali, M.: Entanglement dynamics in quantum cellular automata. Phys. Lett. A 326(5), 328–332 (2004)

Hasani, B., Navimipour, N. J.: A new design of a carry-save adder based on quantum-dot cellular automata. Iran. J. Sci. Technol. Trans. Electr. Eng. 45, 993–999 (2021)

Banik, D., Rahaman, H.: Quantum-dot cellular automata latches for reversible logic using wave clocking scheme. IETE J. Res. (2020). https://doi.org/10.1080/03772063.2020.1819886

Kim, K., Wu, K., Karri, R.: The robust QCA adder designs using composable QCA building blocks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1(26), 176–183 (2007)

Gadim, M.R., Navimipour, N.J.: A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst. Technol. 24, 1295–1305 (2018)

Sarvaghad-Moghaddam, M., Orouji, A.A.: New symmetric and planar designs of reversible full-adders/subtractors in quantum-dot cellular automata. Eur. Phys. J. D 73(6), 125 (2019)

Fam, S.R., Navimipour, N.J.: Design of a loop-based random access memory based on the nanoscale quantum dot cellular automata. Photon Netw. Commun. 37(1), 120–130 (2019)

Walus, K., Jullien, G.A.: Design tools for an emerging SoC technology: quantum-dot cellular automata. Proc. IEEE 94(6), 1225–1244 (2006)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49 (1993)

Sandhu, A., Gupta, S.: Performance evaluation of an efficient five-input majority gate design in QCA nanotechnology. Iran. J. Sci. Techno. Trans. Electr. Eng. (2019). https://doi.org/10.1007/s40998-019-00296-2

Das, J.C., De, D.: Reversible priority encoder design and implementation using quantum-dot cellular automata. IET Quantum Commun. 1(2), 72–78 (2020)

Ilanchezhian, P., Parvathi, R.: Nanotechnology based effective design approach for code converter circuits using QCA. Int. J. Comput. Appl. 69(8) (2013)

Latha, K., Maharshi, M.N.: Design of adders using qca. Int. J. Adv. Eng. Technol. 6(4), 1750 (2013)

Das, J.C., De, D.: Operational efficiency of novel SISO shift register under thermal randomness in quantum-dot cellular automata design. Microsyst. Technol. 23, 4155–4168 (2017)

Nejad, M.Y., Mosleh, M.: A review on QCA multiplexer designs. Majlesi J. Electr. Eng. 11(2), 69–79 (2017)

Rao, N.G., Srikanth, P., Sharan, P.: A novel quantum dot cellular automata for 4-bit code converters. Optik-Int. J. Light Electron Optics 127(10), 4246–4249 (2016)

Sen, B., Mukherjee, R., Mohit, K., Sikdar, B.K.: Design of reliable universal QCA logic in the presence of cell deposition defect. Int. J. Electron. 104(8), 1285–1297 (2017)

Seyedi, S., Navimipour, N.J.: Design and evaluation of a new structure for fault-tolerance full-adder based on quantum-dot cellular automata. Nano Commun. Netw. 16, 1–9 (2018)

Ahmad, F., Bhat, G.: Novel code converters based on quantum-dot cellular automata (QCA). Int. J. Sci. Res. 3(5), 364–371 (2012)

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE Trans. Very Large Scale Integr (VLSI) Syst. 19(9), 1535–1548 (2010)

Heikalabad, S.R., Kamrani, H.: Design and implementation of circuit-switched network based on nanoscale quantum-dot cellular automata. Photonic Netw. Commun. 38(3), 356–377 (2019)

Molahosseini, A.S., Navi, K., Dadkhah, C., Kavehei, O., Timarchi, S.: Efficient reverse converter designs for the new 4-moduli sets and based on new CRTs. IEEE Trans. Circuits Syst. I Regul. Pap. 57(4), 823–835 (2010)

Peskin, U., Abu-Hilu, M., Speiser, S.: Approaches to molecular devices based on controlled intramolecular electronic energy and electron transfer. Electron transfer rates through flexible molecular bridges by a time-dependent super exchange model. Opt. Mater. 24(1), 23–29 (2003)

Moharrami, E., Navimipour, N.J.: Designing nanoscale counter using reversible gate based on quantum-dot cellular automata. Int. J. Theor. Phys. 57, 1060–1081 (2018)

Seyedi, S., Navimipour, N.J.: Designing a new 4:2 compressor using an efficient multi-layer full-adder based on nanoscale quantum-dot cellular automata. Int. J. Theor. Phys. 60, 2613–2626 (2021)

Navi, K., et al.: A novel low-power full-adder cell with new technique in designing logical gates based on static CMOS inverter. Microelectron. J. 40(10), 1441–1448 (2009)

Zhang, Y., Lv, H., Du, H., Huang, C., Liu, S., Xie, G.: Modular design of QCA carry flow adders and multiplier with reduced wire crossing and number of logic gates. Int. J. Circ. Theor. Appl. 44(7), 1351–1366 (2015)

Ghosh, B., Singh, C., Salimath, A.K.: A novel approach of full adder and arithmetic logic unit design in quantum dot cellular automata. J. Low Pow. Electron. 9(4), 452–457 (2013)

Kianpour, M., Sabbaghi-Nadooshan, R.: A conventional design and simulation for CLB implementation of an FPGA quantum-dot cellular automata. Microprocess. Microsyst. 38(8), 1046–1062 (2014)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997)

Wang, W., Walus, K., and Jullien, G. A.: “Quantum-dot cellular automata adders,” in Nanotechnology, 2003. IEEE-NANO 2003. 2003 Third IEEE Conference on, 2003, 1, 461–464: IEEE

Angizi, S., Alkaldy, E., Bagherzadeh, N., Navi, K.: Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J. Low Pow. Electron. 10(2), 259–271 (2014)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik-Int. J. Light Electron Optics 158, 243–256 (2017)

Zhang, R., Walus, K., Wang, W., Jullien, G.A.: A method of majority logic reduction for quantum cellular automata. IEEE Trans. Nanotechnol. 3(4), 443–450 (2004)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014)

Akeela, R., Wagh, M.D.: A five-input majority gate in quantum-dot cellular automata. NSTI Nanotech 2, 978–981 (2011)

Angizi, S., Sarmadi, S., Sayedsalehi, S., Navi, K.: Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron. J. 46(1), 43–51 (2015)

Hashemi, S., Tehrani, M., Navi, K.: An efficient quantum-dot cellular automata full-adder. Sci. Res. Essays 7(2), 177–189 (2012)

Kumari, A., Bhanja, S.: Landauer clocking for magnetic cellular automata MCA arrays. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(4), 714–717 (2011)

Lent, C.S., Liu, M., Lu, Y.: Bennett clocking of quantum-dot cellular automata and the limits to binary logic scaling. Nanotechnology 17(16), 4240 (2006)

Sayedsalehi, S., Moaiyeri, M.H., Navi, K.: Novel efficient adder circuits for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 8(9), 1769–1775 (2011)

Navi, K., Roohi, A., Sayedsalehi, S.: Designing reconfigurable quantum-dot cellular automata logic circuits. J. Comput. Theor. Nanosci. 10(5), 1137–1146 (2013)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Sarmadi, S., Sayedsalehi, S., Fartash, M., Angizi, S.: A structured ultra-dense QCA one-bit full-adder cell. Quant. Matt. 5(1), 118–123 (2016)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik 158, 243–256 (2018)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

Heikalabad, S.R., Asfestani, M.N., Hosseinzadeh, M.: A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput. 74(5), 1994–2005 (2018)

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik 127(20), 8576–8591 (2016)

Navi, K., Farazkish, R., Sayedsalehi, S., Azghadi, M.R.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010)

Cho, H., Swartzlander, E.E., Jr.: Adder and multiplier design in quantum-dot cellular automata. IEEE Trans. Comput. 58(6), 721–727 (2009)

Mohammadyan, S., Angizi, S., Navi, K.: New fully single layer QCA full-adder cell based on feedback model. Int. J. High Perform. Syst. Archit. 5(4), 202–208 (2015)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Seyedi, S., Navimipour, N.J. Designing a three-level full-adder based on nano-scale quantum dot cellular automata. Photon Netw Commun 42, 184–193 (2021). https://doi.org/10.1007/s11107-021-00949-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11107-021-00949-5