Abstract

Ti/p-Si Schottky barrier diodes (SBDs) have been prepared by metal evaporating method. The effect of low annealing temperature on electrical parameters such as series resistance (Rs), ideality factor (n) and barrier height (Φb) of Ti/p-Si Schottky diodes was investigated with the help of current–voltage (I–V) and capacitance–voltage (C–V) characteristics. Schottky diodes have been annealed at temperatures from 50 to 200 °C for 1 min in N2 atmosphere. Φb, Rs and n were determined using Cheung and Norde functions in current–voltage characteristics. The Schottky barrier height of the as-deposited contact is found to be 0.747 eV (I–V), 1.038 eV (C–V), 0.622 eV [H(I)–I] and 0.786 eV [F(V)–V] and ideality factor as 1.3 (I–V) and 3.55 [dV/d(lnI)–I]. It has been seen that the barrier height, ideality factor and series resistance have changed with increasing annealing temperature up to 200 °C.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Schottky diodes, which are used in many applications in semiconductor technology, have been the focus of extensive theoretical and experimental studies in recently. The thermal stability and repeatability of Schottky contacts properties and formation of a quality Schottky barrier are fundamental conditions for the development of many advanced devices [1,2,3,4,5,6,7]. Schottky barrier height controls the current flow through metal–semiconductor (MS) interfaces and is significant to the efficient operation of each semiconductor device. Therefore, any mechanism affecting the Schottky diode will also affect the performance of the devices with which it is located.

Electronic characteristics of Schottky diodes such as barrier height, series resistance and ideality factor are investigated to examine the performance of Schottky contacts. The effects of factors such as annealing [8,9,10,11,12,13], radiation [14], temperature [7, 15,16,17] and pressure [5, 18, 19] on diode parameters are investigated. At the same time, in order to examine the performance of Schottky diodes, an interface layer between semiconductor and metal was formed and diode parameters are examined [20,21,22,23,24]. Many researchers have used variety metals to form Schottky contacts to p-type Si, e.g., Mn [5], Cu [6], Ni [7], PtSi [17], Zr [25], Ti [26], Al [27], Ag [28], Sn [29]. Wang et al. [8] investigated the thermal annealing properties of Gr/Si Schottky diode. They found that the values of diode parameters such as barrier height, ideality factor and series resistance decreased after annealing. Five days after annealing, they examined the I–V characteristic again and compared it with the results before and after annealing and found that the diode parameters increased [8].

Mo/SiC Schottky contact fabricated by facing targets sputtering system was thermally annealed at a temperature range of 300–400 °C for 10–30 min [30]. Electrical parameters of Mo/SiC Schottky diode were found from forward current–voltage characteristic curve using Cheung and Norde functions. Increase in the ideality factor with annealing temperature and time, but a slight decrease in SBH was reported by Hong et al. [30]. They found that there is a series resistance in proportion to annealing temperature and time, a decrease in the values calculated from the Cheung method but an increase in the values calculated from the Norde method [30]. Yıldırım et al. [31] annealed the Ni/GaAs Schottky contact at 600 °C and 700 °C and examined the temperature-dependent current–voltage properties. They found that as the annealing temperature increased, the barrier height values first increased and then decreased. But they calculated that the ideality factor increased with the increase in annealing temperature [31]. In another study on annealing, the effects of annealing time and temperature on the electrical properties and material quality of diodes were investigated [32]. From the I–V properties, they found a better ideality factor and less leakage current in reverse bias that when the annealing temperature rises up to 500 °C for a duration of 30 min [32].

The electrical properties of Schottky barrier diodes that change with the effect of annealing are of great attention for scientifically and technologically [13]. Only a few studies focused on analysis of the thermal stability properties of SBD, which is complementary and important to their electrical performance [8,9,10,11,12,13]. For this reason, it is essential to study SBD thermal stability behavior to achieve Si-based SBD for a variety of electronic applications.

In this paper, the electrical properties of Ti/p-Si Schottky contacts have been examined for the effects of low annealing temperatures using I–V (current–voltage) and C–V (capacitance–voltage) characteristics. The effect of thermal annealing dependency of main parameters obtained by different methods was investigated.

2 Experimental details

In this work, a p-Si semiconductor with the (100) orientation and polished on one side was used. The RCA cleaning procedure [3, 17] was used to clean the Si semiconductor. Then, the semiconductor is immediately placed inside the deposition chamber. Ohmic contacts are produced by evaporation of Al on the back of the substrate when vacuum was decreased by 10–5 Torr. The ohmic contact thickness formed on the semiconductor is approximately 1500 Å. A low resistance ohmic contact was formed by a temperature treatment at 570 °C for 3 min in N2 flowing in the next process. The Schottky diodes were produced by evaporation of Ti dots with diameter of about 1 mm and a thickness of about 1500 Å. Ti/p-Si diode has been annealed at temperatures from 50 to 200 °C for 1 min in N2 atmosphere. The current–voltage (I–V) and capacitance–voltage (C–V) characteristics of Ti/p-Si/Al Schottky diode were obtained by using a Keithley 487 picoammeter/voltage source and HP model 4192A LF impedance analyzer at room temperature.

3 Results and discussion

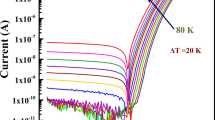

The I–V plots of Ti/p-Si Schottky diodes are shown in Fig. 1. All the forward bias and reverse bias I–V graphs of the Ti/p-Si Schottky diodes with 50 °C steps in the 0–200 °C annealing temperature range are shown in the same graph (Fig. 1). I–V plots were investigated accordingly TE (thermionic emission) theory and current is determined by relationship [33]

Here, n is the ideality factor, V is the applied voltage, k is the Boltzmann constant, T is the temperature in Kelvin, q is the electronic charge and I0 is the saturation current and is given by

where A is diode area (7.85 × 10–3 cm2), A* is the Richardson constant (p-type Si = 32 A/cm2 K2 [7]), Φb is BH (barrier height) and is defined:

n can be defined as:

\({\Phi }_{b}\) and n values of the Ti/p-Si Schottky diode were determined using Eqs. (3) and (4), respectively. The experimental values of \({\Phi }_{b}\) and n for unannealed sample were obtained to be 0.747 eV and 1.3 from Fig. 1, respectively. If the ideality factor n > 1, it expresses the deviation from the ideal diode. The higher values of the ideality factor can be assumed to be caused by the effects of the interface states, series resistance, and the interfacial thin natural oxide layer and the barrier inhomogeneities at metal–semiconductor interface [3, 29, 34]. Also, the image-force effect, tunneling and recombination–generation may be possible mechanisms that could lead to an ideality factor value greater than unity [5, 25]. Shahryari et al. [35], by examining the I–V properties of Ti/p-Si diode, found the values of n, \({\Phi }_{b}\) and Rs at room temperature. They calculated n, \({\Phi }_{b}\) and Rs values as 2.88 and 2.07 [dV/d(lnI)–I, I–V], 0.91 eV, 0.86 eV and 0.89 eV [F(V)–V, I–V, H(I)–I), 19.22 kΩ, 32 kΩ and 30 kΩ (F(V)–V, H(I)–I, dV/d(lnI)–I], respectively. They defined the total series resistance as the substrate resistance, the resistance of the metal contact layers (Ti and Al) and the natural oxide layer, which is the sum of both superficial and interfacial layers [35].

Ti/p-Si Schottky diode annealed in the annealing temperature range 50–200 °C in steps of 50 °C. The experimental values of the barrier height and ideality factor obtained I–V measurements for the Ti/p-Si Schottky diodes change from 0.660 eV and 1.25 (at 50 °C) to 0.560 eV and 2.25 (at 200 °C), respectively. The calculated values of the barrier height (\({\Phi }_{b}\)) and ideality factor (n) are given in Table 1. The barrier height and ideality factor versus annealing temperature graphs for the Ti/p-Si Schottky diodes are demonstrated in Fig. 2. There is a decrease in \({\Phi }_{b}\) values after thermal annealing. In the studies in the literature, it was found that the barrier height decreased due to the increasing annealing temperature [15, 36, 37]. Aboelfotoh [15] examined the Ti/p-Si Schottky diode depending on annealing and temperature and calculated the ideality factor and barrier height by annealing at 673 K (400 °C), 773 K (500 °C) and 873 K (600 °C). For the unannealed and annealed at 873 K, the ideality factors were 1.13 and 1.09 and the barrier height values were 0.623 eV and 0.504 eV, respectively (at a temperature of 295 K). It was found that the barrier height decreases with increasing annealing temperature [15]. The reduction in BH may be due to the thermal generation of carriers on the semiconductor side [38]. Thermally produced carriers increase with increasing annealing temperature and neutralize immobile charges on the semiconductor side. Therefore, as the annealing temperature increases, the barrier height decreases. In the ideality factor calculated from the I–V characteristic, first decrease and then an increase were observed with the increase in the annealing temperature. \({\Phi }_{b}\) (barrier height) calculated from the I–V characteristic decreased with the increase in the annealing temperature. Similarly, Padma et al. [39] found that with increasing annealing temperature, n first decreased and then increased. Co/n-GaN SBD was investigated for the electrical properties at different annealing temperatures (400 °C and 600 °C) by Orak et al. [34]. They calculated that n and \({\Phi }_{b}\) first decreases and then increases with the effect of annealing. They found that Rs decreased with increasing annealing temperature [34].

Methods for extracting information for n, \({\Phi }_{b}\) and Rs values of Schottky diodes were proposed by Cheung and Cheung [40] and Norde [41]. The Schottky diode parameters were calculated using functions of Cheung and Cheung [40]. Cheung’s functions can be explained as follows:

Experimental graphs of dV/d(lnI) vs I and H(I) vs I for Ti/p-Si Schottky diode at distinct annealing temperatures are given in Figs. 3 and 4, respectively. Equation (5) gives a flat line for the data of nonlinear part of the semi-log forward bias I–V characteristics. Hence, the y-axis intercepts and slope of the plots of dV/d(lnI) vs I will yield Rs and n, respectively. The values of Rs and n from the dV/d(lnI) vs I graphs are determined to be 141.13 Ω and 3.55 for unannealed, 379.64 Ω and 4.35 for 50 °C, 556.761 Ω and 3.95 for 100 °C, 655.09 Ω and 3.36 for 150 °C, 676.82 Ω and 3.63 for 200 °C, respectively. As seen in Fig. 4, a graph of H (I) versus I was plotted and the resulting graph is in the form of a straight line. The plot's fit equation is found (Eq. 7) and the Rs value is calculated from the slope of the equation, and using the value of ideality factor found from Eq. (5), the n \({\Phi }_{b}\) value is calculated from the point where the y-axis intercept. The estimated values of Rs and \({\Phi }_{b}\) from the graph of H(I) vs I are determined to be 152.83 Ω and 0.622 eV for unannealed, 389.13 Ω and 0.612 eV for 50 °C, 574.10 Ω and 0.597 eV for 100 °C, 669.24 Ω and 0.587 eV for 150 °C, 687.54 Ω and 0.576 eV for 200 °C. The series resistance values calculated from dV/d(lnI) vs I and H(I) vs I graphs increased with increasing annealing temperature. This increase in series resistance is attributed to that electrical compensation of the substrate dopants [40] or many kinetic processes can occur by annealing at the MS interface [42]. Defect generation, defect annealing, interdiffusion, contamination, compound formation, chemical reaction, interface roughening, etc. can form at surface layer of the semiconductor substrate or at MS interface during annealing [42].

The ideality factors obtained from the ln I–V graphs and the dV/d(lnI)−I graphs are very different from each other. n is determined from the linear regions and from the downward curvature region of the forward bias current–voltage plots of the same characteristics. There is the large difference between n values calculated from dV/d(lnI)–I curve and ln I–V curve. This difference can be attributed to interface states, to existence of series resistance and the voltage drop across the interface layer [3, 39, 40].

Norde method [41] is used to find the values of \({\Phi }_{b}\) and Rs from forward bias I–V measurements. Norde functions:

I(V) is current values obtained from the I–V curve, where γ is considered to be the first integer greater than ideality factor n. A graph of F(V) vs V for the Ti/p-Si Schottky contact at different annealing temperatures is shown in Fig. 5. From the plot of F(V) versus V, \({\Phi }_{b}\) value of Schottky diode can be identified as follows

Moreover, Rs (series resistance) of a Schottky contact is determined using Norde functions,

The values of Imin and Vmin are the current and voltage values at the minimum point [F (Vmin)] of the F(V) graph. From the F(V)–V plot, values of Rs and \({\Phi }_{b}\) are determined as 3232.7 Ω and 0.786 eV for unannealed, 3037.7 Ω and 0.773 eV for 50 °C, 1874.7 Ω and 0.745 eV for 100 °C, 1205.8 Ω and 0.702 eV for 150 °C, 1012.5 Ω and 0.630 eV for 200 °C, respectively.

Rs and \({\Phi }_{b}\) calculated from Norde functions and Cheung’s functions do not match with each other. Since these methods are applied to different parts of the forward bias I–V plot, the values found are different. Norde functions are valid to the entire forward bias I–V plot of the junctions, whereas Cheung’s functions apply only to the nonlinear part of the forward bias I–V properties, namely the high voltage region.

For further study of the contact parameters, C–V characteristics of Ti/p-Si Schottky diodes are measured as a function of annealing temperature and the bias-dependent capacitance was analyzed at a fixed of 500 kHz. C–V plots of Ti/p-Si diode measured of different annealing temperatures are shown in Fig. 6. Figure 7 indicates a graph of 1/C2 as a function of reverse bias voltage at the different annealing temperatures. The depletion layer capacitance is determined by,

where NA is the carrier concentration, A is the diode area, εs is the dielectric constant equal to 11.7 for p-Si [43], q is the electron charge, \({\upvarepsilon }_{0}=8.85\times {10}^{-14}\) F/cm, V is the reverse voltage, Vd determined by extrapolation of the C−2–V graph to the V-axis, is the diffusion potential. BH is given by

Here, Nv is the state density in the valance band (for Si, \({N}_{V}=1.04\times {10}^{19}\) cm−3) [2, 44]. The carrier concentration of Si has been determined to be 3.36 × 1017, 3.66 × 1017, 3.52 × 1017, 3.55 × 1017 and 3.34 × 1017 cm−3 at for unannealed, 50, 100, 150, 200 °C, respectively. The obtained \({\Phi }_{b}\) of Ti/p-Si Schottky diodes for unannealed and samples annealed at 50, 100, 150 and 200 °C is 1.038, 1.166, 1.237, 1.567 and 1.6 eV, respectively.

Figures 6 and 7 show capacitance–voltage and C−2–V graphs of the Ti/p-Si Schottky diode, respectively. With increasing annealing temperature, there has been a decrease in the capacitance values and this decrease can be observed in the forward bias region of the graphs (Fig. 6). These peaks are attributed to the distribution of deep states in the gap or to the series resistance and interface [3, 25]. The depletion region capacitance is difficult to measure as the diode is conducting under forward bias. However, the capacitance can be easily measured as a function of the reverse bias. The values of parameters such as \({\Phi }_{b}\), Ef, Na and Vd, were found from the reverse bias C−2–V plot. These parameters calculated from C−2–V plot are reported in Table 2. \({\Phi }_{b}\) increased with increasing annealing temperature. In his study, Aboelfotoh [15] found that the barrier height values obtained from C–V measurements increased with the increased annealing temperature. The barrier height values at 295 K of the sample which was not annealed and annealed at 873 K was found to be 0.507 eV and 0.582 eV, respectively [15]. Çakıcı et al. [12] annealed the Schottky diode at 100 °C and 200 °C and reported that the barrier height increased depending on the annealing temperature. Reddy et al. [45] calculated the barrier height values of the Schottky diode from the C–V graph and found them as 0.68 eV, 0.74 eV, 0.89 eV, 0.70 eV and 0.82 eV for the samples that were unannealed and annealed at 200, 300, 400 and 500 °C, respectively. Rao et al. [13] annealed the Schottky diode at 200, 300 and 400 °C and calculated the barrier height values from the capacitance–voltage characteristic. They found 0.83 eV, 0.92 eV, 0.96 eV and 0.78 eV for unannealed and annealed samples at 200, 300 and 400 °C, respectively [13]. In their study, Rao et al. [13] and Reddy et al. [45]. It was reported that the barrier height increased in samples annealed up to 300 °C and there was a decrease in samples annealed after 300 °C.

For Schottky diode having interface state in equilibrium with the semiconductor, the ideality factor n becomes greater than unity, and as proposed by Card and Rhoderick, the interface state density Nss is given as [46]

where εi and εs are the permittivity of interfacial layer and semiconductor, respectively, δ is the thickness of the interfacial layer, WD is the space charge width and \(n\left(V\right)=\left[V/kT/q/ln\left(I/{I}_{0}\right)\right]\) is voltage-dependent ideality factor, respectively. The energy of interface states (Ess) with respect to the top of the valence band at the surface of the p-type semiconductor is defined by

Here, \({\Phi }_{e}\) is the effective barrier height and V is the applied voltage drop across the depletion layer. The energy distribution curves of Nss are estimated from the experimental data of forward I–V characteristics. The plot of Nss versus Ess–Ev for Ti/p-Si Schottky diode is shown in Fig. 8 at different annealing temperatures. As can be seen from Fig. 8, there is an increase in the interface state density from the mid-gap to the top of the valence band. It is clearly seen from Fig. 8, interface state density decreases with increasing annealing temperature up to 150 °C and then slightly increases upon annealing at 200 °C.

Table 1 gives the estimated electrical parameters of Ti/p-Si Schottky diode by, Norde, I–V, and Cheung methods. As can be seen from Table 1, Rs values calculated in Cheung’s functions changed with the effect of annealing, that is, the series resistance values increased. It was determined that Rs values acquired from the Norde function decrease with increasing annealing temperature. The barrier height values determined from the C–V measurements and the values determined from the I–V measurements are different from each other and \({\Phi }_{b}\) calculated from C–V is higher. The difference in the Schottky barrier height values may be attributed to the barrier inhomogeneities and the effect of the image force or an interface layer in the Schottky barrier height at MS interface [3, 29, 36, 47, 48].

4 Conclusions

The electrical properties of Ti/p-type Si SBDs were investigated using I–V and C–V characteristics as a function of annealing temperature. The values of n and \({\Phi }_{b}\) and Rs changed with increasing the annealing temperature. The measurement results showed that the ideality factor of the unannealed and annealed at 200 °C diodes is 1.3 (I–V)/3.55 [dV/d(lnI)–I] and 2.25 (I–V)/3.63 [dV/d(lnI)–I], respectively. From the measurements, barrier height in unannealed and annealed diodes was calculated to be 1.038 eV(C–V)/0.747 eV(I–V) and 1.60 eV (C–V)/0.560 eV (I–V), respectively. Barrier height values were calculated with 4 methods (C−2–V characteristics, I–V method, Cheung’s function and Norde function) and the values found can be compared with each other. Further, the energy distribution of interface state density is determined from the forward bias I–V measurements and the calculated interface state density of the Ti/p-Si SBD decreases for the contact annealed at 150 °C and then increases after annealing at 200 °C. Rs values calculated from H(I)–I and dV/d(lnI)–I plots were found to be close to each other. It was observed that the values of n before decreased and then increase with increasing the annealing temperature.

References

D.A. Neamen, Semiconductor Physics and Devices (Irwin, Boston, 1992).

S.M. Sze, Physics of Semiconductor Devices, 2nd edn. (Wiley, New York, 1981).

Ş Aydoğan, K. Çınar, H. Asıl, C. Coşkun, A. Türüt, J. Alloys Compd. 476, 913–918 (2009)

E. Ayyıldız, A. Türüt, Solid-State Electron. 43, 521–527 (1999)

S. Fiat, G. Çankaya, Mater. Sci. Semicond. Process. 15, 461–466 (2012)

A.A.M. Farag, A. Ashery, E.M.A. Ahmed, M.A. Salem, J. Alloys Compd. 495, 116–120 (2010)

R. Kumar, S. Chand, Solid State Sci. 58, 115–121 (2016)

X. Wang, Y. Wang, D. Li, L. Zou, Q. Zhang, J. Zhou, D. Liu, Z. Zhang, Solid State Commun. 201, 115–119 (2015)

F. Djeffal, H. Ferhati, A. Benhaya, A. Bendjerad, Superlattices Microstruct. 128, 382–391 (2019)

T. Yamaguchi, H. Kato, N. Fujimura, T. Ito, Thin Solid Films 396, 119–125 (2001)

E. Guo, Z. Zeng, Y. Zhang, X. Long, H. Zhou, X. Wang, Microelectron. Reliab. 62, 63–69 (2016)

T. Çakıcı, M. Sağlam, B. Güzeldir, Mater. Sci. Semicond. Process. 28, 121–126 (2014)

L.D. Rao, K.S. Latha, V.R. Reddy, C. Choi, Vacuum 119, 276–283 (2015)

S. Krishnan, G. Sanjeev, M. Pattabi, Nucl. Inst. Methods Phys. Res. B 266, 621–624 (2008)

M.O. Aboelfotoh, J. Appl. Phys. 64(8), 4046–4055 (1988)

Ç. Nuhoğlu, E. Özerden, A. Türüt, Appl. Surf. Sci. 250, 203–208 (2005)

S. Gholami, M. Khakbaz, World Acad. Sci. Eng. Technol. 57, 1001–1004 (2011)

A.F. Özdemir, S.M. Abdolahpour, A. Kökçe, N. Uçar, Acta Phys. Pol. A 132, 1118–1121 (2017)

A.F. Özdemir, T. Özsoy, Y. Kansız, M. Sancak, A. Kökçe, N. Uçar, D.A. Aldemir, Eur. Phys. J.-Appl. Phys. 60, 10101 (2012)

F.Z. Pür, A. Tataroğlu, Phys. Scr. 86, 035802 (2012)

U.A. Büyükbaş, A. Tataroğlu, K.Y. Azizian, Ş Altındal, J. Mater. Sci.: Mater. Electron. 29, 159–170 (2018)

E. Şenarslan, B. Güzeldir, M. Sağlam, J. Mater. Sci.: Mater. Electron. 28, 7582–7592 (2017)

Ç.Ş Güçlü, A.F. Özdemir, Ş Altındal, Appl. Phys. A 122, 1032 (2016)

B. Kınacı, S.Ş Çetin, A. Bengi, S. Özçelik, Mater. Sci. Semicond. Process. 15, 531–535 (2012)

D.A. Aldemir, Mod. Phys. Lett. B (2020). https://doi.org/10.1142/S0217984920500955

H. Çetin, B. Şahin, E. Ayyıldız, A. Türüt, Phys. B 364, 133–141 (2005)

M. Siada, A. Keffousb, S. Mammaa, Y. Belkacemb, H. Menarib, Appl. Surf. Sci. 236, 366–376 (2004)

A. Kumar, A. Kumar, K.K. Sharma, S. Chand, Superlattices Microstruct. 128, 373–381 (2019)

Ş Karataş, Microelectron. Eng. 87, 1935–1940 (2010)

J. Hong, K.H. Kim, K.H. Kim, Coating 388, 1–9 (2019)

N. Yıldırım, A. Türüt, H. Doğan, Surf. Rev. Lett. 25(7), 1850082 (2018)

Z. Cao, T.D. Veal, M.J. Ashwin, K. Dawson, I. Sandall, J. Appl. Phys. 126, 053103 (2019)

E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts, 2nd edn. (Clarendon Press, Oxford, 1988).

İ Orak, K. Ejderha, E. Sönmez, M. Alanyalıoğlu, A. Türüt, Mater. Res. Bull. 61, 463–468 (2014)

M. Shahryari, M.H. Shakib, M.B. Askari, S. Nanekarani, S.S. Nejad, S. Bagheri, World J. Eng. 14(4), 284–288 (2017)

H.R. Liauh, M.C. Chen, J.F. Chen, L.J. Chen, J. Appl. Phys. 74(4), 2590–2597 (1993)

N. Fujimura, T. Yamaguchi, H. Kato, T. Ito, Appl. Surf. Sci. 159–160, 186–190 (2000)

A. Manna, S. Saha, S.C. Saha, Chalcogenide Lett. 14(7), 283–289 (2017)

R. Padma, G. Nagaraju, V.R. Reddy, C.J. Choi, Thin Solid Films 598, 236–242 (2016)

S.K. Cheung, N.W. Cheung, Appl. Phys. Lett. 49, 85 (1986)

H. Norde, J. Appl. Phys. 50, 5052 (1979)

A. Türüt, Turk. J. Phys. 44, 302–347 (2020)

Ş Aydoğan, M. Sağlam, A. Türüt, Microelectron. Eng. 85, 278–283 (2008)

M.E. Aydın, Ö. Güllü, N. Yıldırım, Phys. B 403, 131–138 (2008)

M.B. Reddy, V. Janardhanam, A.A. Kumar, V.R. Reddy, P.N. Reddy, C.J. Choi, R. Jung, S. Hur, J. Mater. Sci: Mater. Electron. 21, 804–810 (2010)

H.C. Card, E.H. Rhoderick, J. Phys. D 4, 1589–1601 (1971)

V. Janardhanam, Y.K. Park, K.S. Ahn, C.J. Choi, J. Alloys Compd. 534, 37–41 (2012)

Ş Aydoğan, M. Sağlam, A. Türüt, Vacuum 77, 269–274 (2005)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Asıl Uğurlu, H., Çınar Demir, K. & Coşkun, C. The effect of thermal annealing on Ti/p-Si Schottky diodes. J Mater Sci: Mater Electron 32, 15343–15351 (2021). https://doi.org/10.1007/s10854-021-06084-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-021-06084-1