Abstract

In this study, the electrical characteristics of the prepared Au/(Cu2O–CuO–PVA)/n-Si (MPS) structures have been investigated in detail by using the frequency dependent C–V and G/ω–V measurements by taking into account the interfacial polymer layer, surface states (Nss), polarization and series resistance (Rs). The electric parameters such as the diffusion potential (VD), the concentration of donor atoms (ND), and barrier height (BH) values were obtained from C−2–V plots for each frequency and they were found as 0.33 eV, 7.60 × 1013cm−3, 0.65 eV at 10 kHz and 0.70 eV, 6.99 × 1013cm−3, 1.02 eV at 3 MHz. The energy dependent profiles of Nss and their relaxation time (τ) were found by using admittance method and they ranged from 1.09 × 1011 to 1.60 × 1011 eV−1 cm−2 and 7.75 × 10−6 to 9.93 × 10−5 s, respectively. These low values of Nss are indicated that the (Cu2O–CuO)-doped PVA interfacial layer considerably enhances the performance of the Au/n-Si (MS) structure and so it can be successfully utilized instead of the traditional insulator/dielectric layer due to its passivized the surface states. The Rs versus V plot was obtained from the C–V and G/ω–V data using Nicollian and Brews method and it shows a distinctive peak, while the magnitude of the peak decreases with increasing frequency, its position shift towards lower or negative bias voltage with decreasing frequency due to the reordering and restructuring of surface states and their relaxation time under applied bias voltage. The impedance measurements were also performed in the wide range of frequency (100 Hz–1 MHz) at room temperature. The equivalent circuit model parameters such as parallel resistor (Rp), capacitor (Cp) and a series resistance (Rs) were calculated from Cole–Cole plots. The values of Rs, Rp and Cp decrease with increases dc voltage. The decrease of Rp is because of the increasing in the number of injected charge carriers into the device.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent years, due to the technological importance of the organic/polymeric materials play an important role in electronic and optoelectronic device applications such as Schottky type diode, solar cells, light-emitting diodes, transistors, sensors and capacitors [1,2,3,4,5,6]. In order to improve the performance and reliability of metal-semiconductor (MS) type Schottky barrier diodes (SBDs), a thin polymer layer with and without metal doped are inserted between metal and semiconductor instead of traditional insulator materials such as SiO2 and SnO2. Although SiO2 is a good gate dielectric thanks to its compatibility with Si wafer, it may be unsatisfying to restrain unacceptably large leakage current and high Nss. It is believed that the use of high-dielectric interfacial layer and both its thickness and homogeneity play an important role in reviewing the performance, reliability and stability of these devices. Therefore, to perform a high quality SBDs with a thin interlayer, low ideality factor, low surface states (Nss), high or moderate BH and its homogeneity are critical parameters. In other words, this drawback can be overcome through usage of the other interlayers instead of insulator layer.

The impedance-voltage (Z*–V) measurements which are including capacitance/conductance–voltage (C/G–V) characteristics of these devices are independent of frequency, but the situation is quite different in applications due to the polarization processes, Nss, series resistance (Rs) of the device, native or deposited interfacial layer, the level of doping concentration atoms, the nature of barrier height (BH) at M/S interface. Therefore, the investigation of the forward and reverse C–V and G/ω–V characteristics of these electronic devices measured only at one frequency and voltage cannot supply enough information both on the electric and dielectric properties of these devices. For these reasons, the C–V and G/ω–V measurements of these devices in the wide range of frequency and voltage are more important study to get both the fabrication of high-performance and obtain knowledge on the conduction mechanism in these devices. Usually, metal-polymer-semiconductor (MPS) structure shows similar behavior of metal-insulator-semiconductor (MIS) type Schottky diodes. Especially, polyvinyl alcohol (PVA) has an important place among organics/polymers and it has low cost, low weight, flexible and easy fabrication processes such as electrostatic spraying, electrochemical deposition, sol–gel, dip coating, and spin coating [1,2,3,4]. PVA is also water soluble and it has a semi-crystalline polymer exhibit more important applications due to the role of OH group and hydrogen bonds [4]. On the other hand, PVA has normally poor electrical conductivity and may be conductive upon doping with some dopants such as Zn, Ni, Co, graphene, (Cu2O–CuO) due to the high physical interaction between polymer chains [5, 6].

There are many workers in the literature on the characterization of Nss and Rs [7, 8]. Among them admittance method or impedance (Y = 1/Z) method has been described and analyzed by Nicollian and Goetzberger [9] which can supply more reliable and accurate results. The existence of Nss and Rs in MIS/MOS and MPS type structures can be affected the C–V and G/ω–V characteristics. Because, at low and moderate frequency the charges at surface states/traps can easy follow the ac signal and yield an excess capacitance and conductance to real values of them. Surface states have an energy distribution within the band-gap and even extend into the conduction and valence band of the semiconductor. Conductance method can not only extract the values of Nss in both the depletion and weak inversion region, and relaxation time (τ) of them. This conductance method is based on measuring a set of Cm and Gm of the MIS or MPS type structure both as a function of frequency and bias voltage and subsequently calculating the parallel conductance (Gp/ω) by solving the small signal equivalent circuit. Parallel conductance represents the loss mechanism occurring when the surface states/traps capture and emit carriers, and is used to extract the density of Nss.

In our previous study [10], the conduction mechanisms of the fabricated Au/(Cu2O–CuO–PVA)/n-Si (MPS) structures have been investigated by using the current–voltage (I–V) characteristics in the wide range of temperature (100–380 K) and voltage (± 5 V). The forward bias I–V–T characteristics of the Au/(Cu2O–CuO–PVA)/n-Si (MPS) structures were successfully described by the double-GD of BHs with mean BHs. Therefore, in the present study, we aimed that an achieve good understand effects of Nss, Rs, (Cu2O–CuO–PVA) polymer layer and polarization. For this purpose, the forward and reverse bias C–V and G/ω–V measurements were carried out in the wide range of frequency (10 kHz–3 MHz) and voltage (± 4V) at room temperature.

2 Experimental details

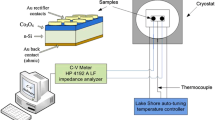

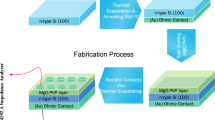

The Au/(CuO–Cu2O–PVA)/n-Si (MPS) type SBDs were fabricated on P-doped (n-Si) single crystalline Si wafer with (100) orientation, with approximately 300 μm thick and 0.2 Ohm cm resistivity. More information on the cleaning processes, structural analysis and schematic diagram of structures system can be seen in our previous study [10]. The admittance measurements in this study were carried out by using a HP 4192A LF Impedance analyzer at room temperature. The forward and reverse bias C–V and G/ω–V measurements were carried out in the wide range of frequency (10 kHz–3 MHz) and voltage (± 4 V) by 50 mV steps. In addition, the impedance measurements were performed using a Solartron SI1260 Impedance/Gain-Phase Analyzer and Solartron 1296 Dielectric Interface at room temperature.

3 Result and discussion

3.1 Frequency dependent electrical properties

The C–V and G/ω–V characteristics of the Au/(Cu2O–CuO–PVA)/n-Si (MPS) structure for various frequency at room temperature were given in Figs. 1 and 2, respectively. In order to see the effects of interfacial layer, surface states and Rs of the structure, these measurements were performed in the frequency range of 10 kHz–3 MHz at ± 4V. As can be clearly seen in Figs. 1 and 2, both the C–V and G/ω–V curves have inversion, depletion and accumulation regions like a metal–oxide–semiconductor (MOS) capacitor and they show some discrepancies especially in the depletion and accumulation regions which are routed from the surface states the existence of Nss, Rs, polarization and interfacial polymer layer. However, an interfacial polymer or insulator layer between metal and semiconductor can be easy polarized under an external electric field that displaces the charges from their equilibrium position. The life time of charges at surface states and both the interfacial layer and the formation of BH at M/S interface are also more effective on the impedance measurements. As shown in Figs. 1 and 2, both the values of C and G/ω increase with increase voltage and decrease with increased frequency both in depletion and accumulation regions. Such behavior of them in depletion region especially at low frequencies can be attributed to the existence of Nss and surface polarization, but at accumulation regions especially due to the effects of Rs and interfacial polymer layer, respectively. On the other hand, the decreases with increasing frequency of them especially in the depletion region is the result of the interface states cannot follow the a.c. signal at higher frequency and so that they cannot yield any contribution or excess values of the measurements of them [11,12,13,14].

existence of Rs can also cause a serious error in the extraction of the electrical parameters. While the Nss are more effective at low frequency, but Rs is effective at high frequency. To avoid from this error and the sensitivity limitation, Rs can be minimized by (a) the fabrication process of the sample (b) performing these measurements at low frequency and (c) measuring Rs and applying a correction/adjustment. According to the Nicollian and Brews [7] method, the real value of Rs can be calculated from the measurements of the Cma and Gma values at strong accumulation region at enough high frequencies (f\(\hspace{0.17em}\ge\) 500 kHz). However, the voltage dependence profile of Rs can be also extracted from the measured any Cm and Gm for each frequency and voltage. Therefore, the Rs versus V plot was obtained by using the fallowing equation formalized by Nicollian and Brews [7].

Thus, Rs versus V plot for each frequency was given in Fig. 3. It is clear that the value of Rs at strong accumulation region at high frequencies become almost constant or independent from voltage and so this value is corresponding to the real value of Rs, but it becomes increases with decreasing frequency at low frequencies due to the effects of Rs and surface polarization. On the other hand the Rs versus V plot has one distinctive peak especially at low frequencies. While the magnitude of the peak decreases with increasing frequency, its position shift towards lower or negative bias voltage with decreasing frequency. Such behavior of it with frequency is the result of reordering and restructuring of surface states under electric field [13,14,15].

In order to extract some main parameters of the Au/(Cu2O–CuO)–PVA/n-Si (MPS) structure such as diffusion potential (VD), doping concentration atoms (ND) and barrier height [ΦB(C−V)], the reverse bias C−2 versus V plot was drawn for the whole measured frequency range and is given in Fig. 4. In MIS/MOS and MPS structures, the depletion layer capacitance per unit area can be expressed as [8]:

In Eq. 2, εs is the dielectric constant of the semiconductor (11.9 for Si), A is the area of rectifier contact and other quantities are well known in the literature. The values of VD (= Vo + kT/q) and ND are usually calculated the intercept and slope of the linear part C−2 versus V plot, respectively. In this way, the value of ΦB (C−V) is calculated by the following equations [8].

With

Here, Em is the maximum electric field, Nc is the density of states at the conduction-band and EF is the energy different between the bulk Fermi level and valance band edge and ΔΦB is the image force barrier lowering. The calculated experimental values of VD, ND and ΦB(C−V) for various frequencies at room temperature are tabulated in Table 1. As can be seen from Table 1, the values of VD, ND and ΦB(C−V) are found as 0.33 eV, 7.60 × 1013cm−3, 0.65 eV at 10 kHz and 0.70 eV, 6.99 × 1013cm−3, 1.02 eV at 3 MHz. It is clear that all of these electric parameters are a strong function of frequency. As shown in Fig. 5, while the value of ΦB(C−V) increases almost as exponentially, ND decreases. Such behavior of ΦB(C−V) and ND with frequency is the effects of Nss and polarization [16,17,18].

The obtained experimental high values of ND and Rs at low frequencies can be attributed to the existence of surface states and dislocation located between interfacial layer and semiconductor. While the contribution of C and G by surface states is very important especially at low frequencies, the value of Rs becomes very effective at high frequency at accumulation region (Fig. 6). As shown in Fig. 6, the value of Rs decreases with the increasing applied bias voltage for each frequency. As the frequency is increased further, the value of Rs remains almost constant such that this value at strong accumulation region corresponds to the real value of Rs. Therefore, both the existence of the interfacial layer native or deposited, Nss and Rs must be taken into account in the calculations [14,15,16,17,18,19].

3.2 The extraction of energy dependent profile of surface states

There are many studies have suggested different ways of the characterization of surfaces states/traps (Nss) [7,8,9]. Among them the one of the most useful methods to determine of them is the conductance method. This method is defined by Nicollian and Brews and they have observed that the values of C and G/ω decreased with increasing frequency, especially at low and moderate frequencies. According to this method, the value of parallel conductance can be expressed as [8]:

In Eq. 6, τ is the life time or relaxation time of the surface states and Cox is the interfacial layer capacitance. The Gp/ω versus Inf plots were calculated from the use of Cm and Gm values in the wide range of applied bias voltage (1–4 V) at room temperature. Firstly, both the Cm and Gm/ω versus Inf plots were drawn and given in Figs. 7 and 8, respectively. As shown Figs. 7 and 8, both Cm and Gm/ω values increase with increasing voltage but decrease with increasing frequencies as almost exponentially and then they remain almost constant at high frequencies [20,21,22,23,24,25].

It is clear that, the changes in the C and G is considerably high in the depletion region when compared accumulation region. In other words, while Nss are effective especially in the depletion region at low and moderate frequencies, Rs becomes effective only at accumulation region at high frequencies. The higher values of C and G/ω at low frequency are due to the excess capacitance and conductance (Cex and Gex/ω) steam from the Nss which are equilibrium with the semiconductor (di ≥ 30 Å) and they can easy follow the ac signal. Similar results have been reported by Tecimer et al. and Şafak et al. [19, 26, 27]. Figure 9 shows the curves of parallel conductance (Gp/ω) versus Inf of the Au/(Cu2O–CuO–PVA)/n-Si (MPS) structure at various forward bias voltages. As can be seen in Fig. 9, for each forward bias voltage the Gp/ω versus Inf plot gives a peak and this peak value shifts towards to the accumulation or high forward bias increase with increasing applied bias voltage. Such peak behavior of Gp/ω can be attributed to the existence of Nss and their restructure and reordering under applied bias voltage [9, 25, 26]. The magnitude of peak is dependent on the capture rate, i.e. on the Nss level occupancy and life time of them. At the peak value of Gp/ω, ωτ is corresponding to 1.98 and substituting this value in Eq. (6), one obtains \({N_{SS}}=\frac{{{{\left( {{G_p}/\omega } \right)}_{\hbox{max} }}}}{{0.402qA}}\) and life time τ = 1.98/ωp, where ωp is the frequency at the (Gp/ω)max.

The energy distribution of Nss and their relaxation time (τ) are indicated in Fig. 10. As can be seen from Fig. 10, the values of Nss and their relaxation time (τ) ranged from 1.09 × 1011 to 1.60 × 1011 eV−1 cm−2 and 7.75 × 10−6 to 9.93 × 10−5 s, respectively. Such dispersion in the C–V and G/ω–V characteristics as function of frequency and voltage have been also reported in the literature [28,29,30,31] due to the existence of Nss, Rs, and interfacial layer. It is clear that, the obtained values of Nss which are order 1011 eV−1 cm−2 are more suitable for an electronics device. These values of Nss are indicated that the (Cu2O–CuO)-doped PVA interfacial layer considerably enhances the performance of the Au/n-Si (MS) structure. Therefore, (Cu2O–CuO)-doped PVA polymer interfacial layer can be successfully used instead of the traditional insulator/dielectric layer due to its passivized the surface states.

3.3 Impedance properties

The impedance spectroscopy (IS) is a technique used to understand the alternating current (ac) behavior of dielectric materials and electronic devices. This technique enables us to measure the response of the material to a small amplitude excitation over a wide range of frequency. A device with dielectric material can be represented by a parallel RC circuit. The impedance (Z) of RC circuit is expressed by,

where Y, R and C are the admittance, resistance and capacitance of device, respectively. The RC circuit can be modeled by an equivalent circuit, as shown in Fig. 11. The equivalent circuit can be considered as a single parallel resistor Rp and capacitor Cp network with a series resistance Rs.

Generally, the complex impedance of the equivalent circuit can be given by the following equation [32,33,34,35,36,37,38],

where Z′ and Z″ are the real part and imaginary parts of the complex impedance, and ω(= 2πf) is the angular frequency of the ac excitation. Z′ and Z″ are given by,

By removing the angular frequency from the equations, the semicircle is associated with the real and imaginary parts of the complex impedance. In other words, the semicircle of the Cole–Cole plot can be defined by the following equation,

This equation defines a circle centered at (Rs+Rp/2,0) with radius Rp/2.

The impedance measurements were carried over wide frequency range of 100 Hz–1 MHz. Figure 12a and b show the variation of real part (ReZ or Z′) and imaginary part (ImZ or Z″) of the complex impedance with frequency at various dc bias voltages. It is observed that the ReZ and ImZ value decrease with increasing applied dc bias. As seen in Fig. 12a, the magnitude of ReZ remains constant up to a certain frequency, then decreases rapidly with increasing frequency. As seen in Fig. 12b, the ImZ plots give a peak for all bias voltages. The ImZ increases with increasing frequency and reaches a maximum peak value, then decreases with increasing frequency. Also, the position of the Z″ peak shifts to higher frequencies with increasing dc bias voltage. This observed peak confirms the single relaxation process in the system. At this case, the dielectric relaxation time τ (= 1/ωmax) can be determined from the position of the peak. When the bias voltage is increased and consequently the parallel resistance Rp decreases, the relaxation time decreases with increasing dc voltage. This decrease of relaxation time is attributed to the injection of charge carriers into the device [37, 38].

Figure 13 shows the Cole–Cole plots at various bias voltages. As seen in Fig. 13, these plots indicate a single semicircle for all dc bias voltages. Moreover, it is observed that the size and radius of these semicircles decrease with increasing applied dc bias. A single semicircle suggests the equivalent electrical circuit, shown in Fig. 11. In other words, the device can be modeled by an equivalent circuit which consists of the parallel resistance (Rp) and the capacitance (Cp) network in series with a series resistance (Rs) [38,39,40].

The minimum ReZ value represents Rs, and the maximum ReZ value corresponds to the summation of Rs and Rp to the capacitance Cp [9]. The Rs is caused by the electrode contact. The fitting parameters of impedance data of the device by provided the equivalent electrical circuit at various bias voltages are given in Table 2. As seen in Table 2, Rs, Rp and Cp value decrease as the dc bias voltage increases. The decrease of Rp is because of the increasing in the number of injected charge carriers into the device [37,38,39,40,41].

As a result both the value of Nss and Rs are more effective on the C–V and G–V characteristics. On the other hand, while the value of Nss has an effect in the depletion and inversion regions at low frequencies, Rs has an effect on the accumulation region at high frequencies. Usually, during the fabrication of semiconductor devices such as metal–semiconductor (MS) structures with and without an interfacial insulator or polymer layer (MIS or MPS), many defects/dislocations can be occurred and which lead to electronic states with energies located in the forbidden band gap of the semiconductor between interfacial layer and semiconductor interface. These states are known as surface states or traps (Nss or Dit) and alter the performance of these devices. Usually they can be originated from defects such as dangling bounds between interfacial layer and semiconductor with energy states in the semiconductor band gap (Eg) and dependent on the chemical composition of the interface [23,24,25,26,27,28,29,30,31, 42,43,44,45]. These electronic states can be stored and released charges when an appropriate dc and external ac signal is applied on the sample. These states can be arise from four different sources: (1) interface trapped charges which are located at interfacial layer/semiconductor ; (2) fixed oxide charges which are located at or near the interface ; (3) oxide trapped charges which can be created by high energetic radiation and (4) mobile ionic charges such as sodium ions [9, 10]. The changes in the values of C and G/ω with applied biases are especially dependent on the ability of these states to follow the ac signal and their relaxation time (τ). The value of Rs has an effect both on the electric and dielectric properties of electronic devices as well as surface states. Usually it can originate from various sources such as the back ohmic and front rectifier contacts, the probe wire to the gate or rectifier contact, the bulk resistance of the semiconductor, a dirty film or particulate matter at back contact interface and extremely non-uniform doped atoms in the semiconductor [7, 9]. The value of Rs can be reduced either by having a low BH between metal and semiconductor and using heavy doped semiconductors (≥ 1017 cm−3) or by the use of a good cleaning and fabrication process.

4 Conclusion

In this study, Au/(Cu2O–CuO)–PVA/n-Si (MPS) structures were fabricated and their electrical characteristics and energy dependent profiles of Nss and τ have been characterized using frequency dependent C–V and G/ω–V measurements. Both the values of C and G/ω show a large dispersion in the depletion region due to a special distribution of Nss and their life time. On the other hand these dispersions at accumulation region due to the existence of Rs and interfacial (Cu2O–CuO)–PVA polymer layer. While the polarization and surface states are effective at low frequencies, Rs is effective only at enough high frequency (f ≥ 500 kHz). Some main electrical parameters such as VD, ND and ΦB(C−V) were found from the reverse bias C−2 versus V plot as 0.33 eV, 7.60 × 1013 cm−3, 0.65 eV at 10 kHz and 0.70 eV, 6.99 × 1013 cm−3, 1.02 eV at 3 MHz. While the value of ΦB(C−V) increases almost as exponentially, ND decreases. Such behavior of ΦB(C−V) and ND with frequency is the effects of Nss and polarization. In addition, the Rs versus V plot was obtained from the C–V and G/ω–V data using Nicollian and Brews method and it has one distinctive peak at low frequencies. While the magnitude of the peak decreases with increasing frequency, its position shift towards lower or negative bias voltage with decreasing frequency due to the reordering and restructuring of surface states and their relaxation time under applied bias voltage. The energy dependent profile of Nss and their relaxation time (τ) were found by using admittance method and they ranged from 1.09 × 1011 to 1.60 × 1011 eV−1 cm−2 and 7.75 × 10−6 s to 9.93 × 10−5 s, respectively. The obtained values of Nss which are order 1011 eV−1 cm−2 are more suitable for an electronics device. These low values of Nss are indicated that the (Cu2O–CuO)–doped PVA interfacial layer considerably enhances the performance of the Au/n-Si (MS) structure. Therefore, (Cu2O–CuO)-doped PVA polymer interfacial layer can be successfully used instead of the traditional insulator/dielectric layer due to its passivized the surface states. The impedance measurements were also performed in the wide range of frequency (100 Hz–1 MHz) at room temperature. The equivalent circuit model parameters such as parallel resistor (Rp), capacitor (Cp) and a series resistance (Rs) were calculated from Cole–Cole plots. Experimental results show that the Rs, Rp and Cp value decrease as the dc bias voltage increases. The decrease of Rp is because of the increasing in the number of injected charge carriers into the device.

References

Y. Nikravan, Ş Badali, İ Altındal, İ Uslu, Orak, On the frequency and voltage-dependent profiles of the surface states and series resistance of Au/ZnO/n-Si structures in a wide range of frequency and voltage. J. Electron. Mater. 46, (5728–5736) (2017)

S. Demirezen, A. Kaya, Ş Altındal, İ Uslu, The energy density distribution profile of interface traps and their relaxation times and capture cross sections of Au/GO-doped PrBaCoO nanoceramic/n-Si capacitors at room temperature Polym. Bull. 74, 3765–3781 (2017)

J. Kwon, Development of a new conjugated polymer containing dialkoxynaphthalene for efficient polymer solar cells and organic thin film transistors. J. Polym. Sci. A. 49, 1119–1128 (2011)

N.M. Shash, H. Khoder, F. Metawe, A.A. Negm, Structure, electrical, dielectric, and optical investigation on polyvinyl alcohol/metal chloride nanocomposites. J. Appl. Polym. Sci. 129, 2796–2805 (2013)

V. Tamilavan, P. Sakthievel, Y. Li, M. Song, C.H. Kim, S.H. Jin, M.H. Hyun, Synthesis and characterization of indenofluorene-based copolymers containing 2,5-bis (2-thienyl)-N-arylpyrrole for bulk heterojunction solar cells and polymer light-emitting diodes’. J. Polym. Sci. A. 48, 3169–3177 (2010)

G. Ersöz, İ Yücedağ, Y. Azizian-Kalandaragh, İ. Orak, Ş. Altındal, Investigation of electrical characteristics in Al/CdS-PVA/p-Si (MPS) structures using impedance spectroscopy method. IEEE Trans. Electron Dev. 63, 2948–2955 (2016)

E.H. Nicollian, J.R. Brews, MOS (Metal Oxide Semiconductor Physics and Technology (Wiley, New York, 1982)

S.M. Sze, Physics of Semiconductor Devices, 2nd edn. (Wiley, New York, 1981)

E.H. Nicollian, A. Goetzberger, MOS conductance technique for measuring surface state parameters. Appl. Phys. Lett. 7, 216 (1965)

A. Buyukbas Ulusan, A. Tataroğlu, Y. Azizian-Kalandaragh, Ş Altındal, On the conduction mechanisms of Au/(Cu2O–CuO–PVA)/n-Si (MPS) Schottky barrier diodes (SBDs) using current–voltage–temperature (I-V-T) characteristics. J Mater Sci. 29, 159–170 (2018)

Ş Tataroglu, Altındal, ‘Characterization of current-voltage (I-V) and capacitance-voltage-frequency (C-V-f) features of Al/SiO2/p-Si (MIS) Schottky diodes’. Microelectron. Eng. 83, 582–588 (2006)

Ş. Altındal, İ. Yücedağ, A. Tataroğlu, ‘Analysis of surface states and series resistance in Au/n-Si Schottky diodes with insulator layer using current–voltage and admittance-voltage characteristics. Vacuum. 84, 363–368 (2009)

S. Chatterjee, Y. Kuo, J. Lu, Thermal annealing effect on electrical properties of metal nitride gate electrodes with hafnium oxide gate dielectrics in nano-metric MOS devices. Microelectron. Eng. 85, 202–209 (2008)

M. Depas, R.L. Van Meirhaeghe, W.H. Lafere, F. Cardon, Electrical characteristics of Al/SiO2/n-Si tunnel diodes with an oxide layer grown by rapid thermal oxidation. Solid State Electron. 37, 433–441 (1994)

P. Durmuş, M. Yıldırım, Influence of interfacial layer thickness on frequency dependent dielectric properties and electrical conductivity in Al/Bi4Ti3O12/p-Si structures, JVSTA, 32, 061512 (2014)

A. Tataroğlu, R.E. Uyar, Analysis of density and time constant of interface states of MIS device by conductance method. Indian J. Pure Appl. Phys. 54, 374–378 (2016)

H. Kanbur, Ş Altındal, A. Tataroğlu, ‘The effect of interface states, excess capacitance and series resistance in the Al/SiO2/p-Si Schottky diodes. Appl. Surf. Sci. 252, 1732–1738 (2005)

A. Tataroğlu, A. Ahmed, F. Al-Ghamdi, W.A. El-Tantawy, F. Farooq, Yakuphanoğlu, Analysis of interface states of FeO-Al2O3 spinel composite film/p-Si diode by conductance technique’. Appl. Phys. A. 122, 220 (2016)

H. Tecimer, H. Uslu, Z.A. Alahmed, F. Yakuphanoglu, Ş Altındal, On the frequency and voltage dependence of admittance characteristics of Al/PTCDA/P-Si (MPS) type Schottky barrier diodes (SBDs). Compos. Part B. 57 25–30 (2014)

M.E. Aydin, F. Yakuphanoğlu, G. Öztürk, Modification of electrical properties of the Au/1,1′ dimethyl ferrocenecarboxylate/n-Si Schottky diode. Synth. Met. 160, 2186–2190 (2010)

M. Yun, S. Gangopadhyay, M. Bai, H. Taub, M. Arif, S. Guha, Interface states in polyfluorene-based metal–insulator–semiconductor devices. Org. Electronics. 8, 591–600 (2007)

M.M. Bülbül, Ş Altındal, F. Parlaktürk, A. Tataroğlu, The density of interface states and their relaxation times in Au/Bi4Ti3O12/SiO2/n-Si (MFIS) structures. Surf. Interface Anal. 43, 1561 (2011)

U. Kelberlau, R. Kassing, Theory of nonequilibrium properties of MIS capacitors including charge exchange of interface states with both bands. Solid State Electron. 22, 37–45 (1979)

M. Kuhn, A quasi-static technique for MOS C-V and surface state measurements. Solid State Electron. 13, 873 (1970)

H.M. Baran, A. Tataroglu, Determination of interface states and their time constant for Au/SnO2/n-Si (MOS) capacitors using admittance measurements. Chin. Phys. B. 22, 047303 (2013)

Ş Altındal, Y. Safak Asar, A. Kaya, Z. Sönmez, Investigation of interface states in Al/SiO2/p-Si (MIS) structures with 50 and 826 Å SiO2 interfacial layer using admittance spectroscopy method. J. Optoelectron. Adv. Mater. 14, 998–1004 (2012)

Y. Şafak, M. Soylu, F. Yakuphanoğlu, Ş. Altındal, On the energy distribution of interface states and their relaxation time profiles in Al/pentacene/p-GaAs heterojunction diode. J. Appl. Phys. 111, 034508 (2012)

S.A. Yerişkin, M. Balbaşı, İ Orak, Frequency dependent electrical characteristics and origin of anomalous capacitance–voltage (C–V) peak in Au/(graphene doped PVA)/n-Si capacitors. J. Mater. Sci. 28, 7819–7826 (2017)

A.F. Ozdemir, D.A. Aldemir, A. Kökçe, S. Altindal, Electrical properties of Al/conducting polymer (P2ClAn)/p-Si/Al contacts. Synth. Met. 159, 1427–1432 (2009)

E.E. Tanrıkulu, S. Demirezen, Ş Altındal, İ Uslu, On the anomalous peak and negative capacitance in the capacitance–voltage (C–V) plots of Al/(%7 Zn-PVA)/p-Si (MPS)Structure. J. Mater. Sci. 29, 2890–2898 (2018)

N. Baraz, İ Yücedağ, Y. Azizian-Kalandaragh, Ş Altındal, Determining electrical and dielectric parameters of dependence as function of frequencies in Al/ZnS-PVA/p-Si (MPS) structures. J Mater Sci. 28, 1315–1321 (2017)

A. Buyukbas, A. Tataroğlu, M. Balbaşı, Analysis of electrical characteristics of metal-oxide-semiconductor capacitor by impedance spectroscopy. J. Nanoelectron. Optoelectron. 9, 515–519 (2014)

V.F. Lvovich, Impedance Spectroscopy. (Wiley, New York, 2012)

J. R. Macdonald, Impedance Spectroscopy, (Wiley, New York, 1987)

F. Marai, S. Romdhane, L. Hassine, M. Majdoub, H. Bouchriha, Static and dynamic electrical investigations on AVB polymer light-emitting diode. Synth. Met. 132, 117–122 (2003)

H. Trad, A. Rouis, J. Davenas, M. Majdoub, Optical and electrical properties of bi-layers organic devices. Eur. Phys. J. Appl. Phys. 68, 10103 (2014)

L. Bi-Xin, C. Jiang-Shan, Z. Yong-Biao, M. Dong-Ge, Frequency-dependent electrical transport properties of 4,4′,4′-tri(N-carbazolyl)-triphenylamine investigated by impedance spectroscopy. Chin. Phys. Lett. 28, 057201 (2011)

M. Braik, C. Dridi, M. Ben Ali, A. Ali, M.N. Abbas, A. Errachid, Investigation of structural, optical and electrical properties of a new cobalt phthalocyanine thin films with potential applications in perchlorate sensor. Synth. Met. 209, 135–142 (2015)

G. Chauhan, R. Srivastava, P. Tyagi, A. Kumar, P.C. Srivastava, M.N. Kamalasanan, Frequency dependent electrical transport properties of 4,4′,4″-tris (N-3-methylphenyl-N-phenylamine) triphenylamine by impedance spectroscopy. Synth. Met. 160, 1422–1426 (2010)

S.K. Barik, R.N.P. Choudhary, A.K. Singh, AC Impedance Spectroscopy and Conductivity Studies of Ba0.8Sr0.2TiO3 Ceramics. Adv. Mat. Lett. 2, 419–424 (2011)

M. Ramar, S.S. Rawat, R. Srivastava, C.K. Suman, AC impedance spectroscopy studies of PtPc doped Alq3 thin film, in Recent Trends in Materials Science and Applications, (Springer, Cham, 2017), pp. 383–390

Ç Bilkan, Ş Altındal, Y. Azizian-Kalandaragh, Investigation of frequency and voltage dependence surface states and series resistance profiles using admittance measurements in Al/p-Si with Co3O4-PVA interlayer structures. Phys. B. 515, 28–33 (2017)

İ Taşçıoğlu, Ö Tüzün Özmen, H.M. Şağban, E. Yağlıoğlu, Ş Altındal, Frequency dependent electrical and dielectric properties of Au/P3HT:PCBM:F4-TCNQ/n-Si Schottky Barrier Diode. J. Electron. Mater. 46, 2379–2386 (2017)

İ Taşçıoğlu, M. Soylu, Ş Altındal, A.A. Al- Ghamdi, F. Yakuphanoğlu, Effects of interface states and series resistance on electrical properties of Al/nanostructure CdO/p-GaAs diode. J. Alloy. Compd. 541, 462–467 (2012)

H. Tecimer, S.O. Tan, Ş Altındal, Frequency-dependent admittance analysis of the Metal–Semiconductor Structure with an interlayer of Zn-doped organic polymer nanocomposites. IEEE Trans. Electron Devices. 65, 231–236 (2018)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Buyukbas-Uluşan, A., Yerişkin, S.A., Tataroğlu, A. et al. Electrical and impedance properties of MPS structure based on (Cu2O–CuO–PVA) interfacial layer. J Mater Sci: Mater Electron 29, 8234–8243 (2018). https://doi.org/10.1007/s10854-018-8830-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-018-8830-9