Abstract

Au/ZnO/n-Si device was obtained by using atomic layer deposition (ALD) technique, and it was characterized by I–V measurement in a wide temperature from 100 to 380 K with 20 K steps. XRD measurements were performed on ZnO thin film layer, and (002) and (201) peaks were seen in XRD pattern of the film. Surface morphology and cross section of the device were taken by SEM and discussed in the details. Some device parameters such as barrier height, ideality factor, series resistance were calculated by thermionic emission theory (TE), using Cheung’s and Norde’s functions. The Calculation results revealed that all device parameters strongly depended on temperature changing. In addition, interface states (N ss ) graphs were plotted and discussed according to energy levels and measurement temperatures. It can be concluded that this device can be used in various technological applications in wide range temperatures in industry.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Metal–semiconductor devices are very interesting and promise for electronic applications [1,2,3,4,5]. These devices can be used as rectifiers, inverters, photodiode and photodetectors [6,7,8,9]. Changing properties of these devices can be accomplished by inserting some kind of metal oxide or insulator layers between the metal and semiconductor [10,11,12].

The ZnO can be inserted as a metal oxide layer between the Au metal and n-type Si semiconductor for controlling of properties of this metal and semiconductor device because the ZnO metal oxide layer has high direct band gap (3.37 eV) [13, 14]. Also, the ZnO layer can be obtained low cost and low temperature deposition technique [15]. The ZnO as a semiconductor can be used in lasers, solar cells, photodetectors and varistors [16,17,18,19]. To obtain a ZnO thin film layer, it can be used chemical vapor deposition [20], spray pyrolysis [21], sol gel [22] and atomic layer deposition techniques (ALD) [23]. Among them, ALD technique has more advantageous for obtaining uniform film and definite thickness control [24, 25].

The measurement temperature of the sample is very important parameter for metal–semiconductor devices because it can affect main properties of those kinds of devices, and these devices can be used at various temperature after understanding temperature dependent features [26, 27]. When it can be checked in the literature, it can be seen many investigations on temperature-dependent electrical properties of metal–semiconductor devices. For instance, Mtangi et al. [28] investigated temperature-dependent current–voltage (I–V) characteristics of Pd/ZnO Schottky barrier diodes in 60–300 K temperature range. They showed that ZnO has different conduction mechanism in different temperatures, and has stable ideality factor and barrier height in this temperature range. Yadav et al. [7] studied high temperature-dependent electrical properties of Pd/ZnO/n-Si/Ti/Al device. They obtained ZnO layer using sol–gel spin coating technique and concluded that the saturation current and barrier height increased with the temperature increment. Khare et al. [29] researched the temperature-dependent current–voltage (I–V) characteristics of ZnO/P3HT:PCBM junctions. ZnO layer were obtained atmospheric pressure spatial ALD and electrodeposition techniques. In this junctions barrier height decreased and ideality factor increased with increasing temperature. They emphasized that the samples need to be thermally annealed for higher photoresponse properties of the junctions in their study. These are three different studies, but there is no any investigations about the temperature-dependent I–V characteristics of Au/ZnO/n-Si devices in the literature. This is important for better understanding of ZnO role in the interface of the metal–semiconductor devices.

In this context, the aim of this study is to investigate the temperature-dependent I–V characteristics of the Au/ZnO/n-Si device for technological applications in the wide range temperatures from 100 to 380 K with 20 K steps.

2 Materials and methods

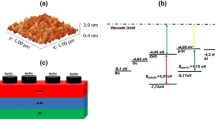

n-Type Si substrate, which has (100) orientation, was used for producing Au/ZnO/n-Si device. Firstly, Si wafer was cut into 1 cm2 pieces (square shape), and they were cleaned and etched with various solvents and acids (H2SO4:H2O2:H2O (5:1:1) for 1 min). Secondly, high purity gold was evaporated thermally back side of the Si wafers for ohmic contact, and then wafers were annealed in N2 atmosphere at 450 °C for 3 min. Thirdly, ZnO layer was deposited on front side of Si wafers for 10 nm ZnO layer with 1.45 Å growth rate at per cycle by ALD technique which had 5 × 10−3 Torr vacuum, 180 °C temperature and zinc acetate and water sources. Fourthly, Au metal was doped on the ZnO surface as metallic contacts using a mask with 1.0 mm diameter holes on the device. Shematic diagram of the device has been shown in Fig. 1. The ZnO film layer in the device was characterized with Bruker D8 Discover XRD. SEM images were obtained ZEISS Sigma 300. The I–V measurements of the device were obtained by using a homemade liquid nitrogen cryostat equipped with a temperature controller in darkness in the range of 100–380 K temperatures with 20 K steps at 500 kHz frequency.

3 Result and discussion

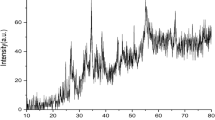

XRD graph of ZnO thin film layer has been indicated in Fig. 2 from 20° to 80°. It can be seen two peaks in that figure: one of them and severe one is (201) peak, other and weak one is (002) peak. These peaks have implied that ZnO thin film layer was obtained successfully by the ALD technique. XRD peaks also referred to the hexagonal structure of the ZnO [30].

Surface and cross-section images of the device were taken to investigate surface morphology properties of the device using SEM. These images have been given in Fig. 3a, b for surface of the ZnO thin film and cross-section of the Au/ZnO/n-Si, respectively. Figure 3a has pointed out that ZnO thin film, which has smooth and homogenous surface, has been obtained successfully by ALD technique. Figure 3b has showed that device was composed also successfully on Si wafer. The surface morphology of the ZnO thin film has revealed that ALD technique is promising technique to deposit good films on a substrate [31, 32].

The I–V characteristics of Au/ZnO/n-Si have indicated for changing temperature from 100 to 380 K for 20 K steps in Fig. 4 (inset figure shows 300 K I–V characteristics of the device). The device has good rectifying property at all temperatures, and this indicates that the temperature increase or decrease do not change rectifying properties of the device. This conclusion implied that this device can be used for wide temperature ranges [33, 34].

Barrier height and ideality factor were calculated by using thermionic emission theory. According to this theory, current (I) is given below equation:

in here, \({I_0}\) (saturation current) is intercept value of the linear portion of lnI–V plot at V = 0, and is given

In these equations, q is charge of the electron; n, k, T, are ideality factor of device, Boltzman’s constant and device temperature, respectively. A and A * are metallic contact area of the device and Richardson constant (A* = 112 A cm−2 K−2 for n-type Si), respectively. \({\Phi _b}\) is the barrier height at zero bias for device. If n and \({\Phi _b}\) is rearranged using Eqs. (1) and (2), they can be typed as follow:

and

n and \({\Phi _b}\) values for all temperature have been listed in Table 1. When n values have decreased from 4.34 at 100 K to 2.40 at 380 K with increasing temperature, \({\Phi _b}\) values increased from 0.39 at 100 K to 0.91 eV at 380 K. These change in n and \({\Phi _b}\) values have been shown in Fig. 5 as a graph. All n values are bigger than one, and it implied that there is no pure thermionic emission (TE) in this device. This difference can be attributed to interface states or barrier inhomogeneity in the interface of the device [35, 36]. At the same time, increasing temperature has increased the saturation current values of the device. Saturation current values have also been listed in Table 1. This device can be used depending on temperature for different applications in technology [37].

Figure 5 shows how barrier height and ideality factor changed with the changing temperature. While the barrier height values have increased with increasing temperature, the ideality factor values have decreased. These changes clearly have concluded that there is no pure TE current in the device [38]. The charge carriers have no enough energy to cross the high barrier height in the lower temperature, but current transport is provided by lower parts of barrier height [39]. If barrier height is not homogeous, this case usually happens, and this causes to increase in the barrier height and decrease in the ideality factors with increasing temperature [40,41,42].

To better understand currrent mechanism, the nkT versus kT plot of Au/ZnO/n-Si device has been plotted in Fig. 6. If a diode is ideal, pure thermionic emission happens, and its ideality factor values do not change with increasing temperature as can be seen in Fig. 6. In this device, nkT versus kT plot have showed almost parallel line to the ideal device but not exactly parallel. It means that associated with TE, other current transport mechanism such as thermionic fileld emission (TFE) has also effectiveness in this device [42]. In addition, this conclusion also have referred to barrier inhomogenity in the interface of the device [38].

The ln(I 0 /T 2) versus (kT)−1 or (nkT)−1 plots of Au/ZnO/n-Si device have been given in Fig. 7. The value of Richardson constant for n-type Si is 112 A/(cm K)−1, but here, Richardson constant values (can be seen on Fig. 7) are very small from the value of 112 A/(cm K)−1. This result showed that there is some barrier inhomogeneity in the interface [42].

The other way to determine the diode parameters, Cheung’s functions can be used for this case. Current expression with considering series resistance of device could be calculated below equation [43]:

where, IR s voltage dropping which is reasoned by series resistance of the device. This series resistance can be calculated using following expression:

where H(I) can be arranged as follow:

Equation (6) is a straight line equation, and if dV/d(lnI) versus I are plotted, this graph should be linear. According to the Cheung’s functions, using this linear plotting, R s and n values can be obtained slope and intercept of the plots, respectively. Also, expression (8) is again a straight line equation. If obtaining ideality factor is written in this equation to its place, same plotting way, barrier height and series resistance can be calculated. In this plotting, y-axis intercept is equal to \(n{\Phi _b}\) and slope of this plot also provides a different obtaining of R s which could be controlled the accuracy of Cheung’s approximation [43].

The dV/d(lnI) versus I and H(I) versus I plots of device for different temperatures have been shown in Figs. 8 and 9, respectively. Although there is some deviations in dV/d(lnI) versus I plots of the device, these plots are good agreement and almost periodic with the changing temperature. H(I) versus I plots have showed very good periodicity with changing temperature. The calculated n, \({\Phi _b}\) and R s values have been given in Table 1. While n values are increasing, \({\Phi _b}\) values almost stay constant for the changing temperature. The difference in n and \({\Phi _b}\) values obtained from TE current theory can be attributed that TE theory and Cheung’s functions obtained different regions of I–V measurements [44]. R s values which were obtained dV/d(lnI) versus I and H(I) versus I plots were not so different from each other. These results have corrected consistency of Chung’s functions. At the same time, R s values for two calculations have decreased with increasing temperature because of increasing number of carriers [45].

As another method, Norde’s approximation can be used for calculating series resistance and barrier height of the device. Respect to this method, R s and \({\Phi _b}\) values are given as follow:

where \(\gamma\) is an integer (dimensionless) greater than n and I(V) is current which is acquired from the I–V curve. With aid of this equation, R s and \({\Phi _b}\) can be rearranged following relations:

here F(V 0) is the minimum point of F(V) and V 0 is the corresponding voltage and R s is with below equation

The F(V) versus V plots of Au/ZnO/n-Si device have been shown in Fig. 10 for the changing temperature from 100 to 380 K. Calculated \({\Phi _b}\) and R s values were listed in Table 1. While \({\Phi _b}\) values were increased with increasing temperature, R s values decreased. This decrease can be attributed to increasing carriers in the device with increasing temperature [46]. There are also differences \({\Phi _b}\) and R s values between obtained Norde’s method, TE theory and Cheung’s method. These differences can be attributed to that while Cheung’s method is applied non-linear region (high voltage), Norde’s method is performed all forward bias lnI–V plots [47].

The lnI–V plot which has a non-linearity part at high forward bias voltages shows a continuous of the interface state density (N ss ) in balance with semiconductor. The N ss values for Au/ZnO/n-Si device with changing temperature were calculated from the forward bias I–V by considering efficient barrier height (Φ e ), ideality factor n(V) which is depend on the voltage and R s . The Φ e can be written as following equation [48]:

Since the ideality factor of a diode become all time greater than one, it was suggested below formula by Card and Rhoderick [48].

where W d is depletion layer width and δ is the thickness of the insulator sheet at the interface. ε i and ε s are permittivity of interfacial layer and the semiconductor, respectively. Rearranges of Eq. (13), the N ss can be expressed as follow:

In addition, for n-type semiconductors, the energy of the N ss as regards the conductance band edge (E c ) at the semiconductor surface can be calculated as

where the IR s term is the voltage drop on the device. The energy density distribution profile of N ss with R s , which was obtained from the forward-bias I–V measurements, has been indicated in Fig. 11 for the changing temperature. It can be seen from Fig. 11 that N ss values has been affected by changing temperatures. In addition, relatively higher N ss values can be ascribed to the very thin (10 nm) ZnO interface layer [49, 50]. These results have also advised that the N ss values should be considered as distinguishing parameters for determining properties of the device [51].

4 Conclusion

Au/ZnO/n-Si device was composed by ALD technique as a thin layer ZnO film at the interface, and device was characterized with XRD, SEM and temperature dependent I–V measurements. XRD measurements showed that ZnO thin film layer has (002) and (201) orientation peaks which are referred to hexagonal structure of the ZnO layer. SEM images of the device showed that ZnO layer has smooth surface and, Au/ZnO/n-Si device was obtained successfully. Ideality factor and barrier height values were calculated using TE theory for various temperatures. While n values decreased with increasing temperature, \({\Phi _b}\) values increased. These changings at n and \({\Phi _b}\) values confirmed that device was not ideal diode and charge transport mechanism was not just TE. Also, these parameters and R s values were calculated using Chung’s and Norde’s methods. The increasing temperature caused generally decreasing R s values. N ss versus (E c –E ss ) plots have shown that N ss values increased with increasing temperatures. These results have implied that this device can be used for diodes applications in the wide range temperatures.

References

A.S. Dahlan, A. Tataroğlu, A.A. Al-Ghamdi, A.A. Al-Ghamdi, S. Bin-Omran, Y. Al-Turki, F. El-Tantawy, F. Yakuphanoglu, Photodiode and photocapacitor properties of Au/CdTe/p-Si/Al device. J. Alloys Compd. 646, 1151–1156 (2015)

Güllü Ö, A. Türüt, Electrical analysis of organic dye-based MIS Schottky contacts. Microelectron. Eng. 87, 2482–2487 (2010)

Ö. Demircioglu, Ş. Karataş, N. Yıldırım, Ö.F. Bakkaloglu, A. Türüt, Temperature dependent current–voltage and capacitance–voltage characteristics of chromium Schottky contacts formed by electrodeposition technique on n-type Si. J. Alloys Compd. 509, 6433–6439 (2011)

H. Feng, W. Yang, JKO Sin, A low recovery loss reverse-conducting IGBT with metal/P-body Schottky junctions for hard-switching applications. ECS J. Solid State Sci. Technol. 5, Q61–Q67 (2016)

N. El-Atab, S. Alqatari, F.B. Oruc, T. Souier, M. Chiesa, A.K. Okyay, A. Nayfeh, Diode behavior in ultra-thin low temperature ALD grown zinc-oxide on silicon. AIP Adv. 3, 102119 (2013)

K.C. Pradel, W. Jevasuwan, J. Suwardy, Y. Bando, N. Fukata, Z.L. Wang, Solution derived p-ZnO/n-Si nanowire heterojunctions for photodetection. Chem. Phys. Lett. 658, 158–161 (2016)

A.B. Yadav, A. Pandey, D. Somvanshi, S. Jit, Sol-gel-based highly sensitive Pd/n-ZnO thin film/n-Si Schottky ultraviolet photodiodes. IEEE Trans. Electron Devices 62, 1879–1884 (2015)

O. Seok, M.-K. Han, Y.-C. Byun, J. Kim, H.-C. Shin, M.-W. Ha, High-voltage AlGaN/GaN Schottky barrier diodes on silicon using a post-process O2 treatment. Solid. State. Electron. 103, 49–53 (2015)

A. Turut, A. Karabulut, K. Ejderha, N. Bıyıklı, Capacitance–conductance–current–voltage characteristics of atomic layer deposited Au/Ti/Al2O3/n-GaAs MIS structures. Mater. Sci. Semicond. Process. 39, 400–407 (2015)

V.R. Reddy, V. Janardhanam, J.-W. Ju, H. Hong, C.-J. Choi, Electrical properties of Au/Bi0.5Na0.5TiO3-BaTiO3/n-GaN metal–insulator–semiconductor (MIS) structure. Semicond. Sci. Technol. 29, 75001 (2014)

A. Kumar, S. Mondal, S.G. Kumar, KSR Koteswara Rao, High performance sol–gel spin-coated titanium dioxide dielectric based MOS structures. Mater. Sci. Semicond. Process. 40, 77–83 (2015)

H.G. Çetinkaya, H. Tecimer, H. Uslu, Ş Altındal, Photovoltaic characteristics of Au/PVA (Bi-doped)/n-Si Schottky barrier diodes (SBDs) at various temperatures. Curr. Appl. Phys. 13, 1150–1156 (2013)

M. Ali Yıldırım, B. Güzeldir, A. Ateş, M. Sağlam, Temperature dependent current–voltage characteristics of the Zn/ZnO/n-Si/Au–Sb structure with ZnO interface layer grown on n-Si substrate by SILAR method. Microelectron. Eng. 88, 3075–3079 (2011)

S. Ameen, D.-R. Park, M. Shaheer Akhtar, H.S. Shin, Lotus-leaf like ZnO nanostructures based electrode for the fabrication of ethyl acetate chemical sensor. Mater. Lett. 164, 562–566 (2016)

F.Z. Bedia, A. Bedia, B. Benyoucef, S. Hamzaoui, Electrical characterization of n-ZnO/p-Si heterojunction prepared by spray pyrolysis technique. Phys. Procedia 55, 61–67 (2014)

S.K. Singh, P. Hazra, S. Tripathi, P. Chakrabarti, Performance analysis of RF-sputtered ZnO/Si heterojunction UV photodetectors with high photo-responsivity. Superlattices Microstruct. 91, 62–69 (2016)

S.B. Bashar, M. Suja, M. Morshed, F. Gao, J. Liu, An Sb-doped p-type ZnO nanowire based random laser diode. Nanotechnology 27, 65204 (2016)

T. Marimuthu, N. Anandhan, R. Thangamuthu, M. Mummoorthi, G. Ravi, Synthesis of ZnO nanowire arrays on ZnOTiO2 mixed oxide seed layer for dye sensitized solar cell applications. J. Alloys Compd. 677, 211–218 (2016)

T. Chen, M.-H. Wang, H.-P. Zhang, Z.-Y. Zhao, T.-T. Liu, Novel synthesis of monodisperse ZnO-based core/shell ceramic powders and applications in low-voltage varistors. Mater. Des. 96, 329–334 (2016)

Z. Ye, T. Wang, S. Wu, X. Ji, Q. Zhang, Na-doped ZnO nanorods fabricated by chemical vapor deposition and their optoelectrical properties. J. Alloys Compd. 690, 189–194 (2017)

M. Yilmaz, Aydoğan Ş, The effect of Mn incorporation on the structural, morphological, optical, and electrical features of nanocrystalline ZnO thin films prepared by chemical spray pyrolysis technique. Metall. Mater. Trans. A 46, 2726–2735 (2015)

A.B. Kashyout, HMA Soliman, H. Shokry Hassan, A.M. Abousehly, A.B. Kashyout, HMA Soliman, H. Shokry Hassan, A.M. Abousehly, Fabrication of ZnO and ZnO:Sb nanoparticles for gas sensor applications. J. Nanomater. 2010, 1–8 (2010)

S.-R. Jian, Y.-H. Lee, Nanoindentation-induced interfacial fracture of ZnO thin films deposited on Si(111) substrates by atomic layer deposition. J. Alloys Compd. 587, 313–317 (2014)

İ. Orak The performances photodiode and diode of ZnO thin film by atomic layer deposition technique. Solid State Commun. 247, 17–22 (2016)

I. Orak, A. Kocyigit, A. Turut, The surface morphology properties and respond illumination impact of ZnO/n-Si photodiode by prepared atomic layer deposition technique. J. Alloys Compd. 691, 873–879 (2017)

M.M. Bülbül, S. Bengi, I. Dökme, S. Altındal, T. Tunç, Temperature dependent capacitance and conductance-voltage characteristics of Au/polyvinyl alcohol(Co,Zn)/n-Si Schottky diodes. J. Appl. Phys. 108, 34517 (2010)

A. Kocyigit, I. Orak, Ş Aydoğan, Z. Çaldıran, A. Turut, Temperature-dependent C-V characteristics of Au/ZnO/n-Si device obtained by atomic layer deposition technique. J. Mater. Sci. 28, 5880–5886 (2017)

W. Mtangi, F.D. Auret, C. Nyamhere, P.J. Janse van Rensburg, M.D.A. Chawanda, Analysis of temperature dependent measurements on Pd/ZnO Schottky barrier diodes and the determination of the Richardson constant. Phys. B 404, 1092–1096 (2009)

N. Khare, M.Z. Ansari, RLZ Hoye, D.C. Iza, J.L. MacManus-Driscoll, Elucidation of barrier homogeneity in ZnO/P3HT:PCBM junctions through temperature dependent I–V characteristics. J. Phys. D 49, 275302 (2016)

H. Fan, X. Jia, Selective detection of acetone and gasoline by temperature modulation in zinc oxide nanosheets sensors. Solid State Ionics 192, 688–692 (2011)

S.-Y. Pung, K.-L. Choy, X. Hou, C. Shan, Preferential growth of ZnO thin films by the atomic layer deposition technique. Nanotechnology 19, 435609 (2008)

Y.-C. Cheng, K.-Y. Yuan, M.-J. Chen, ZnO thin films prepared by atomic layer deposition at various temperatures from 100 to 180 °C with three-pulsed precursors in every growth cycle. J. Alloys Compd. 685, 391–394 (2016)

D. Dhruv, Z. Joshi, S. Kansara, D.D. Pandya, J.H. Markna, K. Asokan, P.S. Solanki, D.G. Kuberkar, N.A. Shah, Temperature-dependent I–V and C–V characteristics of chemically-grown Y0.95Ca0.05MnO3/Si thin films. Mater. Res. Express 3, 36402 (2016)

E. Marıl, A. Kaya, H.G. Çetinkaya, S. Koçyiğit, Ş Altındal, On the temperature dependent forward bias current–voltage (I–V) characteristics in Au/2% graphene–cobalt doped (Ca3Co4Ga0.001Ox)/n-Si structure. Mater. Sci. Semicond. Process. 39, 332–338 (2015)

N. Shiwakoti, A. Bobby, K. Asokan, B. Antony, Temperature dependent dielectric studies of Ni/n-GaP Schottky diodes by capacitance and conductance measurements. Mater. Sci. Semicond. Process. 42, 378–382 (2016)

M.A. Mayimele, JPJ van Rensburg, F.D. Auret, M. Diale, Analysis of temperature-dependant current–voltage characteristics and extraction of series resistance in Pd/ZnO Schottky barrier diodes. Phys. B 480, 58–62 (2016)

Y.J. Park, H. Song, K.B. Ko, B.D. Ryu, T.V. Cuong, C.-H. Hong, Y.J. Park, H. Song, K.B. Ko, B.D. Ryu, T.V. Cuong, C.-H. Hong, Nanostructural effect of ZnO on light extraction efficiency of near-ultraviolet light-emitting diodes. J. Nanomater. 2016, 1–6 (2016)

I. Jyothi, V. Janardhanam, H. Hong, C.-J. Choi, Current–voltage and capacitance–voltage characteristics of Al Schottky contacts to strained Si-on-insulator in the wide temperature range. Mater. Sci. Semicond. Process. 39, 390–399 (2015)

D.S. Reddy, MSP Reddy, V.R. Reddy, Analysis of current-voltage-temperature (I-V-T) and of Pt/Ti Schottky contacts on n-type InP. J. Optoelectron. Adv. Mater. 5, 448–454 (2011)

S. Kumar, Y.S. Katharria, S. Kumar, D. Kanjilal, Temperature-dependent barrier characteristics of swift heavy ion irradiated Au/n-Si Schottky structure. J. Appl. Phys. 100, 113723 (2006)

F.E. Cimilli, H. Efeoğlu, M. Sağlam, A. Türüt, Temperature-dependent current–voltage and capacitance–voltage characteristics of the Ag/n-InP/In Schottky diodes. J. Mater. Sci. 20, 105–112 (2009)

A. Guzel, S. Duman, N. Yildirim, A. Turut, Electronic transport of an Ni/n-GaAs diode analysed over a wide temperature range. J. Electron. Mater. 45, 2808–2814 (2016)

S.K. Cheung, N.W. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85 (1986)

Ş Karataş, Effect of series resistance on the electrical characteristics and interface state energy distributions of Sn/p-Si (MS) Schottky diodes. Microelectron. Eng. 87, 1935–1940 (2010)

K. Ejderha, S. Duman, C. Nuhoglu, F. Urhan, A. Turut, Effect of temperature on the current (capacitance and conductance)-voltage characteristics of Ti/n-GaAs diode. J. Appl. Phys. 116, 234503 (2014)

A. Battal, D. Tatar, A. Kocyigit, B. Duzgun, Effect of substrate temperature on some properties doubly doped tin oxide thin films deposited by using spray pyrolysis. Mater. Focus 4, 445–456 (2015)

Ş Karataş, N. Yildirim, A. Türüt, Electrical properties and interface state energy distributions of Cr/n-Si Schottky barrier diode. Superlattices Microstruct. 64, 483–494 (2013)

H.C. Card, E.H. Rhoderick, Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J. Phys. D 4, 319 (1971)

Z. Rebaoui, W. Bachir Bouiajra, M. Abboun Abid, A. Saidane, D. Jammel, M. Henini, J.F. Felix, SiC polytypes and doping nature effects on electrical properties of ZnO-SiC Schottky diodes. Microelectron. Eng. 171, 11–19 (2017)

Ş. Aydoğan, M.L. Grilli, M. Yilmaz, Z. Çaldiran, H. Kaçuş, A facile growth of spray based ZnO films and device performance investigation for Schottky diodes: determination of interface state density distribution. J. Alloys Compd. 708, 55–66 (2017)

Ç. Bilkan, A. Gümüş, Ş Altındal, The source of negative capacitance and anomalous peak in the forward bias capacitance-voltage in Cr/p-si Schottky barrier diodes (SBDs). Mater. Sci. Semicond. Process. 39, 484–491 (2015)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kocyigit, A., Orak, I., Çaldıran, Z. et al. Current–voltage characteristics of Au/ZnO/n-Si device in a wide range temperature. J Mater Sci: Mater Electron 28, 17177–17184 (2017). https://doi.org/10.1007/s10854-017-7646-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-017-7646-3