Abstract

Herein, we investigate the performance of thin film transistors based on polycrystalline silicon nanowires using the complementary metal–oxide–semiconductor spacer technique. A drain current model was developed based on the Poisson equation whose charge density includes the acceptor traps. The density of states (DOS) distribution was characterized by two exponentials modeling the tail and the deep states within the gap. A comprehensive analysis was conducted on the impact of the DOS parameters on the transfer characteristics. The results show that the deep states affect the current behavior in the subthreshold region, while the tail states affect the current above the threshold. For comparison, the model was fitted with the experimental data. The deep state density was high, which provides qualitative insight into the structure of polycrystalline silicon nanowires (poly-SiNWs). The results are in good agreement with the study of the conduction mechanism and the measurement of DOS for these nanowires.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Polycrystalline silicon nanowires (poly-SiNWs) have attracted considerable attention in recent decades as an active element for the new generation of electronic devices, such as thin film transistors (TFT) [1,2,3] and biochemical sensors [4, 5], owing to their sensitivity to chemical and biological species. The electrical properties of poly-SiNWs and their realization technique have rendered these nanowires potentially promising candidates for overcoming several obstacles, such as the short-channel effects encountered in fin field-effect transistors (FinFETs) [6]. Different techniques have been implemented to realize poly-SiNWs [7, 8], and the top-down approach affords an important advantage due to its compatibility with the concept of miniaturization. Planar technology is commonly used in the very large-scale industrial applications to produce reliable and low-cost devices. More precisely, for low-temperature technologies, polycrystalline silicon is a widely used material.

Although the operation of devices based on poly-SiNWs has been demonstrated [1, 9, 10] and their performance has been encouraging, they are still being researched to better understand and identify the properties of poly-SiNWs for integration in commercial devices. Furthermore, the electrical properties of poly-SiNWs are closely linked to their production processes, their diameter [11], and their architecture. More precisely, their crystalline quality plays a decisive role in the device performance. Thus, poly-SiNWs with good crystalline quality will afford high-performance devices such as transistors with a high ION/IOFF ratio, reduced threshold voltage, and small subthreshold swing slope [12]. In contrast, a low or even highly disordered crystalline quality is advantageous for sensors owing to the interaction of the electrical defects on the surface with the surrounding chemical species [13].

The performance/crystalline quality duality of poly-SiNWs needs to be analyzed to understand and predict their behaviors. Since physical characterizations are a powerful tool for understanding the device properties, analytical and numerical studies have been performed to build models to explicitly determine the electrical properties. Several approaches have been employed to model the electrical performance of poly-SiNW-based devices with different architectures, including back gate, dual gate [14], and gate all around [15, 16], by analyzing the impact of the number and position of grain boundaries present in the nanowire structure. For poly-SiNWs with a high density of defects, adopting a model that is described by only grain boundaries is not convenient. Indeed, studies on the conduction mechanism [17] for poly-SiNWs with diameters less than 50 nm have shown that carrier transport occurs via variable-range hopping (VRH). This verifies the disordered nature for poly-SiNWs and rules out the model based on grains separated by grain boundaries.

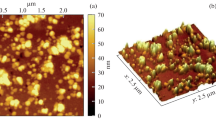

In this study, we investigate the performance of TFTs based on poly-SiNWs with 30 nm diameters that were realized using the complementary metal–oxide–semiconductor (CMOS) spacer technique [7]. First, a model of the drain current was developed based on the Poisson’s equation. The charge of acceptor traps to the density of states (DOS) was represented by two exponentials describing the deep and band tail states. Thereafter, the impact of the DOS parameters is detailed and discussed to elucidate the performance of poly-SiNWs. Finally, the model was fitted with the experimental transfer characteristic data, justified in agreement with our study on the conduction mechanism and DOS measurements for TFTs based on poly-SiNWs in order to provide the DOS within the gap.

2 Device modeling

2.1 Surface potential model

Our previous study [17] on the electrical properties of poly-SiNWs obtained using the spacer method revealed that the conduction mechanism operates via VRH when the nanowire diameter is around 50 nm. This is explained by the high density of electric traps that are afforded by the disordered structure of the lower part of the un-doped poly-Si layer, from which these nanowires are obtained. Therefore, we can consider the DOS model [18] to express the distribution of these defects within the gap. The density of two exponential acceptor and donor tail states and two exponential deep acceptor and donor states can be expressed as follows:

Here, gTA(E) and gTD(E) are two exponential densities that correspond to the densities of the acceptor and donor states, respectively, in the tape tails. Additionally, gDA(E) and gDD(E) are two exponential densities corresponding to the densities of the deep acceptor and donor states, respectively. E is the trap energy, EC is the conduction band energy, and EV is the valence band energy. For tail distributions, DOS is described by the conduction and valence band edge intercept densities (NTA and NTD, respectively) and the characteristic decay energies (WTA and WTD, respectively). For deep distributions, DOS is described by the conduction and valence band edge intercept densities (NDA and NDD, respectively) and the characteristic decay energies (WDA and WDD, respectively).

Figure 1 shows the cross-section of the metal–insulator–semiconductor structure and the corresponding energy diagram. For simplicity, we only consider the free electrons and the charge of the acceptor traps. The one-dimensional Poisson equation is

Here, n is the concentration of free electrons and nT is the density of ionized acceptor traps:

where \(N_{0} = N_{C} \exp \left( { - \frac{{E_{F0} }}{{{\text{kT}}}}} \right)\) is the electron concentration under equilibrium conditions, and NC is the effective DOS in the conduction band. fA(E) is the probability function of occupation of an acceptor trap by an electron:

Here, EF0 denotes the Fermi level under equilibrium conditions. Based on the band gap diagram, the number of ionized acceptor traps at steady state is

Here,

Using the property \(\partial \left( {\partial \psi /\partial x} \right)^{2} = 2\left( {\partial^{2} \psi /\partial x^{2} } \right)\partial \psi\), the electric field ξ along x is expressed according to (5) as

Substituting (6), (10), and (12) in (13) and integrating from ψTsc(x = Tsc) to ψs(x = 0), the expression of the electric field at the SiO2/poly-SiNW interface (x = 0) is

Here,

For a range of parameters WTA, WDA, NTA, and NDA, which we will discuss later, only the terms N2 and N3 subsist in the expression of ξs. Neglecting the potential ψTsc, the final expression of ξs becomes

Here,

Considering the Vox potential in the insulator and using Gauss’s law at the SiO2/poly-SiNW interface, the gate voltage is

where VFB is the flat band voltage defined by \(V_{{{\text{FB}}}} = q\chi - q\varphi_{m}\). Thus, ψs becomes

Here, Cox is the oxide capacity per unit area. An analytical expression of ψs cannot be clearly obtained from (17). However, depending on the choice of the parameters N2 and N3, one of the two parameters dominates the expression of ξs. Then, ψs becomes

Here,

From (18), the numerical solution ψs for a given VGS value shows that the potential ψs < < VGS when VGS > VFB, yielding the following final expression of ψs

2.2 Drain current model

The free electron concentration, according to the charge sheet model, over the entire depth of the nanowire is as follows:

According to the MOSFET drain current [22], its expression is

where W and L are the width and length of the channel, respectively, µ0 is the mobility of electrons, and ψ(z) is the potential along the channel. The drain current is

The subthreshold slope is

3 Results and discussion

To validate our model, a technology computer-aided design (TCAD) simulation was performed using Silvaco commercial software [19]. Figure 2 displays a three-dimensional (3D) view of the simulated device, and Table 1 summarizes the DOS parameters and the chosen dimensions, similar to the experimental device reported in Ref. [20]. Herein, we focus on the effect of DOS parameters (NTA, WTA, NDA, WDA) on the transfer characteristics. Thus, only one parameter is varied while the others are kept fixed. For reference, IDS(VGS) curves include transfer characteristics fitted with experimental data from Ref. [20].

Figure 3 displays the transfer characteristics of the model in comparison to the simulation with NTA ranging from 1020 to 1022 cm−3 eV−1. The model and simulation results agree well, demonstrating the validity of our model. When NTA increases, the current above the threshold decreases and the threshold voltage and the subthreshold slope are very weakly affected. Based on (24), only the parameters of the band tail states affect the current, justifying the weak variation of the subthreshold slope according to (25). In contrast, the decrease in the drain current above the threshold is explained by the increase in N02 with NTA. The NTA effect studied in this context agrees with the simulations of Gao et al. [21], highlighting the band tail effect on the drain current when the gate voltage exceeds the threshold voltage. Additionally, from (18), \(\partial {\psi }_{s}/\partial {V}_{GS}\) exhibits a slope independent of NTA, leading to a less pronounced increase in the surface potential when the device operates above the threshold. However, the experimental characteristics exhibit a high threshold voltage and sub-threshold slope. Clearly, the consideration of NTA alone does not afford a DOS representation that brings the model closer to the experimental characteristics.

Figure 4 shows the transfer characteristics for WTA varying from 0.04 to 0.08 eV while the other parameters are kept fixed. Obviously, the increase in WTA degrades the device performance as the threshold voltage and subthreshold slope increase and the current above the threshold decreases. Below the threshold, WTA significantly affects the subthreshold slope, which increases according to (25), and the drain current decreases with N02 above the threshold. Given the WTA range considered, only the band tail states describe the total density of the acceptor traps. Compared to NTA, the effect of WTA is clearly seen on the transfer characteristics as the dominant factor of the slopes below and above the threshold.

Figure 5 shows the transfer characteristics for WDA varying from 0.3 to 1.1 eV, while the other parameters are kept fixed. In this case, the expression for the current depends on N2 and N3, and an explicit expression for the drain current cannot be formulated with these two quantities together. Indeed, as mentioned earlier, one of the two parameters subsists in the expression of the current. This fact is illustrated in Fig. 6, which displays the variation in N2 and N3 as a function of ψ, where the intersection potential ψi corresponds to N2(ψi) = N3(ψi) and is expressed by:

Thus, based on the value of ψi, we define two currents Ideep and Itail: Above ψi (region above the threshold), the drain current is described by Itail, which depends on N2; N2 is kept fixed in this case. Below ψi (below the threshold), the drain current is described by Ideep, which depends on N3. Figure 7 exhibits the Ideep current as a function of VGS for a limit value of 10−10 A. From the expression of Ideep, the transfer characteristics can be differentiated into two regions with a new threshold voltage and a new subthreshold slope depending on WDA. However, in the region below the threshold and for WDA ≥ 0.7 eV, Ideep is drastically weak to the point of being practically immeasurable. Thus, the current is only present above the threshold of Ideep, which appears in the subthreshold region of the device and whose slope varies very weakly with WDA. This explains the small variation in the slope under the device threshold with increasing WDA. The expression of the potential according to (18) shows that its value is negative even when VGS > VFB. For the region of the channel near the SiO2/poly-SiNW interface, the band diagram will exhibit high curvature of the conduction band that is manifested by a strong decrease in the concentration of free electrons. In other words, the region near the SiO2/poly-SiNW interface is deserted for a positive VGS. On the other hand, a negative surface potential will shift the probability of the occupation function fA(E) back toward energies below EF0, which will drastically reduce the probability that an acceptor trap will be ionized. Hence, the device performance degrades in the region below the threshold.

Figure 8 shows the transfer characteristics for NDA ranging from 1019 to 1021 cm−3 eV−1. Below an NDA value between 1020 and 1021 cm−3 eV−1, the drain current is described by Itail and Ideep, whose subthreshold slope does not vary with NDA (the part of the very weak currents is not shown in the figure). Above a certain value of NDA, only the deep states influence the drain current, whose decrease above the threshold is due to the increase of N03 with NDA. Figure 9 displays a fit of the model with the experimental data. Compared to the DOS distribution of polycrystalline silicon referenced in the literature [18], the DOS studied herein displays a high density of deep states. As is known, deep states are afforded by the dangling bonds present in disordered silicon, such as microcrystalline or amorphous silicon. Moreover, our previous study [17] clearly showed that the increase in deep states exhaustively explains the conduction mechanism via VRH for poly-SiNWs with small diameters and presents clear insight into their structure. Moreover, the DOS measurements of Le Borgne et al. [14] confirm our results, showing a high density of acceptor states for the TFT back gate based on poly-SiNWs realized by the spacer method.

Transfer characteristics fitted with experimental data [20] for NTA = 1021 cm−3 eV−1; WTA = 0.06 eV; NDA = 2.1020 cm−3 eV−1; WDA = 0.1 eV

In addition to the performance analysis of poly-SiNW TFTs exhibiting a high defect density, the analytical drain current model developed in this work has an interesting advantage. The explanation for all acceptor DOS parameters in the formulation of the model affords a good understanding of the impact of each parameter on the device behavior. Let us recall, among other things, the expression of the ionized acceptor trap density as a function of the potential, the involvement of each parameter, and its effect on operating below or above the threshold regions via the expressions of the densities N02 and N03.

In the case of FETs based on poly-SiNWs, the literature often mentions simulation studies [23,24,25] and shows similar effects of the variation in the DOS on the performance without presenting an analytical formulation. Hence, the importance of our model is that it can be adopted as a reference to develop other models intended for other devices, such as biochemical sensors based on poly-SiNWs whose operation is governed by the interaction of chemical species surrounding the defects present on the surface of the nanowires [26]. Note that although our model concerns the case of an architecture in which the gate modulates the channel on a single face, it can be extended to other architectures such as the double gate or the gate-all-around.

4 Conclusion

We investigated the performance of poly-SiNW TFTs fabricated using the spacer method by developing an analytical model of the drain current, explicitly showing the DOS parameters described by two exponentials. The impact of these parameters on the transfer characteristics demonstrated that the deep states significantly affect the subthreshold region while the tail states affect the region above the threshold. The fit of the model with the experimental data revealed a higher density of deep states than that for polysilicon, which provides extensive insight into the distribution of acceptor traps in the gap, agreeing well with our previous studies on the conduction mechanism and DOS measurement for poly-SiNWs. On the other hand, the explanation of the DOS parameters in the model of the drain current, in the particular case of TFTs based on poly-SiNWs, presents an interesting advantage for the analytical study of the performance of these devices. This supports the proposal of this model as a reference for the study and development of other models for other devices based on poly-SiNWs.

Data availability

Enquiries about data availability should be directed to the authors.

References

Liu, T.-Y., Pan, F.-M., Sheu, J.-T.: Characteristics of gate-all-around junctionless polysilicon nanowire transistors with twin 20-nm gates. IEEE J. Electron Dev. Soc. (2015). https://doi.org/10.1109/JEDS.2015.2441736

Xu, M., Wang, J., Xue, Z., Wang, J., Feng, P., Yu, L., Xu, J., Shi, Y., Chen, K., P. Roca I Cabarrocas,: High performance transparent in-plane silicon nanowire Fin-TFTs via a robust nano-droplet-scanning crystallization dynamics. Nanoscale (2017). https://doi.org/10.1039/C7NR02825C

Chen, Y.-H., Ma, W.C.-Y., Chao, T.-S.: High-performance poly-Si TFT with ultra-thin channel film and gate oxide for low-power application. Semicond. Sci. Technol. (2015). https://doi.org/10.1088/0268-1242/30/10/105017

Tang, S., Yan, J., Zhang, J., Wei, S., Zhang, Q., Li, J., Fang, M., Zhang, S., Xiong, E., Wang, Y., Yang, J., Zhang, Z., Wei, Q., Yin, H., Wang, W., Tu, H.: Fabrication of low cost and low temperature poly-silicon nanowire sensor arrays for monolithic three-dimensional integrated circuits applications. Nanomaterials (2020). https://doi.org/10.3390/nano10122488

Yen, L.-C., Pan, T.-M., Lee, C.-H., Chao, T.-S.: Label-free and real-time detection of ferritin using a horn-like polycrystalline-silicon nanowire field-effect transistor biosensor. Sens. Actuators B Chem. (2016). https://doi.org/10.1016/j.snb.2016.02.095

Gill, A., Madhu, C., Kaur, P.: Investigation of short channel effects in Bulk MOSFET and SOI FinFET at 20nm node technology. IEEE INDICON (2015). https://doi.org/10.1109/INDICON.2015.7443263

Demami, F., Pichon, L., Rogel, R., Salaün, A.C.: Fabrication of polycrystalline silicon nanowires using conventional UV lithography. IOP Conf. Ser. Mater. Sci. Eng. (2009). https://doi.org/10.1088/1757-899X/6/1/012014

Im, M., Han, J.-W., Lee, H., Yu, L.-E., Kim, S., Kim, C.-H., Jeon, S.C., Kim, K.H., Lee, G.S., Oh, J.S., Park, Y.C., Lee, H.M., Choi, Y.-K.: Multiple-gate CMOS thin-film transistor with polysilicon nanowire. IEEE Electron Device Lett. (2008). https://doi.org/10.1109/LED.2007.911982

Oda, M., Sakuma, K., Kamimuta, Y., Saitoh, M.: Carrier transport analysis of high-performance poly-Si Nanowire transistor fabricated by advanced SPC with record-high electron mobility. IEEE IEDM (2015). https://doi.org/10.1109/IEDM.2015.7409637

Hsu, H., Liu, T., Chan, L., Lin, C., Huang, T., Lin, H.: Fabrication and characterization of multiple-gated Poly-Si nanowire thin-film transistors and impacts of multiple-gate structures on device fluctuations. IEEE Trans. Electron Devices (2008). https://doi.org/10.1109/TED.2008.2005161

Demami, F.: Synthèse de nanofils de silicium par la méthode des espaceurs pour dispositifs électroniques. In : Ph Dissertation, Université de Rennes1, France (2011)

Chang, T.-C., Chang, C.-Y., Chen, C.-S., Tu, C.-H., Liu, P.-T., Zan, H.-W., Tai, Y.-H.: High-performance polycrystalline silicon thin-film transistor with multiple nanowire channels and lightly doped drain structure. Appl. Phys. Lett. (2004). https://doi.org/10.1063/1.1745104

Pichon, L., Salaün, A.-C., Wenga, G., Rogel, R., Jacques, E.: Ammonia sensors based on suspended silicon nanowires. Procedia Eng. (2014). https://doi.org/10.1016/j.proeng.2014.11.329

Le Borgne, B., Salaün, A.-C., Pichon, L.: Electrical properties of self-aligned gate-all-around polycrystalline silicon nanowires field-effect transistors. Microelectron. Eng. (2016). https://doi.org/10.1016/j.mee.2015.11.001

Kim, J., Oh, H., Lee, J., Baek, C.-K., Meyyappan, M., Lee, J.-S.: Three-dimensional simulation of threshold voltage variations due to an oblique single grain boundary in sub-40 nm polysilicon nanowire FETs. Semicond. Sci. Technol. (2015). https://doi.org/10.1088/0268-1242/30/8/085015

Oh, H., Kim, J., Lee, J., Rim, T., Baek, C.-K., Lee, J.-S.: Effects of single grain boundary and random interface traps on electrical variations of sub-30 nm polysilicon nanowire structures. Microelectron. Eng. (2016). https://doi.org/10.1016/j.mee.2015.09.018

Pichon, L., Jacques, E., Rogel, R., Salaun, A.C.-, Demami, F.: Variable range hopping conduction in N- and P-type in situ doped polycrystalline silicon nanowires. Semicond. Sci. Technol. (2013). https://doi.org/10.1088/0268-1242/28/2/025002

Chou, T.-K.A., Kanicki, J.: Two-dimensional numerical simulation of solid-phase-crystallized polysilicon thin-film transistor characteristics. Jpn. J. Appl. Phys (1999). https://doi.org/10.1143/JJAP.38.2251

ATLAS User’s Manual, Silvaco Software. 5.19.20.R (2013).

Lin, H.-C., Lee, M.-H., Su, C.-J., Huang, T.-Y., Lee, C.C., Yang, Y.-S.: A simple and low-cost method to fabricate TFTs with poly-Si nanowire channel. IEEE Electron Device Lett. (2005). https://doi.org/10.1109/LED.2005.853669

Gao, H.-X., Hu, R., Yang, Y.-T.: Modeling of polycrystalline ZnO thin-film transistors with a consideration of the deep and tail states. Chin. Phys. B (2011). https://doi.org/10.1088/1674-1056/20/11/116803

Arora, N.: MOSFET Modeling for VLSI Simulation: Theory and Practice. World Scientific, Singapore (2007)

Amit, I., Englander, D., Horvitz, D., Sasson, Y., Rosenwaks, Y.: Density and energy distribution of interface states in the grain boundaries of polysilicon nanowire. Nano Lett. (2014). https://doi.org/10.1021/nl5024468

Salaun, A., Le Borgne, B., Pichon, L.: Dual-gate and gate-all-around polycrystalline silicon nanowires field effect transistors: simulation and characterization. ECS Trans. (2018). https://doi.org/10.1149/08611.0079ecst

Siddique, A.B., Rahman, K.A., Alam, M.N., Hasan, K., Hakim, M.M.A.: Physical understanding on the interface states and grain boundary defects of polysilicon nanowires. 10th ICECE (2018). https://doi.org/10.1109/ICECE.2018.8636707

Demami, F., Ni, L., Rogel, R., Salaun, A.C., Pichon, L.: Silicon nanowires based resistors as gas sensors. Sens. Actuators B Chem. (2012). https://doi.org/10.1016/j.snb.2011.04.083

Funding

The authors have not disclosed any funding.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing Interests

The authors have not disclosed any competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Demami, F. Polycrystalline silicon nanowire FET performance depending on density of states. J Comput Electron 22, 946–953 (2023). https://doi.org/10.1007/s10825-023-02034-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-023-02034-8